أدوات التحقق من صحة ما بعد السيليكون ليست فكرة جديدة ولكن هنا تطور. استخدام مضاهاة (ما قبل السيليكون) لاختيار هياكل مراقبة التصحيح للأداة في السيليكون. بول كننغهام (مدير عام ، Verification at Cadence) ، راؤول كامبوسانو (Silicon Catalyst ، رجل أعمال ، CTO سابق لشركة Synopsys) وأواصل سلسلتنا حول أفكار البحث. كما هو الحال دائما ، نرحب بالتعليقات.

![]()

الابتكار

اختيار هذا الشهر هو البنية التحتية للمحاكاة لتقييم تأكيدات الأجهزة للتحقق من صحة ما بعد السيليكون. تم تقديم الورقة في 2017 IEEE Transactions on VLSI. المؤلفون من جامعة ماك ماستر ، هاميلتون ، أونتاريو ، كندا

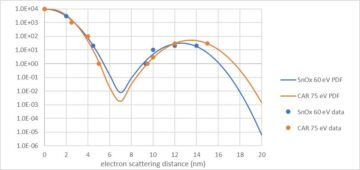

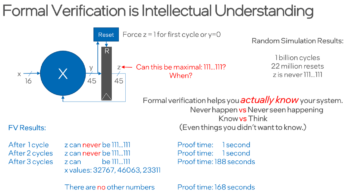

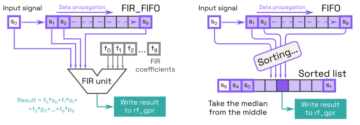

يميز المؤلفون بين الأخطاء المنطقية والكهربائية بعد السيليكون ويكرسون انتباههم في هذه الورقة للأخطاء الكهربائية ، التي يمكن اكتشافها من خلال تقلبات البت في النوبات. نهجهم هو تحديد مجموعة مثالية من التأكيدات في تحليل ما قبل السيليكون. ثم يقومون بتنفيذها في السيليكون لدعم تصحيح ما بعد السيليكون. يشبه تحليل ما قبل السيليكون حدوث خلل في تحليلات السلامة ، حيث يتم حقن الأعطال في التقلبات المقابلة للأخطاء الكهربائية ، كما يشيرون في الورقة. يقومون بإنشاء قائمة المرشحين للتأكيدات باستخدام التوكيد التوليفي ؛ يتمثل جوهر ابتكاراتهم في توفير طريقة لتصنيف هذه التأكيدات من خلال مدى فعالية كل منها في اكتشاف أخطاء متعددة.

يتم توليد المدخلات بشكل عشوائي ، حيث يتم تحليل العيوب المحقونة (تعامل على أنها عابرة) بالتسلسل. أنها تسمح بعدد محدد من دورات المستخدم للكشف عن كل خطأ. في مرحلة لاحقة ، يقومون بقياس الفعالية باستخدام طريقتين مختلفتين للتغطية. لتغطية التقليب ، يحسبون تأكيدًا إذا اكتشف خطأً محقونًا عند أي تقليب. في تغطية bit-flip ، يسجلون عدد التأكيدات من الأخطاء المكتشفة في عمليات التقليب المنفصلة. تستخدم هذه المقاييس ، جنبًا إلى جنب مع تقديرات المنطقة ، (بالتناوب) لتحديد التأكيدات المفضلة.

رأي بول

هذه الورقة تقترن بشكل جيد مع مدونة أغسطس 2020 عن الكشف السريع عن الأخطاء (QED). يعمل QED على تسريع اكتشاف الأخطاء الوظيفية بعد السيليكون ، حيث تركز هذه المدونة على اكتشاف الأخطاء الكهربائية بعد السيليكون. الورقة سهلة القراءة ، على الرغم من أنها تساعد على قراءة المرجع أولاً [23].

يصعب اكتشاف الأخطاء الكهربائية ، وحتى مع ذلك ، يصعب تكرارها والعثور على السبب المادي الأساسي. يقترح المؤلفون طريقة ، من خلال المنطق المضمن ، لاكتشاف متى تتسبب مثل هذه الأخطاء في قلب التقليب إلى قيمة غير صحيحة (فهم لا يحفرون أعمق من العثور على هذه التقلبات).

يعد قلب الورقة والمرجع المصاحب لها [23] طريقة متعددة الخطوات لإنشاء وتوليف منطق الكشف هذا. يبدأ بخصائص التعدين للتصميم كتأكيدات زمنية باستخدام أداة GoldMine. إنهم يرتبون التأكيدات بناءً على تقدير لقدرتها على اكتشاف تقلبات البتات ، وتقدير المنطقة / تكلفة الأسلاك المراد تنفيذها في السيليكون. يعتمد الترتيب على تشغيل العديد من عمليات محاكاة ما قبل السيليكون مع تأكيدات مرشح ، وحقن أخطاء قلب البتات وإحصاء التقلبات المكتشفة بالتأكيدات. في الورقة الأصلية التي استخدموا فيها المحاكاة المنطقية ، قاموا هنا بتسريع هذه المحاكاة عن طريق تعيين التصميم إلى لوحة Altera FPGA.

أحب الطريقة التي يجمعون بها العديد من الابتكارات في طريقة متماسكة لاكتشاف انعكاس بت ما بعد السيليكون: التنقيب عن التأكيد ، وتوليف التأكيد ، ووظيفة الترتيب الأنيقة لاختيار التأكيد. ومع ذلك ، يشير قسم النتائج بالورقة إلى أن اكتشاف تقلبات البت في n٪ من flip-flops يتطلب ما يقرب من n٪ زيادة في مساحة التصميم. يبدو هذا صعبًا بالنسبة للتطبيق التجاري ، خاصةً لأنه يساعد فقط في العثور على الأخطاء الكهربائية. يمكن للمرء أن يحقق نتيجة مماثلة عن طريق استنساخ المخروط المنطقي الذي يقود تقليبًا ، ثم مقارنة ناتج هذا المنطق المستنسخ بالمنطق الأصلي. يبدو أن هذا يولد مساحة مماثلة لطريقتهم ، في الحد من استنساخ التصميم بالكامل (أي 100٪ مساحة علوية) لاكتشاف التقلبات في 100٪ من التقلبات في التصميم.

رأي راؤول

الورقة قائمة بذاتها مع قدر لا بأس به من التفاصيل. أجرى المؤلفون تجارب لثلاث دوائر متتابعة من ISCAS (حوالي 3 ألف بوابة ، 12 FF). تقوم تجارب التحضير بحقن 2000 خطأ لكل فليب وباستخدام جميع التأكيدات الناتجة عن GoldMine. نظرًا للقدرة المحدودة لـ FPGA ، قام المؤلفون بتقسيم الدورات إلى 256 "جلسة" لدائرة واحدة. تظهر النتائج ، حتى مع 45 جلسة ، تسارعًا في التحليل على المحاكاة من 45 إلى 20 مرة (فقط ما يصل إلى 500 حقن خطأ لأن المحاكاة تصبح بطيئة جدًا ، 8 ساعة). الحد الأقصى من تغطية Flip-Flop التي يمكن تحقيقها هي 105٪ و 55٪ و 89٪ للدوائر الثلاث. عدد التأكيدات الملغومة يتحكم في التغطية.

يؤدي التشغيل مع التأكيدات المحددة (المقابلة لـ 5-50٪ مساحة علوية) وحقن 1-256 إلى تغطية بتات 2.2٪ -34٪. في معظم الأوقات ، ركض عامل منجم التأكيد لمدة 228 ساعة. الشيء الوحيد الذي أربكني هو بياناتهم الخاصة بأوقات التشغيل مقابل الأخطاء التي تم إدخالها. تبدو الزيادة معقولة (خطية) في المحاكاة. لكن في المحاكاة ، يقفز بشكل كبير ، من 0.045 ساعة إلى 5.4 ساعة لزيادة 2 إلى 8 حقن خطأ. أود المزيد من الشرح حول هذه النقطة.

هذه ورقة منهجية. يعجبني أنه يمكن استبدال كل خطوة بأداة تجارية. جنبا إلى جنب مع استخدام لوحة FPGA كبيرة (كمحاكي) مقاييس المنهجية. بالطبع من الصعب جدًا تسويق المنهجيات ، لكنه تطبيق جيد للتكنولوجيا الحالية!

وجهة نظري

طريقة استكشاف تقنية تحليل السلامة لتصحيح ما بعد السيليكون مثيرة للاهتمام. فكرة جديدة ، على الرغم من أنها تؤدي إلى نتيجة غير عملية إلى حد ما للتطبيق التجاري.

شارك هذا المنشور عبر: المصدر: https://semiwiki.com/artuable-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- الكل

- تحليل

- تطبيق

- المنطقة

- الكتاب

- قطعة

- المدونة

- مجلس

- علة

- البق

- إيقاع

- الطاقة الإنتاجية

- يو كاتش

- سبب

- تجاري

- استمر

- CTO

- البيانات

- تصميم

- التفاصيل

- كشف

- قيادة

- الطُرق الفعّالة

- ريادي

- تقديرات

- عادل

- الاسم الأول

- FPGA

- وظيفة

- البوابات و حواجز اللعب

- GM

- أجهزة التبخير

- هنا

- كيفية

- HTTPS

- فكرة

- IEEE

- القيمة الاسمية

- البنية التحتية

- الابتكار

- IT

- كبير

- قيادة

- محدود

- قائمة

- قياس

- المقاييس

- تعدين

- ورق

- اقترح

- بحث

- النتائج

- تشغيل

- السلامة

- مختار

- مسلسلات

- طقم

- محاكاة

- انقسم

- الدعم

- الوقت

- المعاملات

- تحريف

- جامعة

- قيمنا

- التحقق

- مقابل