تشتهر شركة Achronix بحلول FPGA عالية الأداء. في هذا المنشور، سأستكشف Speedster7T FPGA. تم تحسين عائلة FPGA هذه لأحمال العمل ذات النطاق الترددي العالي وتزيل اختناقات الأداء من خلال بنية مبتكرة. تم تصميم هذه العائلة بناءً على عملية FinFET مقاس 7 نانومتر من TSMC، وتوفر أداءً على مستوى ASIC مع الحفاظ على قابلية البرمجة الكاملة لـ FPGA. هناك الكثير لنتعلمه عن Speedster7T. لدى Achronix الآن مقطع فيديو متاح يجيب على الكثير من هذه الأسئلة. يوجد رابط لهذا الفيديو والمزيد في المستقبل، ولكن دعونا نرى أولاً ما يحدث عندما تأخذ Achronix Speedster7t FPGA لاختبار القيادة في المختبر.

تشتهر شركة Achronix بحلول FPGA عالية الأداء. في هذا المنشور، سأستكشف Speedster7T FPGA. تم تحسين عائلة FPGA هذه لأحمال العمل ذات النطاق الترددي العالي وتزيل اختناقات الأداء من خلال بنية مبتكرة. تم تصميم هذه العائلة بناءً على عملية FinFET مقاس 7 نانومتر من TSMC، وتوفر أداءً على مستوى ASIC مع الحفاظ على قابلية البرمجة الكاملة لـ FPGA. هناك الكثير لنتعلمه عن Speedster7T. لدى Achronix الآن مقطع فيديو متاح يجيب على الكثير من هذه الأسئلة. يوجد رابط لهذا الفيديو والمزيد في المستقبل، ولكن دعونا نرى أولاً ما يحدث عندما تأخذ Achronix Speedster7t FPGA لاختبار القيادة في المختبر.

يقدم ستيف مينسور، نائب الرئيس للمبيعات والتسويق في Achronix، الفيديو. يعمل ستيف مع Achronix منذ ما يقرب من عشر سنوات وقضى 21 عامًا في Altera قبل ذلك. من المؤكد أنه يعرف الكثير عن FPGAs – التصميم والتطبيق. يبدأ ستيف بتحديد بعض عناصر الهندسة المعمارية المبتكرة المذكورة سابقًا. هناك الكثير من القدرات المخصصة على متن Speedster7T. هذا يتضمن:

- 112 جيجابت في الثانية سيرديس

- شنومكسغ إيثرنت

- بكيي Gen5

- GDDR6 يعمل بسرعة 4 تيرابايت في الثانية

- DDR 4 يعمل بسرعة 3,200 ميجابت في الثانية

- معالج التعلم الآلي الخاص

- شبكة ثنائية الأبعاد على الشريحة (NoC)

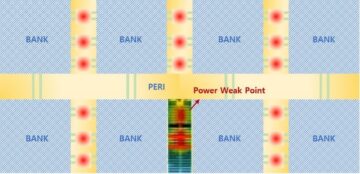

يوفر معالج التعلم الآلي الخاص الكثير من الوظائف، بما في ذلك النقطة العائمة والنقطة العائمة وعمليات الأعداد الصحيحة. تعد 2D NoC قدرة جديدة على الصناعة لـ FPGAs من Achronix. يمكن لـ NoC توجيه البيانات من أي من الواجهات عالية السرعة إلى نسيج FPGA الأساسي بسرعة 2 جيجا هرتز دون استهلاك أي من موارد منطق FPGA. تتيح لك كل هذه التقنيات الموجودة على اللوحة الوصول إلى أداء على مستوى ASIC في FPGA.

يقوم ستيف بعد ذلك بتسليم العرض التقديمي إلى كاتي بورسيل، مديرة هندسة التطبيقات في Achronix. تعمل كاتي مع Achronix منذ أربع سنوات. قبل ذلك كانت مصممة ASIC. كما أمضت وقتًا في Xilinx. كاتي هي التي أخذت Speedster7t FPGA لاختبار القيادة في المختبر، وهي بالتأكيد على مستوى التحدي.

تأخذ Katie المشاهد إلى معمل Achronix حيث يتم إجراء عرض Speedster7T - التحقق من الصحة والتوصيف. يُظهر العرض التوضيحي الذي قدمته كاتي الجهاز الذي يقوم بتشغيل حركة مرور إيثرنت 400 جيجا على بطاقة تسريع Achronix VectorPath. تبدأ كاتي بتلخيص العناصر الأساسية للعرض، والتي تشمل:

- واجهة خارجية 8 × 50 جيجا

- واجهة واحدة 400G في نظام إيثرنت الفرعي

- البيانات مقسمة إلى أربعة تدفقات منفصلة في 2D NoC

- تتم معالجة كل تيار بشكل مستقل

تقضي كاتي بعض الوقت في 2D NoC. وتشير إلى أن هذه القدرة تجعل التصميم أبسط وأسهل لإغلاق التوقيت. ظهرت NoC الفريدة ثنائية الأبعاد هذه عدة مرات أثناء العرض التوضيحي. يجدر البحث أكثر قليلاً لفهمه. قدمت Achronix سابقًا ندوة عبر الإنترنت حول هذه القدرة الفريدة مغطاة على SemiWiki تسمى 5 أسباب لماذا تتطلب بطاقة SmartNIC عالية الأداء والقابلة لإعادة التكوين رقم NoC ثنائي الأبعاد. والخبر السار هو أن إعادة تشغيل هذه الندوة عبر الإنترنت الغنية بالمعلومات متاحة الآن. يمكنك مشاهدته هنا.

تأخذك Katie في نظرة تفصيلية على ما يحدث داخل جهاز Speedster7T أثناء قيامه بمعالجة حزم البيانات. تساعد معرفة هذه التفاصيل على فهم سهولة الإعداد والدقة المقدمة التي تظهر أثناء العرض التوضيحي. إذا كنت تعتقد أن جهازًا فريدًا مثل هذا يمكن أن يساعد في مشروع التصميم الخاص بك، فإنني أوصي بشدة بمشاهدة العرض التوضيحي. إنها قصيرة ولكنها مفيدة جدًا. أنت تستطيع الوصول إلى الفيديو التجريبي هنا.

الآن أنت تعرف كيفية استخدام Achronix Speedster7t FPGA لاختبار القيادة في المختبر. يمكنك معرفة المزيد من التفاصيل حول هذا الأمر عائلة FPGA الفريدة هنا.

شارك هذا المنشور عبر: المصدر: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- مسرع

- الكل

- تطبيق

- هندسة معمارية

- ASIC

- قطعة

- مجلس

- تحدى

- رقاقة

- آت

- البيانات

- تصميم

- مصمم

- الهندسة

- قماش

- للعائلات

- الاسم الأول

- FPGA

- بالإضافة إلى

- خير

- مرتفع

- كيفية

- كيفية

- HTTPS

- بما فيه

- مبتكرة

- IT

- القفل

- تعلم

- تعلم

- LINK

- آلة التعلم

- التسويق

- شبكة

- أخبار

- عمليات

- أداء

- تنفيذ المشاريع

- الأسباب

- الموارد

- طريق

- تشغيل

- الأملاح

- قصير

- الحلول

- تكنولوجيا

- تجربه بالعربي

- الوقت

- حركة المرور

- فيديو

- شاهد

- الويبينار

- من الذى

- قيمة

- X

- سنوات