I ugen den 19. aprilth, Linley Group afholdt sin Spring Processor Conference 2021. Linley Group har ry for at indkalde fremragende konferencer. Og dette års forårskonference var ingen undtagelse. Der var en række meget informative foredrag fra forskellige virksomheder, der opdaterede publikum om det seneste forsknings- og udviklingsarbejde, der sker i branchen. Præsentationerne var blevet kategoriseret under otte forskellige emner. Emnerne var Edge AI, Embedded SoC Design, Scaling AI Training, AI SoC Design, Network Infrastructure for AI og 5G, Edge AI Software, Signal Processing og Efficient AI Inference.

Kunstig intelligens (AI) som en teknologi har fået megen opmærksomhed og investeringer i de seneste år. Konferencen afspejlede bestemt det i antallet af emnekategorier relateret til AI. Inden for den bredere kategori af AI var Edge AI et emne, der havde en uretfærdig andel af præsentationer og med rette. Edge computing oplever hurtig vækst drevet af IoT, 5G og andre applikationer med lav latenskrav.

En af præsentationerne inden for Edge AI-kategorien havde titlen "Forbedring af RISC-V Vector Extensions for at accelerere ydeevnen på ML-arbejdsbelastninger." Foredraget blev holdt af Chris Lattner, President, Engineering and Product hos SiFive, Inc. Chris gjorde en stærk argumentation for, hvorfor SiFives RISC-V vektorudvidelsesbaserede løsning passer godt til AI-drevne applikationer. Følgende er mit bud.

Markedskrav:

Så hurtigt som markedet for edge computing vokser, bliver disse applikationers ydeevne og strømkrav også mere og mere krævende. Mange af disse applikationer er AI-drevet og falder ind under kategorien maskinlæring (ML) arbejdsbelastninger. Og AI-adoption skubber behandlingskravene mere i retning af datamanipulation frem for generel databehandling. Dyb læring ligger til grund for ML-modeller og involverer behandling af store arrays af data. Med ML-modeller, der udvikler sig hurtigt, ville en ideel løsning være en løsning, der optimerer til: ydeevne, kraft, let at inkorporere nye ML-modeller og omfanget af resulterende hardware- og/eller softwareændringer.

RISC-V vektor fordel:

Den oprindelige motivation bag initiativet, der har givet os RISC-V-arkitekturen, er eksperimentering. Eksperimenterer for at udvikle chipdesign, der giver bedre ydeevne i lyset af den forventede opbremsning af Moores lov. RISC-V er bygget på ideen om at være i stand til at skræddersy bestemte chips, hvor du kan vælge hvilke instruktionssætudvidelser du bruger. Vektorudvidelser giver mulighed for behandling af vektorer af enhver længde ved hjælp af funktioner, der behandler vektorer med faste længder. Vektorbehandling gør det muligt for eksisterende software at køre uden omkompilering, når hardware opgraderes i form af flere ALU'er og andre funktionelle enheder. Der er sket betydelige fremskridt med hensyn til etableret hardwarebase og understøttende økosystemer såsom compilerteknologier.

RISC-V kan optimeres til et bestemt domæne eller applikation gennem brugerdefinerede udvidelser. Som en åben standard instruktionssæt-arkitektur nyder RISC-V-brugere stor fleksibilitet ved at vælge en leverandør til deres chipdesignbehov.

SiFives tilbud:

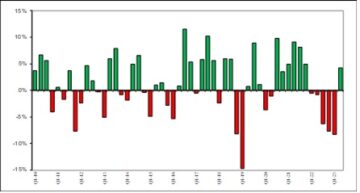

SiFive har forbedret RISC-V Vector-fordelen ved at tilføje nye vektorudvidelser til at accelerere eksekveringen af mange forskellige neurale netværksmodeller. Se figur 1 for at se et eksempel på den type speedup, der kan opnås ved at bruge SiFives tilføjelsesudvidelser sammenlignet med kun at bruge basisvektorudvidelserne af RISC-V. Dens Intelligence X280-løsning er en multi-core-kapabel RISC-V Vector-løsning (hardware og software) for at gøre det nemt for sine kunder at implementere optimerede Edge AI-applikationer. Løsningen kan også bruges til at implementere datacenterapplikationer.

Figur 1:

SiFive fordel:

- SiFives Intelligence X280-løsning understøtter fuldt ud TensorFlow og TensorFlow Lite open source platforme til maskinlæring (se figur 2)

- SiFive giver en nem måde at migrere kundens eksisterende kode baseret på andre arkitekturer til RISC-V Vector-arkitektur. For eksempel kan SiFive oversætte ARM Neon-kode til RISC-V V-samlingskode

- SiFive giver sine kunder mulighed for at udforske at tilføje brugerdefinerede udvidelser til deres RISC-V-implementeringer

- SiFive udvider gennem sin OpenFive forretningsenhed tilpassede chipimplementeringstjenester for at imødekomme domænespecifikke siliciumbehov

Figur 2:

Sammendrag:

I en nøddeskal kan SiFive-kunder nemt og hurtigt implementere deres applikationer, uanset om applikationerne involverer Edge AI-arbejdsbelastninger eller traditionelle datacentertyper. Hvis du er interesseret i at drage fordel af SiFives løsninger til at accelerere ydeevnen af dine ML-arbejdsbelastninger, anbefaler jeg, at du registrerer dig og lytter til Chris' hele snak og derefter diskutere med SiFive om måder at udnytte deres forskellige tilbud til at udvikle dine produkter.

Del dette opslag via: Kilde: https://semiwiki.com/ip/sifive/299157-enhancing-risc-v-vector-extensions-to-accelerate-performance-on-ml-workloads/

- 2021

- 5G

- Tilføjelse

- Vedtagelse

- Fordel

- AI

- AI adoption

- AI -træning

- Anvendelse

- applikationer

- april

- arkitektur

- ARM

- publikum

- virksomhed

- chip

- Chips

- kode

- Virksomheder

- computing

- Konference

- konferencer

- Kunder

- data

- Data Center

- dyb læring

- Design

- udvikle

- Udvikling

- drevet

- økosystem

- Edge

- kant computing

- Engineering

- udførelse

- udvidelser

- Ansigtet

- FAST

- Figur

- passer

- Fleksibilitet

- formular

- fuld

- Generelt

- stor

- gruppe

- Dyrkning

- Vækst

- Hardware

- HTTPS

- idé

- Inc.

- industrien

- Infrastruktur

- initiativ

- Intelligens

- investering

- tingenes internet

- IT

- stor

- seneste

- Lov

- læring

- Leverage

- machine learning

- Håndtering

- Marked

- Matters

- ML

- Neon

- netværk

- Neural

- neurale netværk

- tilbyde

- tilbud

- åbent

- Andet

- ydeevne

- Platforme

- magt

- Præsentationer

- præsident

- Produkt

- Produkter

- Krav

- forskning

- forskning og udvikling

- Kør

- skalering

- Tjenester

- sæt

- Del

- So

- Software

- Løsninger

- forår

- support

- Understøtter

- Talks

- Teknologier

- Teknologier

- tensorflow

- Initiativet

- Kurser

- us

- brugere

- uge

- inden for

- Arbejde

- år

- Udbytte