Instrumentering af post-siliciumvalidering er ikke en ny idé, men her er et twist. Brug af (præ-silicium) emulering til at vælge debug observationsstrukturer til instrumentering i silicium. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, iværksætter, tidligere Synopsys CTO) og jeg fortsætter vores serie om forskningsidéer. Som altid er feedback velkommen.

![]()

Innovation

Denne måneds valg er Emuleringsinfrastruktur til evaluering af hardwarepåstande til post-siliciumvalidering. Papiret blev præsenteret ved 2017 IEEE Transactions on VLSI. Forfatterne er fra McMaster University, Hamilton, ON, Canada

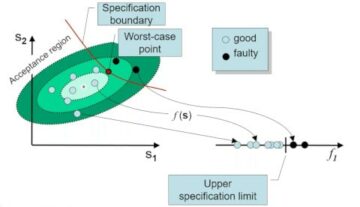

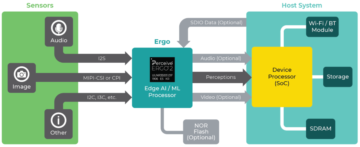

Forfatterne skelner mellem logiske og elektriske fejl efter silicium og vier deres opmærksomhed i dette papir til elektriske fejl, der kan påvises gennem bit-flips i flops. Deres tilgang er at bestemme et optimalt sæt af påstande i præ-siliciumanalyse. Disse implementerer de derefter i silicium til støtte for post-silicium debug. Præ-siliciumanalysen ligner fejl i sikkerhedsanalyser, injicering af fejl på flops svarende til elektriske fejl, som de antyder i papiret. De genererer en kandidatliste over påstande ved hjælp af påstandssyntese; kernen i deres innovation er at give en metode til at klassificere disse påstande efter, hvor effektiv hver enkelt er til at opdage flere fejl.

Inputgenerering er tilfældig og analyserer injicerede fejl (behandlet som forbigående) i rækkefølge. De tillader et brugerspecificeret antal cyklusser til detektering pr. fejl. I en efterfølgende fase måler de effektivitet ved hjælp af to forskellige dækningsteknikker. For flip-flop-dækning tæller de en påstand, hvis den fanger en injiceret fejl på et hvilket som helst flop. I bit-flip dækning, scorer de påstande antal fejl opdaget på separate flops. Disse målinger, sammen med arealestimater, bruger de (skiftevis) til at vælge, hvilke foretrukne påstande.

Pauls syn

Dette papir passer fint sammen med vores August 2020 blog om hurtig fejlfinding (QED). QED accelererer post-silicium funktionel fejldetektion, hvor denne blog fokuserer på post-silicium elektrisk fejldetektion. Papiret er letlæst, selvom det hjælper at læse referencen først [23].

Elektriske fejl er svære at fange, og selv da er de svære at replikere og finde den underliggende fysiske årsag. Forfatterne foreslår en metode, gennem indlejret logik, til at opdage, hvornår sådanne fejl får et flop til at vende til en forkert værdi (de graver ikke dybere end at finde disse flip).

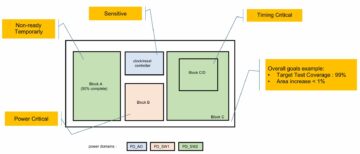

Hjertet i papiret og dets ledsagende reference [23] er en flertrinsmetode til at skabe og syntetisere denne detektionslogik. Det begynder med mineegenskaber af designet som tidsmæssige påstande ved hjælp af GoldMine værktøj. De rangerer påstande baseret på et estimat af deres evne til at detektere bitflip og et estimat af arealet/ledningsomkostningerne til at implementere i silicium. Rangordning er afhængig af at køre mange præ-silicium-simuleringer med kandidatpåstande, indsprøjtning af bitflip-fejl og tælle detekterede flip efter påstande. I det originale papir brugte de logisk simulering, her accelererer de disse simuleringer ved at kortlægge designet til et Altera FPGA-kort.

Jeg kan godt lide, hvordan de samler flere innovationer i en sammenhængende metode til post-silicium bit flip detektion: assertion mining, assertion syntese og en elegant rangeringsfunktion til assertion valg. Imidlertid indikerer resultatafsnittet af papiret, at detektering af bitflip i n% af flip-flops kræver omtrent en n% stigning i designareal. Dette virker udfordrende for kommerciel anvendelse, især da det kun hjælper med at finde elektriske fejl. Man kunne potentielt opnå et lignende resultat ved at klone den logiske kegle, der driver en flip-flop, og derefter sammenligne outputtet af denne klonede logik med den oprindelige logik. Dette synes at generere et lignende område overhead som deres metode, i grænsen kloning af hele designet (dvs. 100% område overhead) for at opdage flips i 100% af floppene i designet.

Raúls syn

Papiret er selvstændigt med en god del detaljer. Forfatterne kørte eksperimenter for 3 ISCAS sekventielle kredsløb (ca. 12K gates, 2000 FF). Forberedelseseksperimenter injicerer 256 fejl pr. flip flop og bruger alle påstande genereret af GoldMine. På grund af den begrænsede kapacitet af FPGA'en løber forfatteropdelingen op til 45 "sessioner" for et kredsløb. Resultaterne viser, selv med 45 sessioner, en acceleration i analyse over simulering på 20-500 gange (kun op til 8 fejlindsprøjtninger, fordi simuleringen bliver for langsom, 105 timer). Den maksimalt opnåelige Flip-Flop-dækning er 55 %, 89 % og 99 % for de 3 kredsløb. Antallet af mine påstande kontrollerer dækningen.

Kørsel med udvalgte påstande (svarende til et areal på 5-50 %) og 1-256 injektioner resulterer i 2.2 %-34 % bitdækning. Det meste af tiden løb påstandsminearbejderen i 228 timer. En ting, der forvirrede mig, er deres data for kørselstider kontra indførte fejl. Stigningen ser rimelig (lineær) ud i simulering. Men i emulering springer det massivt fra 0.045 timer til 5.4 timer for en stigning på 2 til 8 fejlindsprøjtninger. Jeg vil gerne have mere forklaring på dette punkt.

Dette er et metodologisk papir. Jeg kan godt lide, at stort set alle trin kan erstattes af et kommercielt værktøj. Sammen med at bruge et stort FPGA-kort (som emulator) skalerer metoden. Metoder er selvfølgelig meget svære at kommercialisere, men det er en fin applikation til eksisterende teknologi!

Min udsigt

Metoden til at udforske en sikkerhedsanalyseteknik til post-silicium debug er spændende. En ny idé, selvom det fører til et noget upraktisk resultat til kommerciel anvendelse.

Del dette opslag via: Kilde: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Alle

- analyse

- Anvendelse

- OMRÅDE

- forfattere

- Bit

- Blog

- board

- Bug

- bugs

- kadence

- Kapacitet

- brydning

- Årsag

- kommerciel

- fortsæt

- CTO

- data

- Design

- detail

- Detektion

- kørsel

- Effektiv

- Entrepreneur

- skøn

- retfærdig

- Fornavn

- FPGA

- funktion

- Gates

- GM

- Hardware

- link.

- Hvordan

- HTTPS

- idé

- IEEE

- Forøg

- Infrastruktur

- Innovation

- IT

- stor

- førende

- Limited

- Liste

- måle

- Metrics

- Mining

- Papir

- foreslå

- forskning

- Resultater

- kører

- Sikkerhed

- valgt

- Series

- sæt

- simulation

- delt

- support

- tid

- Transaktioner

- Twist

- universitet

- værdi

- Verifikation

- versus