I hver chip er strøm et progressivt problem, der skal løses. Designere har længe været nødt til at stole på en kombination af erfaring og viden for at tackle dette dilemma, og de har typisk skullet vente til efter siliciumtilgængelighed for at udføre strømanalyse med realistiske softwarebelastninger. Dette er dog for sent i spillet, da det bliver et dyrt og tidskrævende forslag at løse strømproblemer efter silicium. I dette blogindlæg vil jeg forklare, hvordan du tidligt kan opnå effektive effektverifikationsresultater på timer på billion-gate-design. Med denne funktion kan du finde de kritiske områder og tidsvinduer for spidseffekt og dermed optimere din RTL og software.

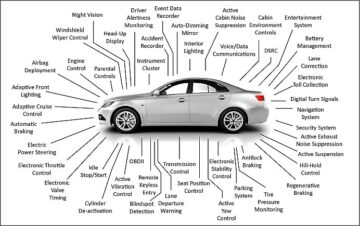

Udførelse af strømanalyse efter silicium introducerer risikoen for at gå glip af kritiske situationer med høj effekt, hvilket kan skabe betydelige omkostninger og problemer med produktvedtagelse. Ulemperne ved at tage fejl om magt? En kunde kan vælge at gå med en anden chipleverandør, hvis et design misser det lovede effektmål. Eller en systemdesigner kan blive tvunget til at skrue tilbage på chip-ydeevnen for at opretholde den målrettede effektomkreds - en ugunstig afvejning i applikationer, der er afhængige af hurtig beregningsydelse. I dette indlæg, som oprindeligt blev offentliggjort på "Fra silicium til software" blog, vil vi se nærmere på nogle SoC-applikationsområder, hvor nøjagtig strømanalyse er afgørende.

GPU'er

Traditionelle GPU-applikationer er kendte enheder til sammenligning, men dette gør ikke energianalyseopgaven nemmere. Overvej en GPU designet til en bærbar computer. Du kan køre effektanalyse på bestemte målepunkter over en periode. Men med potentielt op til 10 millioner clock-cyklusser er denne tilgang tydeligvis ikke udtømmende - hvilket er grunden til, at designere traditionelt har været nødt til at stole på deres bedste estimater for effekt.

Kunstig intelligens

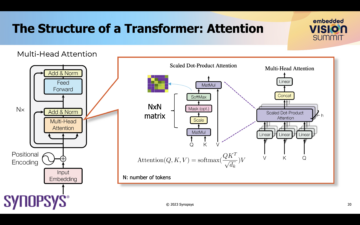

Inden for kunstig intelligens (AI)-chips er applikationerne såvel som softwarestakken til AI-applikationer og -arkitekturer alle nyt territorium, hvilket giver flere udfordringer set fra et magtprofileringsperspektiv. Alligevel er de potentielle fordele ved at optimere AI-applikationer for kraft store. Strømeffektivitet er trods alt en fordel, som AI-chipdesignere ville elske at være i stand til at fremvise sammen med hurtig beregningsydelse.

5G

En anden strømkritisk applikation er 5G, som handler om høj ydeevne og lav latenstid. 5G-applikationer involverer en masse parallel behandling og høje frekvenser, men med kun så meget strøm til rådighed, skal de optimeres til at køre effektivt. Dette gælder især for radiohovedchips.

datacentre

Datacentre, især hyperskala datacentre, er bygget på lynhurtige, energieffektive chips, der kan hjælpe med at maksimere den samlede systemgennemstrømning. Med milliarder af porte sammen med komplekse software-arbejdsbelastninger, kommer datacenter-SoC'er med særligt krævende krav til verifikation og softwareopdrag.

Mobil

På grund af deres kompakte formfaktor og ønskede lange batterilevetid har mobile enheder som smartphones ikke råd til at bruge chips, der bruger for meget strøm. Selvom deres arbejdsbelastning er vokset i kompleksitet, skal disse enheder – selv de strømkrævende GPU'er – stadig være i stand til at håndtere disse arbejdsbelastninger effektivt.

Hvordan en Fast Power Emulator løser Power Profiling Challenge

Da det bliver stadig sværere at opfylde dynamiske strømkrav, betragter chipdesignere ofte strøm som deres største verifikationsudfordring. Dynamisk effektverifikation kræver at finde spidseffekt. Alligevel er kritiske spidseffekthændelser drevet af faktiske software-arbejdsbelastninger. Simulering kan identificere spidseffekt, der falder over såvel som under strømbudgettet, men i milliardporte-design vil den kun være i stand til at fange de virkelige kritiske hændelser ved rent held, da de vinduer, en simuleringsbaseret tilgang kan overveje, er alt for meget. lille. Et signoff-værktøj ville give nøjagtige effektmålinger, men hvis det bruges på det forkerte tidsvindue, ville designeren ikke være i stand til at bestemme, hvilket vindue der har den højeste effekt.

Identifikation af lavstrømsfejl kræver kørsel af softwarearbejdsbelastninger. Små test vil ikke afsløre realistiske arbejdsbelastningsdrevne strømfejl. Det der skal til er:

- Ægte firmware og operativsystem ved pre-silicium test

- Emulering for at verificere kraft over millioner eller milliarder af cyklusser

- Præ-silicium effektverifikation til fejlretning, hvilket ikke er muligt med faktisk silicium

Højhastighedsemulering giver designteams mulighed for at udføre effektverifikation tidligere i designcyklussen, så de kan minimere risikoen for strømfejl og mistede SoC-strømmål. Faktisk kan en hurtig strømemulator være svaret på hardware/software-strømverifikationsdilemmaet, hvilket giver bedre nøjagtighed over et bredere vindue. Den ideelle emulator ville være i stand til at køre flere iterationer om dagen på store designs med realistiske arbejdsbelastninger. Ved at gøre det kan chipdesignere få brugbar indsigt i deres designs kraftprofil.

Handlingsbar indsigt i timer

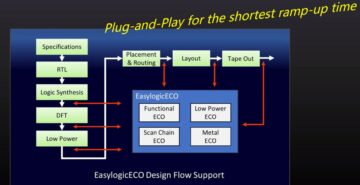

Med multi-milliard-gate SoC-arbejdsbelastninger i tankerne, Synopsys har afsløret sit nye Synopsys ZeBu® Empower-emuleringssystem til hardware/software-strømverifikation. Leverer maksimal computerydelse, ZeBu Empower kan udføre flere iterationer om dagen, hvilket giver brugbare resultater på timer. Baseret på de resulterende strømprofiler kan hardware- og softwaredesignere tidligt identificere områder, hvor de kan forbedre dynamisk og lækagestyrke. ZeBu Empower bruger ZeBu server hurtig emuleringshardwareteknologi for at give de korte ekspeditionstider.

ZeBu Empower sender også strømkritiske blokke og tidsvinduer frem i Synopsys PrimePower-motor for at accelerere RTL-effektanalyse og gate-niveau power signoff. Både ZeBu Empower og PrimePower er en del af Synopsys software-drevet lavstrømsløsning. Afbildet i diagrammet nedenfor giver lavstrømsløsningen et end-to-end flow og metodologi, der spænder fra arkitekturanalyse til blok-RTL-strømanalyse til SoC-strømanalyse og optimering.

Synopsys software-drevne lavstrømsløsning er designet til at hjælpe med at reducere det samlede dynamiske og statiske strømforbrug af IC'er.

Resumé

Strøm er måske bare den mest udfordrende del af kraft-, ydeevne- og arealligningen (PPA). Og når det kommer til multi-milliard-gate-design, vokser kompleksiteten i at opnå nøjagtige strømprofiler kun. Men med den hurtige strømemuleringsløsning fra Synopsys kan designteams nu finde de kritiske områder og tidsvinduer for spidseffekt, så de kan optimere deres RTL og deres software. Ved at drage fordel af det omfattende Synopsys-low-power flow får designere værktøjer, der kan hjælpe dem med at nå deres PPA-mål. I betragtning af de store arbejdsbelastninger og ydeevnekrav fra applikationer som GPU'er, AI, 5G, datacentre og mobil, bør enhver løsning, der kan give et mere præcist effektbillede, være en velkommen tilføjelse til enhver designers PPA-værktøjssæt.

Del dette opslag via: Kilde: https://semiwiki.com/eda/synopsys/301320-optimize-rtl-and-software-with-fast-power-verification-results-for-billion-gate-designs/

- 5G

- Vedtagelse

- Fordel

- AI

- Alle

- analyse

- Anvendelse

- applikationer

- arkitektur

- OMRÅDE

- kunstig intelligens

- Kunstig intelligens (AI)

- tilgængelighed

- batteri

- BEDSTE

- Blog

- bugs

- brydning

- udfordre

- chip

- Chips

- tættere

- Compute

- forbruge

- forbrug

- data

- Data Center

- datacentre

- dag

- leverer

- Design

- Designer

- Enheder

- drevet

- Tidligt

- effektivitet

- bemyndige

- skøn

- begivenheder

- FAST

- flow

- formular

- Videresend

- spil

- Gates

- GPU

- GPU'er

- stor

- Hardware

- hoved

- Høj

- Hvordan

- HTTPS

- ICS

- identificere

- indsigt

- Intelligens

- spørgsmål

- IT

- viden

- laptop

- stor

- Lang

- kærlighed

- million

- Mobil

- mobilenheder

- drift

- operativsystem

- ydeevne

- perspektiv

- billede

- magt

- Produkt

- Profil

- Profiler

- Radio

- reducere

- Krav

- Resultater

- Belønninger

- Risiko

- Kør

- kører

- Kort

- simulation

- lille

- smartphones

- So

- Software

- systemet

- mål

- Teknologier

- tests

- tid

- top

- Verifikation

- vente

- vinduer