Die Instrumentierung der Post-Silizium-Validierung ist keine neue Idee, aber hier gibt es eine Wendung. Verwendung der (Prä-Silizium-)Emulation zur Auswahl von Debug-Beobachtungsstrukturen für die In-Silizium-Instrumentierung. Paul Cunningham (GM, Verification bei Cadence), Raúl Camposano (Silicon Catalyst, Unternehmer, ehemaliger CTO von Synopsys) und ich setzen unsere Reihe über Forschungsideen fort. Feedback ist wie immer willkommen.

![]()

Die Innovation

Die Auswahl dieses Monats ist Emulationsinfrastruktur zur Bewertung von Hardware-Assertions für die Post-Silicon-Validierung. Das Papier wurde auf der IEEE Transactions on VLSI 2017 vorgestellt. Die Autoren stammen von der McMaster University, Hamilton, ON, Kanada

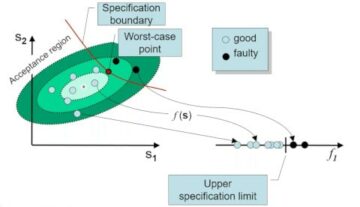

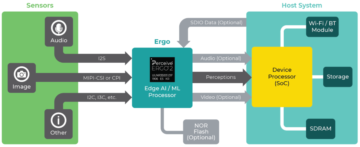

Die Autoren unterscheiden zwischen logischen und elektrischen Fehlern nach dem Silizium und widmen in dieser Arbeit ihre Aufmerksamkeit elektrischen Fehlern, die durch Bit-Flips in Flops erkennbar sind. Ihr Ansatz besteht darin, einen optimalen Satz von Aussagen in der Präsiliziumanalyse zu ermitteln. Diese implementieren sie dann in Silizium zur Unterstützung des Post-Silicon-Debugging. Die Pre-Silicium-Analyse ähnelt der Fehlererkennung bei Sicherheitsanalysen, indem Fehler in Flops eingefügt werden, die elektrischen Fehlern entsprechen, wie in dem Artikel angedeutet wird. Sie generieren mithilfe der Behauptungssynthese eine Kandidatenliste von Behauptungen. Der Kern ihrer Innovation besteht darin, eine Methode bereitzustellen, um diese Behauptungen danach zu bewerten, wie effektiv jede einzelne bei der Erkennung mehrerer Fehler ist.

Die Eingabegenerierung erfolgt zufällig, wobei injizierte Fehler (die als vorübergehend behandelt werden) nacheinander analysiert werden. Sie ermöglichen eine vom Benutzer festgelegte Anzahl von Erkennungszyklen pro Fehler. In einer anschließenden Phase messen sie die Wirksamkeit mithilfe zweier unterschiedlicher Abdeckungstechniken. Für die Flip-Flop-Abdeckung zählen sie eine Behauptung, wenn sie auf einem Flop einen injizierten Fehler abfängt. Bei der Bit-Flip-Abdeckung ermitteln sie die Anzahl der auf separaten Flops erkannten Fehler. Diese Metriken werden zusammen mit Flächenschätzungen (abwechselnd) verwendet, um die bevorzugten Behauptungen auszuwählen.

Pauls Ansicht

Dieses Papier passt gut zu unserem Blog vom August 2020 zur schnellen Fehlererkennung (QED). QED beschleunigt die Post-Silicon-Funktionsfehlererkennung, wobei sich dieser Blog auf die Post-Silicon-Elektrofehlererkennung konzentriert. Das Papier ist leicht zu lesen, obwohl es hilfreich ist, zuerst die Referenz zu lesen [23].

Elektrische Fehler sind schwer zu erkennen und selbst dann ist es schwierig, sie zu reproduzieren und die zugrunde liegende physische Ursache zu finden. Die Autoren schlagen eine Methode durch eingebettete Logik vor, um zu erkennen, wann solche Fehler dazu führen, dass ein Flop auf einen falschen Wert umkippt (sie graben nicht tiefer, als diese Umschläge zu finden).

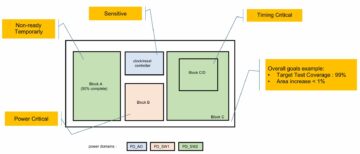

Das Herzstück des Artikels und seiner begleitenden Referenz [23] ist eine mehrstufige Methode zur Erstellung und Synthese dieser Erkennungslogik. Es beginnt mit der Gewinnung von Eigenschaften des Entwurfs als zeitliche Aussagen unter Verwendung der GoldMine-Tool. Sie ordnen Behauptungen basierend auf einer Schätzung ihrer Fähigkeit, Bit-Flips zu erkennen, und einer Schätzung der Flächen-/Verdrahtungskosten für die Implementierung in Silizium. Das Ranking basiert auf der Durchführung vieler Pre-Silicon-Simulationen mit Kandidaten-Assertions, dem Einfügen von Bit-Flip-Fehlern und dem Zählen erkannter Flips durch Assertionen. In der Originalarbeit nutzten sie die Logiksimulation, hier beschleunigen sie diese Simulationen, indem sie das Design auf eine Altera-FPGA-Karte abbilden.

Mir gefällt, wie sie mehrere Innovationen zu einer kohärenten Methode zur Post-Silicon-Bit-Flip-Erkennung zusammenführen: Assertion Mining, Assertion Synthesis und eine elegante Ranking-Funktion für die Assertionsauswahl. Aus dem Ergebnisteil des Papiers geht jedoch hervor, dass die Erkennung von Bit-Flips in n % der Flip-Flops eine Vergrößerung der Entwurfsfläche um etwa n % erfordert. Dies scheint für eine kommerzielle Anwendung eine Herausforderung zu sein, insbesondere da es nur dabei hilft, elektrische Fehler zu finden. Möglicherweise könnte man ein ähnliches Ergebnis erzielen, indem man den Logikkegel, der ein Flip-Flop antreibt, klont und dann die Ausgabe dieser geklonten Logik mit der ursprünglichen Logik vergleicht. Dies scheint einen ähnlichen Flächen-Overhead zu erzeugen wie ihre Methode, bei der das gesamte Design geklont wird (d. h. 100 % Flächen-Overhead), um Flips in 100 % der Flops im Design zu erkennen.

Raúls Ansicht

Das Papier ist in sich geschlossen und enthält eine ganze Menge Details. Die Autoren führten Experimente für 3 ISCAS-Sequenzschaltungen durch (ca. 12K-Gatter, 2000 FF). Vorbereitungsexperimente führen zu 256 Fehlern pro Flip-Flop und unter Verwendung aller von GoldMine generierten Behauptungen. Aufgrund der begrenzten Kapazität des FPGA haben die Autoren die Läufe auf 45 „Sitzungen“ für eine Schaltung aufgeteilt. Die Ergebnisse zeigen, selbst bei 45 Sitzungen, eine Beschleunigung der Analyse gegenüber der Simulation um das 20- bis 500-fache (nur bis zu 8 Fehlerinjektionen, da die Simulation zu langsam wird, 105 Stunden). Die maximal erreichbare Flip-Flop-Abdeckung beträgt 55 %, 89 % und 99 % für die 3 Schaltkreise. Die Anzahl der ermittelten Behauptungen steuert die Abdeckung.

Das Ausführen mit ausgewählten Assertionen (entsprechend einem Flächen-Overhead von 5–50 %) und 1–256 Injektionen führt zu einer Bitabdeckung von 2.2–34 %. Meistens lief der Assertion Miner 228 Stunden lang. Eine Sache, die mich verwirrt hat, sind die Daten zu Laufzeiten im Vergleich zu injizierten Fehlern. Der Anstieg sieht in der Simulation vernünftig (linear) aus. Aber in der Emulation springt sie massiv an, von 0.045 Stunden auf 5.4 Stunden, was einem Anstieg von 2 auf 8 Fehlerinjektionen entspricht. Ich hätte gerne mehr Erklärungen zu diesem Punkt.

Dies ist ein Methodenpapier. Mir gefällt, dass so ziemlich jeder Schritt durch ein kommerzielles Tool ersetzt werden kann. Zusammen mit der Verwendung eines großen FPGA-Boards (als Emulator) lässt sich die Methodik skalieren. Methoden sind natürlich sehr schwer zu kommerzialisieren, aber es ist eine schöne Anwendung für bestehende Technologie!

Meine Sicht

Die Methode zur Erforschung einer Sicherheitsanalysetechnik für das Post-Silicon-Debugging ist faszinierend. Eine neuartige Idee, auch wenn sie für eine kommerzielle Anwendung zu einem etwas unpraktischen Ergebnis führt.

Teile diesen Beitrag über: Quelle: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Alle

- Analyse

- Anwendung

- Bereich

- Autoren

- Bit

- Blog

- Tafel

- Fehler

- Bugs

- Kadenz

- Kapazität

- Ringen

- Verursachen

- kommerziell

- fortsetzen

- CTO

- technische Daten

- Design

- Detail

- Entdeckung

- Fahren

- Effektiv

- Unternehmer

- Schätzungen

- Messe

- Vorname

- FPGA

- Funktion

- Gates

- GM

- Hardware

- hier

- Ultraschall

- HTTPS

- Idee

- IEEE

- Erhöhung

- Infrastruktur

- Innovation

- IT

- grosse

- führenden

- Limitiert

- Liste

- messen

- Metrik

- Bergbau

- Papier

- bietet

- Forschungsprojekte

- Die Ergebnisse

- Laufen

- Sicherheit

- ausgewählt

- Modellreihe

- kompensieren

- Simulation

- gespalten

- Support

- Zeit

- Transaktionen

- Twist

- Universität

- Wert

- Verification

- Gegen