In jedem Chip ist die Leistung ein fortschreitendes Problem, das gelöst werden muss. Um dieses Dilemma zu bewältigen, waren Entwickler lange Zeit auf eine Kombination aus Erfahrung und Wissen angewiesen und mussten in der Regel bis zur Siliziumverfügbarkeit warten, um eine Leistungsanalyse mit realistischen Software-Workloads durchzuführen. Dies ist jedoch zu spät im Spiel, da es zu einem kostspieligen und zeitaufwändigen Unterfangen wird, Stromversorgungsprobleme nach der Siliziumproduktion zu lösen. In diesem Blogbeitrag erkläre ich, wie Sie bei Milliarden-Gate-Designs schon früh binnen Stunden verwertbare Ergebnisse zur Leistungsüberprüfung erzielen können. Mit dieser Funktion können Sie die kritischen Bereiche und Zeitfenster für Spitzenleistungen finden und so Ihr RTL und Ihre Software optimieren.

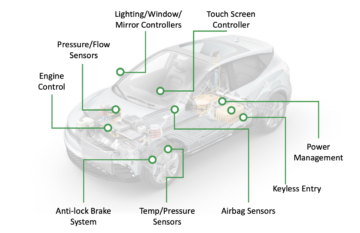

Die Durchführung einer Leistungsanalyse nach dem Silizium birgt das Risiko, dass kritische Hochleistungssituationen übersehen werden, was zu erheblichen Kosten- und Produktakzeptanzproblemen führen kann. Die Nachteile, wenn man in Bezug auf Macht falsch liegt? Ein Kunde könnte sich für einen anderen Chipanbieter entscheiden, wenn ein Design das versprochene Leistungsziel verfehlt. Oder ein Systemdesigner könnte gezwungen sein, die Chipleistung zurückzuschrauben, um die angestrebte Leistungsgrenze beizubehalten – ein ungünstiger Kompromiss bei Anwendungen, die auf schnelle Rechenleistung angewiesen sind. In diesem Beitrag, der ursprünglich am veröffentlicht wurde Blog „Vom Silizium zur Software“., werfen wir einen genaueren Blick auf einige SoC-Anwendungsbereiche, in denen eine genaue Leistungsanalyse unerlässlich ist.

GPUs

Herkömmliche GPU-Anwendungen sind im Vergleich dazu bekannte Einheiten, aber das macht die Aufgabe der Leistungsanalyse nicht einfacher. Stellen Sie sich eine GPU vor, die für einen Laptop-Computer entwickelt wurde. Sie können an bestimmten Messpunkten über einen bestimmten Zeitraum eine Leistungsanalyse durchführen. Allerdings ist dieser Ansatz mit potenziell bis zu 10 Millionen Taktzyklen eindeutig nicht erschöpfend – weshalb sich Entwickler traditionell auf ihre besten Schätzungen für die Leistung verlassen mussten.

Artificial Intelligence

Bei Chips für künstliche Intelligenz (KI) sind die Anwendungen sowie der Software-Stack für KI-Anwendungen und -Architekturen allesamt Neuland, was aus Sicht der Leistungsprofilierung größere Herausforderungen mit sich bringt. Dennoch sind die potenziellen Vorteile der Optimierung von KI-Anwendungen für die Stromversorgung groß. Schließlich ist die Energieeffizienz ein Vorteil, den KI-Chipdesigner neben der schnellen Rechenleistung gerne anpreisen würden.

5G

Eine weitere energiekritische Anwendung ist 5G, bei der es auf hohe Leistung und geringe Latenz ankommt. 5G-Anwendungen erfordern viel Parallelverarbeitung und hohe Frequenzen, aber da nur eine begrenzte Leistung zur Verfügung steht, müssen sie für einen effizienten Betrieb optimiert werden. Dies gilt insbesondere für Funkkopfchips.

Daten Center

Rechenzentren, insbesondere Hyperscale-Rechenzentren, basieren auf blitzschnellen, energieeffizienten Chips, die zur Maximierung des Gesamtsystemdurchsatzes beitragen können. Mit Milliarden von Gates und komplexen Software-Workloads stellen SoCs in Rechenzentren besonders anspruchsvolle Anforderungen an die Verifizierung und Softwarebereitstellung.

Mobil

Aufgrund ihres kompakten Formfaktors und der gewünschten langen Akkulaufzeit können es sich mobile Geräte wie Smartphones nicht leisten, Chips zu verwenden, die zu viel Strom verbrauchen. Auch wenn die Komplexität ihrer Arbeitslasten zugenommen hat, müssen diese Geräte – selbst die stromhungrigen GPUs – diese Arbeitslasten immer noch energieeffizient bewältigen können.

Wie ein schneller Power-Emulator die Power-Profiling-Herausforderung löst

Da die Erfüllung dynamischer Leistungsanforderungen immer schwieriger wird, betrachten Chipdesigner die Stromversorgung häufig als ihre größte Herausforderung bei der Verifizierung. Bei der dynamischen Leistungsüberprüfung muss die Spitzenleistung ermittelt werden. Kritische Spitzenstromereignisse werden jedoch durch tatsächliche Software-Workloads verursacht. Die Simulation kann Spitzenleistungen identifizieren, die sowohl über als auch unter dem Leistungsbudget liegen, aber in Milliarden-Gate-Designs wird sie nur durch reines Glück in der Lage sein, die wirklich kritischen Ereignisse zu erfassen, da die Zeitfenster, die ein auf Simulation basierender Ansatz berücksichtigen kann, viel zu groß sind klein. Ein Signoff-Tool würde genaue Leistungsmessungen liefern, aber wenn es im falschen Zeitfenster verwendet wird, wäre der Designer nicht in der Lage zu bestimmen, welches Fenster die höchste Leistung hat.

Das Erkennen von Fehlern mit geringem Stromverbrauch erfordert die Ausführung von Software-Workloads. Kleine Tests werden keine realistischen, arbeitslastbedingten Leistungsfehler aufdecken. Was benötigt wird ist:

- Echte Firmware und Betriebssystem beim Pre-Silicon-Test

- Emulation zur Überprüfung der Leistung über Millionen oder Milliarden Zyklen

- Überprüfung der Stromversorgung vor dem Silizium zum Debuggen, was mit echtem Silizium nicht möglich ist

Durch die Hochgeschwindigkeitsemulation können Designteams die Leistungsüberprüfung früher im Designzyklus durchführen und so das Risiko von Leistungsfehlern und verfehlten SoC-Leistungszielen minimieren. Tatsächlich kann ein schneller Leistungsemulator die Antwort auf das Hardware-/Software-Leistungsüberprüfungsdilemma sein und eine bessere Genauigkeit über einen größeren Zeitraum hinweg bieten. Der ideale Emulator wäre in der Lage, mehrere Iterationen pro Tag für große Designs mit realistischen Arbeitslasten auszuführen. Auf diese Weise können Chipdesigner verwertbare Einblicke in das Leistungsprofil ihrer Designs gewinnen.

Umsetzbare Erkenntnisse in Stunden

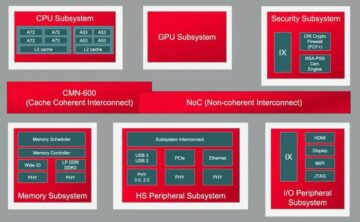

Mit Blick auf Multi-Milliarden-Gate-SoC-Workloads Synopsys hat sein neues Synopsys ZeBu® Empower-Emulationssystem für die Hardware-/Software-Leistungsüberprüfung vorgestellt. Bereitstellung maximaler Rechenleistung, ZeBu Empower kann mehrere Iterationen pro Tag durchführen und so innerhalb von Stunden umsetzbare Ergebnisse liefern. Basierend auf den resultierenden Leistungsprofilen können Hardware- und Softwareentwickler frühzeitig Bereiche identifizieren, in denen sie die Dynamik- und Verlustleistung verbessern können. ZeBu Empower nutzt ZeBu-Server Schnelle Emulations-Hardwaretechnologie für kurze Bearbeitungszeiten.

ZeBu Empower speist auch leistungskritische Blöcke und Zeitfenster in das ein Synopsys PrimePower-Engine um die RTL-Leistungsanalyse und die Leistungsabmeldung auf Gate-Ebene zu beschleunigen. Sowohl ZeBu Empower als auch PrimePower sind Teil des Synopsys softwaregesteuerte Low-Power-Lösung. Die im Diagramm unten abgebildete Low-Power-Lösung bietet einen durchgängigen Ablauf und eine Methodik, die von der Architekturanalyse über die Block-RTL-Leistungsanalyse bis hin zur SoC-Leistungsanalyse und -Optimierung reicht.

Die softwaregesteuerte Low-Power-Lösung von Synopsys soll dazu beitragen, den gesamten dynamischen und statischen Stromverbrauch von ICs zu reduzieren.

Zusammenfassung

Die Leistung ist möglicherweise der schwierigste Teil der PPA-Gleichung (Power, Performance, Area). Und wenn es um Multimilliarden-Gate-Designs geht, nimmt die Komplexität bei der Erstellung präziser Leistungsprofile nur noch zu. Mit der schnellen Leistungsemulationslösung von Synopsys können Designteams jetzt jedoch die kritischen Bereiche und Zeitfenster für die Spitzenleistung finden, sodass sie ihr RTL und ihre Software optimieren können. Durch die Nutzung des umfassenden Low-Power-Flows von Synopsys erhalten Designer Tools, die ihnen beim Erreichen ihrer PPA-Ziele helfen können. Angesichts der hohen Arbeitsbelastung und Leistungsanforderungen von Anwendungen wie GPUs, KI, 5G, Rechenzentren und Mobilgeräten sollte jede Lösung, die ein genaueres Leistungsbild liefern kann, eine willkommene Ergänzung zum PPA-Toolkit eines jeden Designers sein.

Teile diesen Beitrag über: Quelle: https://semiwiki.com/eda/synopsys/301320-optimize-rtl-and-software-with-fast-power-verification-results-for-billion-gate-designs/

- 5G

- Adoption

- Vorteil

- AI

- Alle

- Analyse

- Anwendung

- Anwendungen

- Architektur

- Bereich

- künstliche Intelligenz

- Künstliche Intelligenz (AI)

- Verfügbarkeit

- austauschbare Akkus

- BESTE

- Blog

- Bugs

- Ringen

- challenges

- Chip

- Pommes frites

- näher

- Berechnen

- verbrauchen

- Verbrauch

- technische Daten

- Data Center

- Rechenzentren

- Tag

- liefern

- Design

- Designer

- Geräte

- angetrieben

- Früh

- Effizienz

- ermächtigen

- Schätzungen

- Veranstaltungen

- FAST

- Fluss

- unten stehende Formular

- vorwärts

- Spiel

- Gates

- GPU

- GPUs

- groß

- Hardware

- ganzer

- High

- Ultraschall

- HTTPS

- ICS

- identifizieren

- Einblicke

- Intelligenz

- Probleme

- IT

- Wissen

- Laptop

- grosse

- Lang

- ich liebe

- Million

- Mobil

- mobile Geräte

- die

- Betriebssystem

- Leistung

- Perspektive

- ein Bild

- Werkzeuge

- Produkt

- Profil

- Profil

- Radio

- Veteran

- Voraussetzungen:

- Die Ergebnisse

- Belohnung

- Risiko

- Führen Sie

- Laufen

- Short

- Simulation

- klein

- Smartphones

- So

- Software

- System

- Target

- Technologie

- Tests

- Zeit

- Top

- Verification

- warten

- Fenster