Achronix ist für seine leistungsstarken FPGA-Lösungen bekannt. In diesem Beitrag werde ich das Speedster7T FPGA erkunden. Diese FPGA-Familie ist für Workloads mit hoher Bandbreite optimiert und beseitigt Leistungsengpässe durch eine innovative Architektur. Basierend auf dem 7-nm-FinFET-Prozess von TSMC bietet die Familie Leistung auf ASIC-Niveau und behält gleichzeitig die volle Programmierbarkeit eines FPGA bei. Es gibt viel über den Speedster7T zu lernen. Achronix stellt jetzt ein Video zur Verfügung, das viele dieser Fragen beantwortet. Es gibt einen Link zu diesem Video und weitere folgen, aber schauen wir uns zunächst an, was passiert, wenn Sie den Achronix Speedster7t FPGA für eine Testfahrt im Labor mitnehmen.

Achronix ist für seine leistungsstarken FPGA-Lösungen bekannt. In diesem Beitrag werde ich das Speedster7T FPGA erkunden. Diese FPGA-Familie ist für Workloads mit hoher Bandbreite optimiert und beseitigt Leistungsengpässe durch eine innovative Architektur. Basierend auf dem 7-nm-FinFET-Prozess von TSMC bietet die Familie Leistung auf ASIC-Niveau und behält gleichzeitig die volle Programmierbarkeit eines FPGA bei. Es gibt viel über den Speedster7T zu lernen. Achronix stellt jetzt ein Video zur Verfügung, das viele dieser Fragen beantwortet. Es gibt einen Link zu diesem Video und weitere folgen, aber schauen wir uns zunächst an, was passiert, wenn Sie den Achronix Speedster7t FPGA für eine Testfahrt im Labor mitnehmen.

Steve Mensor, Vizepräsident für Vertrieb und Marketing bei Achronix, stellt das Video vor. Steve ist seit fast zehn Jahren bei Achronix und verbrachte davor 21 Jahre bei Altera. Er weiß sicherlich viel über FPGAs – Design und Anwendung. Steve skizziert zunächst einige Elemente der zuvor erwähnten innovativen Architektur. An Bord des Speedster7T gibt es zahlreiche dedizierte Funktionen. Das beinhaltet:

- 112 Gbit/s SerDes

- 400G Ethernet

- PCIe Gen5

- GDDR6 läuft mit 4 Tbit/s

- DDR 4 läuft mit 3,200 Mbit/s

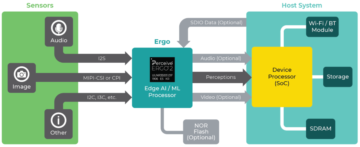

- Ein proprietärer Prozessor für maschinelles Lernen

- 2D-Netzwerk-on-Chip (NoC)

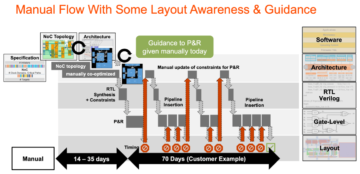

Der proprietäre Prozessor für maschinelles Lernen bietet zahlreiche Funktionen, darunter Gleitkomma-, Block-Gleitkomma- und Ganzzahloperationen. Das 2D NoC ist eine branchenweit neue Funktion für FPGAs von Achronix. Der NoC kann Daten von jeder Hochgeschwindigkeitsschnittstelle mit 2 GHz an die FPGA-Kernstruktur weiterleiten, ohne die Logikressourcen des FPGA zu verbrauchen. Mit all dieser integrierten Technologie können Sie in einem FPGA eine Leistung auf ASIC-Niveau erreichen.

Anschließend übergibt Steve die Präsentation an Katie Purcell, Application Engineering Manager bei Achronix. Katie ist seit vier Jahren bei Achronix. Zuvor war sie ASIC-Designerin. Sie verbrachte auch Zeit bei Xilinx. Katie ist diejenige, die den Speedster7t FPGA für eine Probefahrt im Labor mitnimmt, und sie ist der Herausforderung definitiv gewachsen.

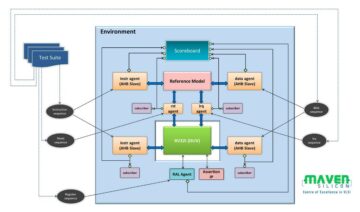

Katie nimmt den Betrachter mit in das Achronix-Labor, wo der Aufbau des Speedster7T durchgeführt wird – Validierung und Charakterisierung. Die Demo, die Katie präsentiert, zeigt das Gerät, auf dem 400G-Ethernet-Verkehr läuft Achronix VectorPath-Beschleunigerkarte. Katie fasst zunächst die Schlüsselelemente der Demonstration zusammen, darunter:

- 8 x 50G externe Schnittstelle

- Einzelne 400G-Schnittstelle im Ethernet-Subsystem

- Daten im 2D-NoC auf vier separate Streams aufgeteilt

- Jeder Stream wurde unabhängig verarbeitet

Katie verbringt einige Zeit mit dem 2D NoC. Sie weist darauf hin, dass diese Fähigkeit das Design einfacher macht und die zeitliche Abstimmung erleichtert. Dieses einzigartige 2D-NoC tauchte während der Demo mehrmals auf. Um es zu verstehen, lohnt es sich, etwas tiefer in die Materie einzutauchen. Achronix hat zuvor ein Webinar über diese einzigartige Funktion präsentiert behandelt auf SemiWiki namens 5 Gründe, warum eine rekonfigurierbare Hochleistungs-SmartNIC ein 2D-NoC erfordert. Die gute Nachricht ist, dass eine Wiederholung dieses sehr informativen Webinars jetzt verfügbar ist. Hier kannst du es dir anschauen.

Katie führt Sie durch einen detaillierten Einblick in die Vorgänge im Inneren des Speedster7T-Geräts, während es die Datenpakete verarbeitet. Die Kenntnis dieser Details hilft, die einfache Einrichtung und die gelieferte Genauigkeit zu verstehen, die während der Demo gezeigt werden. Wenn Sie der Meinung sind, dass ein einzigartiges Gerät wie dieses Ihrem Designprojekt helfen könnte, empfehle ich Ihnen dringend, sich die Demo anzusehen. Es ist kurz, aber sehr nützlich. Du kannst Hier gelangen Sie zum Demo-Video.

Jetzt wissen Sie, wie Sie den Achronix Speedster7t FPGA für eine Testfahrt im Labor nutzen. Näheres dazu erfahren Sie hier einzigartige FPGA-Familie hier.

Teile diesen Beitrag über: Quelle: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- Beschleuniger

- Alle

- Anwendung

- Architektur

- ASIC

- Bit

- Tafel

- challenges

- Chip

- Kommen

- technische Daten

- Design

- Designer

- Entwicklung

- Stoff

- Familie

- Vorname

- FPGA

- voller

- gut

- High

- Ultraschall

- Hilfe

- HTTPS

- Einschließlich

- innovativ

- IT

- Wesentliche

- LERNEN

- lernen

- LINK

- Maschinelles Lernen

- Marketing

- Netzwerk

- News

- Einkauf & Prozesse

- Leistung

- Projekt

- Gründe

- Downloads

- Straße

- Laufen

- Vertrieb

- Short

- Lösungen

- Technologie

- Test

- Zeit

- der Verkehr

- Video

- Ansehen

- Webinar

- WHO

- wert

- X

- Jahr