Instrumentar la validación post-silicio no es una idea nueva, pero aquí hay un giro. Uso de la emulación (pre-silicio) para elegir estructuras de observación de depuración para instrumentar en silicio. Paul Cunningham (GM, Verificación en Cadence), Raúl Camposano (Silicon Catalyst, emprendedor, ex director de tecnología de Synopsys) y yo continuamos nuestra serie sobre ideas de investigación. Como siempre, los comentarios son bienvenidos.

![]()

La innovación

La elección de este mes es Infraestructura de emulación para la evaluación de afirmaciones de hardware para validación post-silicio. El artículo se presentó en IEEE Transactions on VLSI de 2017. Los autores son de la Universidad McMaster, Hamilton, ON, Canadá.

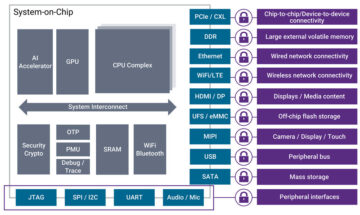

Los autores distinguen entre errores lógicos y eléctricos post-silicio y dedican su atención en este artículo a los errores eléctricos, detectables mediante cambios de bits en flops. Su enfoque consiste en determinar un conjunto óptimo de afirmaciones en el análisis previo al silicio. Luego los implementan en silicio para respaldar la depuración post-silicio. El análisis previo al silicio es similar a los fallos en los análisis de seguridad, inyectando fallos en los fallos correspondientes a errores eléctricos, como se insinúa en el artículo. Generan una lista de candidatos de afirmaciones mediante síntesis de afirmaciones; El núcleo de su innovación es proporcionar un método para calificar estas afirmaciones según la eficacia de cada una de ellas a la hora de detectar múltiples fallos.

La generación de entradas es aleatoria y analiza las fallas inyectadas (tratadas como transitorias) en secuencia. Permiten un número de ciclos especificado por el usuario para la detección por falla. En una fase posterior, miden la efectividad utilizando dos técnicas de cobertura diferentes. Para la cobertura de flip-flop, cuentan una afirmación si detecta un error inyectado en cualquier flop. En la cobertura de bit-flip, puntúan las afirmaciones por el número de errores detectados en flops separados. Estas métricas, junto con las estimaciones de área, las utilizan (alternativamente) para seleccionar qué afirmaciones preferidas.

Punto de vista de pablo

Este documento combina muy bien con nuestro Blog de agosto de 2020 sobre detección rápida de errores (QED). QED acelera la detección de errores funcionales post-silicio, donde este blog se centra en la detección de errores eléctricos post-silicio. El artículo es de fácil lectura, aunque ayuda leer primero la referencia [23].

Los errores eléctricos son difíciles de detectar y, aun así, son difíciles de replicar y encontrar la causa física subyacente. Los autores proponen un método, a través de lógica incorporada, para detectar cuándo dichos errores hacen que un flop cambie a un valor incorrecto (no profundizan más que encontrar estos cambios).

El corazón del artículo y su referencia complementaria [23] es un método de varios pasos para crear y sintetizar esta lógica de detección. Comienza con las propiedades mineras del diseño como afirmaciones temporales utilizando el herramienta mina de oro. Clasifican las afirmaciones basándose en una estimación de su capacidad para detectar cambios de bits y una estimación del costo del área/cableado para implementar en silicio. La clasificación se basa en ejecutar muchas simulaciones previas al silicio con afirmaciones candidatas, inyectar errores de inversión de bits y contar las inversiones detectadas por afirmaciones. En el artículo original utilizaron simulación lógica, aquí aceleran estas simulaciones asignando el diseño a una placa Altera FPGA.

Me gusta cómo reúnen varias innovaciones en un método coherente para la detección de inversión de bits post-silicio: minería de afirmaciones, síntesis de afirmaciones y una elegante función de clasificación para la selección de afirmaciones. Sin embargo, la sección de resultados del artículo indica que detectar cambios de bits en un n% de los flip-flops requiere aproximadamente un aumento del n% en el área de diseño. Esto parece un desafío para una aplicación comercial, especialmente porque solo ayuda a encontrar errores eléctricos. Potencialmente, se podría lograr un resultado similar clonando el cono lógico que impulsa un flip-flop y luego comparar la salida de esta lógica clonada con la lógica original. Esto parecería generar una sobrecarga de área similar a su método, en el límite de clonar todo el diseño (es decir, 100% de sobrecarga de área) para detectar cambios en el 100% de los fracasos en el diseño.

La mirada de Raúl

El documento es autónomo y contiene bastantes detalles. Los autores realizaron experimentos para 3 circuitos secuenciales ISCAS (aproximadamente 12K puertas, 2000 FF). Los experimentos de preparación inyectan 256 errores por flip-flop y utilizan todas las afirmaciones generadas por GoldMine. Debido a la capacidad limitada de la FPGA, los autores dividieron las ejecuciones en 45 "sesiones" para un circuito. Los resultados muestran, incluso con 45 sesiones, una aceleración en el análisis respecto a la simulación de 20 a 500 veces (sólo hasta 8 inyecciones de error porque la simulación se vuelve demasiado lenta, 105 h). La cobertura Flip-Flop máxima alcanzable es del 55%, 89% y 99% para los 3 circuitos. El número de afirmaciones extraídas controla la cobertura.

La ejecución con aserciones seleccionadas (correspondientes a una sobrecarga de área del 5-50%) y 1-256 inyecciones da como resultado una cobertura de bits del 2.2%-34%. La mayor parte del tiempo, el minero de afirmaciones funcionó durante 228 horas. Una cosa que me confundió son sus datos sobre tiempos de ejecución versus errores inyectados. El aumento parece razonable (lineal) en la simulación. Pero en la emulación salta enormemente, de 0.045h a 5.4h para un aumento de 2 a 8 inyecciones de error. Me gustaría tener más explicaciones sobre este punto.

Este es un documento metodológico. Me gusta que prácticamente cada paso se pueda sustituir por una herramienta comercial. Junto con el uso de una placa FPGA grande (como emulador), la metodología se amplía. Por supuesto, las metodologías son muy difíciles de comercializar, ¡pero es una buena aplicación para la tecnología existente!

Mi vista

El método para explorar una técnica de análisis de seguridad para la depuración post-silicio es intrigante. Una idea novedosa, aunque conduce a un resultado poco práctico para su aplicación comercial.

Comparte esta publicación a través de: Fuente: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Todos

- análisis

- Aplicación

- Reservada

- Autorzy

- Poco

- Blog

- tablero

- Error

- loco

- Cadencia

- Capacidad

- lucha

- Causar

- completo

- continue

- CTO

- datos

- Diseño

- detalle

- Detección

- conducción

- Eficaz

- Emprendedor

- estima

- feria

- Nombre

- FPGA

- función

- -

- GM

- Materiales

- esta página

- Cómo

- HTTPS

- idea

- IEEE

- aumente

- EN LA MINA

- Innovation

- IT

- large

- líder

- Limitada

- Lista

- medir

- Métrica

- Minería

- Papel

- ofrece

- la investigación

- Resultados

- correr

- Safety

- seleccionado

- Serie

- set

- simulación

- dividido

- SOPORTE

- equipo

- Transacciones

- torcedura

- universidad

- propuesta de

- Verificación

- Versus