Cuando leo la prensa popular y técnica cada semana, a menudo veo artículos sobre sistemas informáticos pirateados, y aquí hay solo algunas vulnerabilidades de esta semana:

Aquí en SemiWiki tenemos muchos ingenieros responsables del hardware, software, firmware y seguridad de SoC, entonces, ¿cuáles son las mejores prácticas para hacer que sus sistemas electrónicos nuevos o existentes sean más resistentes contra ataques y menos vulnerables?

Gajinder Panesar y Tim Ramsdale son dos expertos de Siemens EDA y Agile Analog, respectivamente, y se unieron para escribir un informe técnico de 15 páginas, "El panorama evolutivo de las vulnerabilidades de SoC y las amenazas analógicas. " Compartiré la esencia de lo que aprendí al leer esto.

Vulnerabilidades

Una premisa de seguridad es que depender solo de las actualizaciones de software para parchear las vulnerabilidades no es suficiente, por lo que se debe considerar agregar seguridad como parte del diseño del hardware. Incluso hay un proyecto de código abierto llamado AbiertoTitan, para ayudarlo a crear un diseño de referencia transparente y de alta calidad y pautas de integración para chips de raíz de confianza (RoT) de silicio. Con un RoT basado en hardware, solo se puede ejecutar el firmware comparado con una firma conocida, deteniendo los intentos de cargar cualquier firmware pirateado.

Los piratas informáticos se están volviendo lo suficientemente creativos e ingeniosos como para examinar las claves secretas en un algoritmo RSA al realizar mediciones de hardware, notando pequeñas variaciones en cómo se ejecutan las operaciones, también conocido como ataque de canal lateral. A continuación se muestran cuatro porciones de multiplicación por las flechas violetas, luego los picos negativos son parte de la reducción modular y cuadrática en el algoritmo.

Las pistas de seguridad se pueden revelar examinando varias cosas:

- Actividad de caché

- Pipelines de ejecución

- Valores electromagnéticos (EM)

- Variaciones de voltaje

- Variaciones actuales

Otro ejemplo de un ataque de canal lateral tiene al pirata informático tratando de adivinar uno de los bytes de clave, y alrededor de la región 350 encontraron un byte de clave correcto.

Los objetivos de la piratería incluyen infraestructura 5G, servidores de borde, dispositivos IoT, computación en la nube, vehículos autónomos, robótica industrial. Los piratas informáticos utilizan métodos estadísticos para medir los dispositivos electrónicos, lo que proporciona pistas sobre las vulnerabilidades de seguridad. Una contramedida es que el equipo de diseño de hardware agregue ruido eléctrico aleatorio.

Otra técnica que usan los piratas informáticos es fallar intencionalmente la fuente de alimentación en un momento específico, lo que luego puede convertir un bit almacenado en un estado inseguro, según lo documentado por la compañía de seguridad alemana. Nivel abajo. Incluso algunos procesadores más antiguos tenían un exploit donde un hacker usaba códigos de operación ilegales, lo que a su vez puso al procesador en un estado vulnerable.

La temperatura es otra técnica en la que un atacante puede ejecutar un SoC a una temperatura más alta o más baja que la especificada, para alterar el estado interno o incluso extraer claves privadas de una función físicamente no clonable (PUF).

Un atacante puede usar cambios de voltaje en el riel de suministro para ralentizar o acelerar la lógica, provocando que los bits internos cambien y se alcancen estados ilegales.

Si un pirata informático tiene acceso físico a su sistema electrónico, el que controle directamente las entradas del reloj cambiando el ciclo de trabajo, o introduciendo fallas, cambiará la lógica interna. chipwhisperer es una empresa con un sistema de código abierto para exponer las debilidades de los sistemas embebidos, utilizando análisis de potencia de canal lateral e inyección de fallas.

La inyección de fallas mediante radiación electromagnética (EM) es una técnica utilizada por ChipShouter, pero tendrían que sincronizarse con precisión con los bordes del reloj interno para crear una falla repetible. Incluso el uso de una luz láser en un paquete de CI sin tapa puede forzar errores internos para un SoC.

Contramedidas a las vulnerabilidades

- Fallos del reloj: fuente generada internamente para la comparación.

- Fallos de energía: detectores de apagones

- Ataque de temperatura: sensores de temperatura

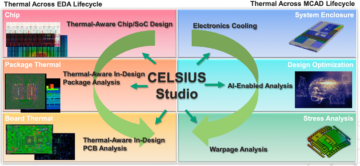

En Siemens EDA ofrecen un producto llamado Análisis integrado de Tessente incorpora monitores de hardware en su SoC, luego se comunica con una arquitectura basada en mensajes. Al agregar IP de seguridad de hardware de Agile Analog, se pueden verificar el reloj, el voltaje y la temperatura:

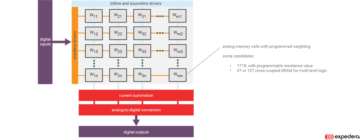

Estos monitores pueden detectar una vulnerabilidad, luego los análisis integrados pueden informar y decidir la respuesta de seguridad adecuada. La combinación de análisis integrado e IP de seguridad que se muestra en un diagrama:

Resumen

El gran poder y los beneficios del diseño de SoC están siendo atacados por piratas informáticos, por lo que depende de la comunidad de diseño adoptar medidas proactivas para fortalecer el nivel de seguridad de sus nuevos productos. Lo que Siemens EDA y Agile Analog han creado es un marco de hardware digital y analógico integrado, para permitir la detección de amenazas cibernéticas y un medio para tomar las medidas adecuadas, en tiempo real.

Sí, esto significa más trabajo para su equipo de diseño, pero sus clientes valorarán más un SoC más seguro. Tampoco tiene que empezar de cero, porque Siemens EDA y Agile Analog han hecho el trabajo de base por usted.

Para leer el texto completo Libro blanco de 15 páginas, visite esta página y proporcione algunos detalles sobre usted.

Blogs relacionados

Comparte esta publicación a través de: Fuente: https://semiwiki.com/eda/301364-soc-vulnerabilities/

- 5G

- de la máquina

- la columna Acción

- algoritmo

- análisis

- Analytics

- arquitectura

- en torno a

- ataques

- autónomo

- vehículos autónomos

- MEJOR

- y las mejores prácticas

- Poco

- build

- el cambio

- Cheques

- Papas fritas

- Soluciones

- la computación en nube

- vibrante e inclusiva

- compañía

- informática

- Estudio

- Clientes

- ciber

- Diseño

- Detección

- Dispositivos

- digital

- Southern Implants

- certificados

- expertos

- Explotar

- Marco conceptual

- ser completados

- función

- falla

- maravillosa

- orientaciones

- pirata informático

- los piratas informáticos

- la piratería

- Materiales

- Cómo

- HTTPS

- ilegal

- industrial

- EN LA MINA

- integración

- IOT

- dispositivos iot

- IP

- IT

- Clave

- claves

- láser

- aprendido

- Nivel

- luz

- carga

- Realizar

- medir

- modulares

- nuevos diseños y productos

- ruido

- LANZAMIENTO

- habiertos

- de código abierto

- Operaciones

- solicite

- Papel

- Patch

- Popular

- industria

- prensa

- privada

- Llaves privadas

- Producto

- Productos

- proyecto

- La radiación

- Carril

- Reading

- reporte

- respuesta

- robótica

- Ejecutar

- EN LINEA

- sentido

- Compartir

- Siemens

- chica

- So

- Software

- velocidad

- comienzo

- Estado

- Zonas

- suministro

- te

- Todas las funciones a su disposición

- Técnico

- amenazas

- equipo

- Confía en

- Actualizaciones

- propuesta de

- Vehículos

- Vulnerabilidades

- Vulnerable

- semana

- detalles de la moneda

- Actividades: