Achronix es conocido por sus soluciones FPGA de alto rendimiento. En esta publicación, exploraré el Speedster7T FPGA. Esta familia de FPGA está optimizada para cargas de trabajo de gran ancho de banda y elimina los cuellos de botella en el rendimiento con una arquitectura innovadora. Construida sobre el proceso FinFET de 7 nm de TSMC, la familia ofrece un rendimiento de nivel ASIC al tiempo que conserva la capacidad de programación completa de un FPGA. Hay mucho que aprender sobre el Speedster7T. Achronix ahora tiene un video disponible que responderá muchas de esas preguntas. Hay un enlace a ese video y más por venir, pero primero veamos qué sucede cuando toma el Achronix Speedster7t FPGA para una prueba de manejo en el laboratorio.

Achronix es conocido por sus soluciones FPGA de alto rendimiento. En esta publicación, exploraré el Speedster7T FPGA. Esta familia de FPGA está optimizada para cargas de trabajo de gran ancho de banda y elimina los cuellos de botella en el rendimiento con una arquitectura innovadora. Construida sobre el proceso FinFET de 7 nm de TSMC, la familia ofrece un rendimiento de nivel ASIC al tiempo que conserva la capacidad de programación completa de un FPGA. Hay mucho que aprender sobre el Speedster7T. Achronix ahora tiene un video disponible que responderá muchas de esas preguntas. Hay un enlace a ese video y más por venir, pero primero veamos qué sucede cuando toma el Achronix Speedster7t FPGA para una prueba de manejo en el laboratorio.

Steve Mensor, vicepresidente de ventas y marketing de Achronix, presenta el video. Steve ha estado con Achronix durante casi diez años y pasó 21 años en Altera antes de eso. Ciertamente sabe mucho sobre FPGA: diseño y aplicación. Steve comienza describiendo algunos de los elementos de la arquitectura innovadora mencionada anteriormente. Hay mucha capacidad dedicada a bordo del Speedster7T. Esto incluye:

- SerDes de 112 Gbps

- 400G Ethernet

- PCIe Gen5

- GDDR6 funcionando a 4 Tbps

- DDR 4 funcionando a 3,200 Mbps

- Un procesador de aprendizaje automático patentado

- Red 2D en chip (NoC)

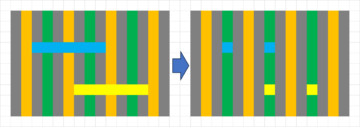

El procesador de aprendizaje automático patentado ofrece una gran cantidad de funciones, incluidas operaciones de punto flotante, punto flotante de bloque y enteros. El 2D NoC es una capacidad nueva en la industria para FPGA de Achronix. El NoC puede enrutar datos desde cualquiera de las interfaces de alta velocidad a la estructura central de FPGA a 2 GHz sin consumir ninguno de los recursos lógicos de FPGA. Toda esta tecnología integrada le permite obtener un rendimiento de nivel ASIC en un FPGA.

Luego, Steve entrega la presentación a Katie Purcell, gerente de ingeniería de aplicaciones de Achronix. Katie ha estado con Achronix durante cuatro años. Antes de eso, fue diseñadora de ASIC. También pasó un tiempo en Xilinx. Katie es la que prueba el Speedster7t FPGA en el laboratorio y definitivamente está a la altura del desafío.

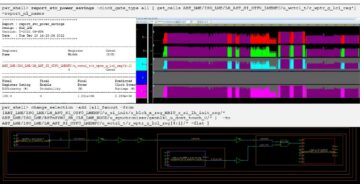

Katie lleva al espectador al laboratorio de Achronix, donde se realiza la validación y caracterización del Speedster7T. La demostración que presenta Katie muestra el dispositivo que ejecuta un tráfico Ethernet de 400 G en el Tarjeta aceleradora Achronix VectorPath. Katie comienza resumiendo los elementos clave de la demostración, que incluyen:

- Interfaz externa 8X50G

- Interfaz única de 400G en el subsistema ethernet

- Datos divididos en cuatro flujos separados en el NoC 2D

- Cada flujo se procesa de forma independiente

Katie pasa algún tiempo en el 2D NoC. Ella señala que esta capacidad hace que el diseño sea más simple y más fácil de cerrar el tiempo. Este NoC 2D único apareció varias veces durante la demostración. Vale la pena indagar un poco más para entenderlo. Achronix presentó previamente un seminario web sobre esta capacidad única que fue cubierto en SemiWiki , que son 5 razones por las que una SmartNIC reconfigurable de alto rendimiento exige un NoC 2D. La buena noticia es que ya está disponible una repetición de este seminario web muy informativo. Puedes verlo aqui.

Katie lo guía a través de una mirada detallada de lo que sucede dentro del dispositivo Speedster7T mientras procesa los paquetes de datos. Conocer esos detalles ayuda a comprender la facilidad de configuración y la precisión entregada que se muestra durante la demostración. Si cree que un dispositivo único como este podría ayudar a su proyecto de diseño, le recomiendo que vea la demostración. Es breve, pero muy útil. Puede acceda al video de demostración aquí.

Ahora ya sabe cómo probar el Achronix Speedster7t FPGA en el laboratorio. Puedes conocer más detalles al respecto familia FPGA única aquí.

Comparte esta publicación a través de: Fuente: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- acelerador

- Todos

- Aplicación

- arquitectura

- ASIC

- Poco

- tablero

- Reto

- chip

- viniendo

- datos

- Diseño

- Designer

- Ingeniería

- material

- familia

- Nombre

- FPGA

- ser completados

- candidato

- Alta

- Cómo

- Como Hacer

- HTTPS

- Incluye

- originales

- IT

- Clave

- APRENDE:

- aprendizaje

- LINK

- máquina de aprendizaje

- Marketing

- del sistema,

- noticias

- Operaciones

- actuación

- proyecto

- razones

- Recursos

- Ruta

- correr

- ventas

- En Corto

- Soluciones

- Tecnología

- test

- equipo

- tráfico

- Video

- Ver ahora

- Webinar

- QUIENES

- valor

- X

- años