Viikolla 19. huhtikuutath, Linley Group piti kevään prosessorikonferenssin 2021. Linley Groupilla on maine kutsua koolle erinomaisia konferensseja. Ja tämän vuoden kevätkonferenssi ei ollut poikkeus. Eri yritykset pitivät useita erittäin informatiivisia keskusteluja, jotka päivittivät yleisöä alan uusimmasta tutkimus- ja kehitystyöstä. Esitykset oli luokiteltu kahdeksaan eri aihepiiriin. Aihealueita olivat Edge AI, Embedded SoC Design, Scaling AI Training, AI SoC Design, Network Infrastructure for AI and 5G, Edge AI Software, Signal Processing and Efficient AI Inference.

Tekoäly (AI) teknologiana on saanut viime vuosina paljon huomiota ja investointeja. Konferenssi heijasti sitä varmasti tekoälyyn liittyvien aiheluokkien määrässä. Laajemmassa tekoälyn luokassa Edge AI oli aihe, jolla oli epäoikeudenmukainen osuus esityksistä ja perustellusti. Reunalaskennan kasvu on nopeaa IoT-, 5G- ja muiden matalaviiveisten vaatimussovellusten ohjaamana.

Yksi Edge AI -luokan esityksistä oli otsikoitu "RISC-V-vektorilaajennusten parantaminen suorituskyvyn parantamiseksi ML-työkuormilla." Puheen piti SiFive, Inc: n insinööri- ja tuotepäällikkö Chris Lattner. Chris kertoi vahvasti, miksi SiFiven RISC-V-vektorilaajennuksiin perustuva ratkaisu sopii erinomaisesti tekoälyohjattuihin sovelluksiin. Seuraava on minun otokseni.

Markkinavaatimukset:

Niin nopeasti kuin reunalaskennan markkinat kasvavat, myös näiden sovellusten suorituskyky ja tehovaatimukset ovat yhä vaativampia. Monet näistä sovelluksista ovat tekoälyohjattuja ja kuuluvat koneoppimisen (ML) työkuormien luokkaan. Tekoälyn käyttöönotto työntää käsittelyvaatimukset enemmän kohti tietojen manipulointia kuin yleiskäyttöistä tietojenkäsittelyä. Syvä oppiminen perustuu ML-malleihin ja käsittää suurten tietomäärien käsittelyn. Kun ML-mallit kehittyvät nopeasti, ihanteellinen ratkaisu olisi optimoida: suorituskyky, teho, uusien ML-mallien sisällyttämisen helppous ja tuloksena olevien laitteisto- ja / tai ohjelmistomuutosten laajuus.

RISC-V Vector -etu:

RISC-V-arkkitehtuurin antaneen aloitteen alkuperäinen motivaatio on kokeilu. Kokeilemalla sirumallien kehittämistä, jotka tuottavat parempaa suorituskykyä Mooren lain odotetun hidastumisen edessä. RISC-V perustuu ajatukseen siitä, että pystymme räätälöimään tiettyjä pelimerkkejä, joissa voit valita käyttämäsi komentosarjalaajennukset. Vektorilaajennukset mahdollistavat minkä tahansa pituisten vektorien käsittelyn käyttämällä toimintoja, jotka käsittelevät kiinteän pituisia vektoreita. Vektorikäsittelyn avulla nykyiset ohjelmistot voidaan suorittaa ilman uudelleenkääntämistä, kun laitteistoa päivitetään enemmän ALU: iden ja muiden toiminnallisten yksiköiden muodossa. Merkittävää edistystä on tapahtunut vakiintuneen laitteistopohjan ja ekosysteemin, kuten kääntäjätekniikoiden, tukemisessa.

RISC-V voidaan optimoida tietylle verkkotunnukselle tai sovellukselle mukautettujen laajennusten avulla. Avoimen vakiokäskyjoukkoarkkitehtuurin RISC-V-käyttäjillä on paljon joustavuutta toimittajan valitsemisessa sirun suunnittelutarpeisiinsa.

SiFiven tarjous:

SiFive on parantanut RISC-V Vector -etua lisäämällä uusia vektorilaajennuksia monien eri hermoverkkomallien suorittamisen nopeuttamiseksi. Katso kuvasta 1 esimerkki sellaisesta nopeutuksesta, joka voidaan saavuttaa käyttämällä SiFiven lisäosa-laajennuksia verrattuna vain RISC-V: n perusvektorilaajennuksiin. Sen Intelligence X280 -ratkaisu on monisydäminen RISC-V Vector -ratkaisu (laitteisto ja ohjelmisto), jonka avulla asiakkaiden on helppo toteuttaa optimoituja Edge AI -sovelluksia. Ratkaisua voidaan käyttää myös datakeskussovellusten toteuttamiseen.

Kuva 1:

SiFive-etu:

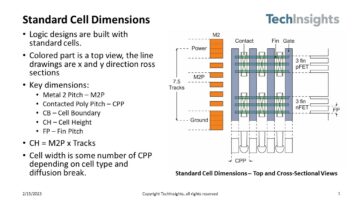

- SiFiven Intelligence X280 -ratkaisu tukee täysin avoimen lähdekoodin TensorFlow- ja TensorFlow Lite -alustoja koneoppimiseen (katso kuva 2)

- SiFive tarjoaa helpon tavan siirtää asiakkaan nykyinen koodi, joka perustuu muihin arkkitehtuureihin, RISC-V Vector -arkkitehtuuriin. Esimerkiksi SiFive voi kääntää ARM-neonkoodin RISC-V V -kokoonpanokoodiksi

- SiFive antaa asiakkailleen mahdollisuuden tutkia mukautettujen laajennusten lisäämistä RISC-V-toteutuksiinsa

- SiFive laajentaa OpenFive-liiketoimintayksikönsä kautta räätälöityjä sirujen toteutuspalveluja toimialakohtaisten piitarpeiden tyydyttämiseksi

Kuva 2:

Yhteenveto:

Pähkinänkuoressa SiFive-asiakkaat voivat helposti ja nopeasti toteuttaa sovelluksensa riippumatta siitä, liittyykö sovelluksiin Edge AI -kuormia vai perinteisiä palvelinkeskustyyppisiä kuormia. Jos olet kiinnostunut hyötymään SiFiven ratkaisuista ML-kuormituksesi nopeuttamiseksi, suosittelen, että rekisteröidyt ja kuuntelet Chrisin koko puhe ja keskustele sitten SiFiven kanssa keinoista hyödyntää heidän erilaisia tarjouksiaan tuotteidesi kehittämisessä.

Jaa tämä viesti: Lähde: https://semiwiki.com/ip/sifive/299157-enhancing-risc-v-vector-extensions-to-accelerate-performance-on-ml-workloads/

- 2021

- 5G

- Lisäosan

- Hyväksyminen

- Etu

- AI

- AI hyväksyminen

- AI-koulutus

- Hakemus

- sovellukset

- huhtikuu

- arkkitehtuuri

- ARM

- yleisö

- liiketoiminta

- siru

- sirut

- koodi

- Yritykset

- tietojenkäsittely

- Konferenssi

- konferenssit

- Asiakkaat

- tiedot

- Data Center

- syvä oppiminen

- Malli

- kehittää

- Kehitys

- ajanut

- ekosysteemi

- reuna

- reunan tietojenkäsittely

- Tekniikka

- teloitus

- laajennukset

- Kasvot

- FAST

- Kuva

- sovittaa

- Joustavuus

- muoto

- koko

- general

- suuri

- Ryhmä

- Kasvava

- Kasvu

- Tarvikkeet

- HTTPS

- ajatus

- Inc.

- teollisuus

- Infrastruktuuri

- aloite

- Älykkyys

- investointi

- Esineiden internet

- IT

- suuri

- uusin

- Laki

- oppiminen

- Vaikutusvalta

- koneoppiminen

- Manipulointi

- markkinat

- Matters

- ML

- Neon

- verkko

- hermo-

- neuroverkkomallien

- tarjoamalla

- tarjoukset

- avata

- Muut

- suorituskyky

- Platforms

- teho

- Esitykset

- puheenjohtaja

- Tuotteet

- Tuotteemme

- vaatimukset

- tutkimus

- tutkimus ja kehitys

- ajaa

- skaalaus

- Palvelut

- setti

- Jaa:

- So

- Tuotteemme

- Ratkaisumme

- kevät

- tuki

- Tukee

- Neuvottelut

- Technologies

- Elektroniikka

- tensorflow

- Aloite

- koulutus

- us

- Käyttäjät

- viikko

- sisällä

- Referenssit

- vuotta

- tuotto