Piin jälkeisen validoinnin instrumentointi ei ole uusi idea, mutta tässä on käänne. Käyttämällä (pre-pii) emulointia valitaksesi virheenkorjaushavainnointirakenteet instrumentille piin sisällä. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, yrittäjä, entinen Synopsys CTO) ja minä jatkamme tutkimusideoiden sarjaamme. Kuten aina, palaute on tervetullutta.

![]()

Innovaatio

Tämän kuukauden valinta on Emulointiinfrastruktuuri laitteistoväitteiden arvioimiseksi silikonin jälkeistä validointia varten. Paperi esiteltiin vuoden 2017 IEEE Transactions -tapahtumassa VLSI:llä. Kirjoittajat ovat McMaster Universitystä, Hamilton, ON, Kanada

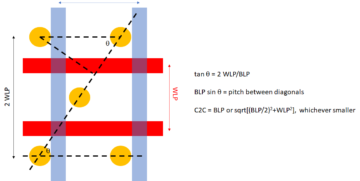

Kirjoittajat erottavat piin jälkeiset loogiset ja sähköiset virheet ja kiinnittävät tässä artikkelissa huomionsa sähköisiin virheisiin, jotka voidaan havaita floppien bittikäänteillä. Heidän lähestymistapansa on määrittää optimaalinen joukko väitteitä esipiianalyysissä. Ne sitten toteuttavat piin jälkeisen virheenkorjauksen tueksi. Esipiianalyysi on samankaltainen kuin turvallisuusanalyyseissä tapahtuva vika, jossa sähkövirheitä vastaavia vikoja syötetään floppiin, kuten paperissa vihjataan. Ne luovat ehdokasluettelon väitteistä väitösynteesin avulla; heidän innovaationsa ydin on tarjota menetelmä näiden väitteiden arvioimiseksi sen mukaan, kuinka tehokkaita kukin on useiden vikojen havaitsemisessa.

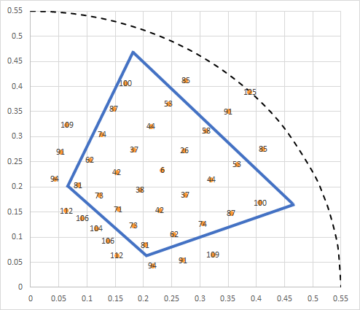

Tulon generointi on satunnaista, ja se analysoi syötetyt viat (käsitelty ohimenevinä) peräkkäin. Ne mahdollistavat käyttäjän määrittämän jaksojen lukumäärän vian havaitsemiseksi. Myöhemmässä vaiheessa ne mittaavat tehokkuutta käyttämällä kahta eri peittotekniikkaa. Flip-flop-kattavuuden osalta he laskevat väitteen, jos se havaitsee syötetyn virheen missä tahansa flopilla. Bit-flip-peittoalueella ne arvostavat eri flopeissa havaittujen virheiden määrää. Näitä mittareita yhdessä aluearvioiden kanssa he käyttävät (vuorotellen) valitsemaan ensisijaiset väitteet.

Paavalin näkemys

Tämä paperi sopii hyvin meidän kanssamme Elokuun 2020 blogi nopeasta virheiden havaitsemisesta (QED). QED nopeuttaa piin jälkeistä toiminnallisten vikojen havaitsemista, jossa tämä blogi keskittyy piin jälkeiseen sähkövikojen havaitsemiseen. Paperi on helppolukuinen, vaikka se auttaakin lukemaan viitteen [23].

Sähkövikoja on vaikea havaita, ja silloinkin niitä on vaikea jäljitellä ja löytää taustalla oleva fyysinen syy. Kirjoittajat ehdottavat sulautetun logiikan avulla menetelmää, jolla havaitaan, milloin tällaiset virheet saavat flopin kääntymään väärään arvoon (he eivät kaivaudu syvemmälle kuin näiden käänteiden löytäminen).

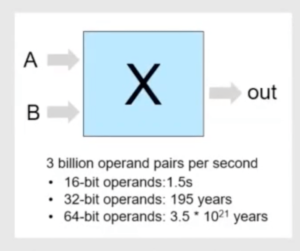

Paperin ydin ja sen oheisviite [23] on monivaiheinen menetelmä tämän tunnistuslogiikan luomiseksi ja syntetisoimiseksi. Se alkaa suunnittelun louhintaominaisuuksista ajallisina väitteinä käyttäen GoldMine työkalu. Ne luokittelevat väitteet, jotka perustuvat arvioon heidän kyvystään havaita bitin käännöksiä ja arvioon piin käyttöönotettavan alueen/johdotuskustannuksista. Luokittelu perustuu monien piitä edeltävien simulaatioiden suorittamiseen ehdokkaiden väitteillä, bitinvaihtovirheiden lisäämiseen ja havaittujen kääntymisten laskemiseen väitteiden perusteella. Alkuperäisessä artikkelissa he käyttivät logiikkasimulaatiota, tässä he nopeuttavat näitä simulaatioita kartoittamalla suunnittelun Altera FPGA -levylle.

Pidän siitä, kuinka he yhdistävät useita innovaatioita yhtenäiseksi menetelmäksi piibitin jälkeisen käänteen havaitsemiseksi: väitteiden louhinta, väitesynteesi ja tyylikäs ranking-toiminto väitteiden valinnassa. Paperin tulososio kuitenkin osoittaa, että bittikääntojen havaitseminen n %:ssa kiikkuista vaatii suunnilleen n %:n lisäyksen suunnittelualueeseen. Tämä näyttää haastavalta kaupallisessa käytössä, varsinkin kun se auttaa vain löytämään sähkövikoja. Samanlainen tulos voitaisiin mahdollisesti saavuttaa kloonaamalla logiikkakartio, joka ohjaa flip-flopia, ja vertaa sitten tämän kloonatun logiikan tulosta alkuperäiseen logiikkaan. Tämä näyttäisi tuottavan samanlaisen alueen yläpuolella kuin heidän menetelmänsä, raja-kloonattaessa koko mallia (eli 100 % alueen yläpuolella) havaitakseen käännökset 100 %:ssa suunnittelun floppeista.

Raúlin näkemys

Paperi on itsenäinen ja sisältää melko paljon yksityiskohtia. Kirjoittajat suorittivat kokeita kolmelle ISCAS-peräkkäiselle piirille (noin 3K portit, 12 FF). Valmistelukokeet syöttävät 2000 virhettä per flip floppi ja käyttämällä kaikkia GoldMinen luomia väitteitä. FPGA:n rajoitetun kapasiteetin vuoksi kirjoittajien jako kestää 256 "istuntoa" yhdelle piirille. Tulokset osoittavat jopa 45 istunnolla 45-20-kertaisen analyysin kiihtyvyyden simulaatioon nähden (vain jopa 500 virheinjektiota, koska simulaatio hidastuu liian hitaasti, 8 tuntia). Suurin saavutettavissa oleva Flip-Flop-peitto on 105 %, 55 % ja 89 % kolmelle piirille. Louhittujen väitteiden määrä säätelee kattavuutta.

Ajaminen valituilla väitteillä (vastaa 5–50 %:n pinta-alaa) ja 1–256 injektiolla johtaa 2.2–34 % bittipeittoon. Suurimman osan ajasta kaivosmies juoksi 228 tuntia. Yksi asia, joka hämmensi minua, on heidän datansa ajoaikojen ja syötettyjen virheiden osalta. Lisäys näyttää kohtuulliselta (lineaariselta) simulaatiossa. Mutta emuloinnissa se hyppää massiivisesti, 0.045 tunnista 5.4 tuntiin, mikä lisää 2-8 virheinjektiota. Haluaisin lisäselvitystä tähän kohtaan.

Tämä on metodologiapaperi. Pidän siitä, että melkein jokainen askel voidaan korvata kaupallisella työkalulla. Yhdessä suuren FPGA-levyn käytön kanssa (emulaattorina) menetelmä skaalautuu. Menetelmiä on tietysti erittäin vaikea kaupallistaa, mutta se on mukava sovellus olemassa olevalle teknologialle!

Minun näkökulmani

Menetelmä turvallisuusanalyysitekniikan tutkimiseksi silikonin jälkeistä virheenkorjausta varten on kiehtova. Uusi idea, vaikka se johtikin kaupalliseen käyttöön jokseenkin epäkäytännölliseen tulokseen.

Jaa tämä viesti: Lähde: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Kaikki

- analyysi

- Hakemus

- ALUE

- Tekijät

- Bitti

- Uutiset ja media

- hallitus

- Vika

- Bugs

- kadenssi

- Koko

- paini

- Aiheuttaa

- kaupallinen

- jatkaa

- CTO

- tiedot

- Malli

- yksityiskohta

- Detection

- ajo

- Tehokas

- Yrittäjä

- arviot

- oikeudenmukainen

- Etunimi

- FPGA

- toiminto

- Gates

- GM

- Tarvikkeet

- tätä

- Miten

- HTTPS

- ajatus

- IEEE

- Kasvaa

- Infrastruktuuri

- Innovaatio

- IT

- suuri

- johtava

- rajallinen

- Lista

- mitata

- Metrics

- kaivos-

- Paperi

- ehdottaa

- tutkimus

- tulokset

- juoksu

- Turvallisuus

- valittu

- Sarjat

- setti

- simulointi

- jakaa

- tuki

- aika

- Liiketoimet

- twist

- yliopisto

- arvo

- Vahvistus

- Vastaan