Dans la semaine du 19 avrilth, Linley Group a tenu sa Spring Processor Conference 2021. Le Linley Group a la réputation d'organiser d'excellentes conférences. Et la conférence du printemps de cette année n'a pas fait exception. Il y a eu un certain nombre de conférences très informatives de diverses entreprises qui ont informé le public des derniers travaux de recherche et développement en cours dans l'industrie. Les présentations avaient été classées sous huit sujets différents. Les sujets étaient Edge AI, Embedded SoC Design, Scaling AI Training, AI SoC Design, Network Infrastructure for AI et 5G, Edge AI Software, Signal Processing et Efficient AI Inference.

L’intelligence artificielle (IA) en tant que technologie a suscité beaucoup d’attention et d’investissements ces dernières années. La conférence l’a certainement reflété dans le nombre de catégories de sujets liés à l’IA. Dans la catégorie plus large de l’IA, Edge AI était un sujet qui faisait l’objet d’une part injuste de présentations et à juste titre. L’Edge Computing connaît une croissance rapide tirée par l’IoT, la 5G et d’autres applications nécessitant une faible latence.

L'une des présentations dans la catégorie Edge AI était intitulée « Amélioration des extensions vectorielles RISC-V pour accélérer les performances des charges de travail de ML. » La conférence a été donnée par Chris Lattner, président de l'ingénierie et des produits chez SiFive, Inc. Chris a expliqué avec force pourquoi la solution basée sur les extensions vectorielles RISC-V de SiFive convient parfaitement aux applications basées sur l'IA. Ce qui suit est mon point de vue.

Exigences du marché :

À mesure que le marché de l'informatique de pointe se développe, les exigences en matière de performances et de puissance de ces applications deviennent également de plus en plus exigeantes. Beaucoup de ces applications sont pilotées par l’IA et entrent dans la catégorie des charges de travail d’apprentissage automatique (ML). Et l’adoption de l’IA pousse les besoins de traitement davantage vers la manipulation de données plutôt que vers l’informatique à usage général. L'apprentissage profond est à la base des modèles ML et implique le traitement de larges tableaux de données. Avec l'évolution rapide des modèles ML, une solution idéale serait celle qui optimise les performances, la puissance, la facilité d'intégration des modèles ML émergents et la portée des modifications matérielles et/ou logicielles qui en résultent.

Avantage du vecteur RISC-V :

La motivation originale derrière l'initiative qui nous a donné l'architecture RISC-V est l'expérimentation. Expérimenter pour développer des conceptions de puces offrant de meilleures performances face au ralentissement attendu de la loi de Moore. RISC-V repose sur l'idée de pouvoir créer des puces particulières sur mesure sur lesquelles vous pouvez choisir les extensions de jeu d'instructions que vous utilisez. Les extensions vectorielles permettent de traiter des vecteurs de n'importe quelle longueur à l'aide de fonctions qui traitent des vecteurs de longueurs fixes. Le traitement vectoriel permet aux logiciels existants de s'exécuter sans recompilation lorsque le matériel est mis à niveau sous la forme de davantage d'ALU et d'autres unités fonctionnelles. Des progrès significatifs ont été réalisés en termes de base matérielle établie et d'écosystème de support tel que les technologies de compilateur.

RISC-V peut être optimisé pour un domaine ou une application particulière via des extensions personnalisées. En tant qu'architecture de jeu d'instructions standard ouverte, les utilisateurs de RISC-V bénéficient d'une grande flexibilité dans le choix d'un fournisseur pour leurs besoins de conception de puces.

L'offre de SiFive :

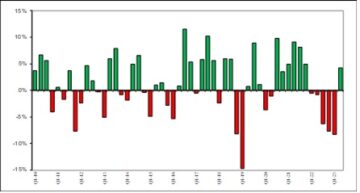

SiFive a amélioré l'avantage RISC-V Vector en ajoutant de nouvelles extensions vectorielles pour accélérer l'exécution de nombreux modèles de réseaux neuronaux différents. Reportez-vous à la figure 1 pour voir un exemple du type d'accélération qui peut être obtenu en utilisant les extensions complémentaires de SiFive par rapport à l'utilisation uniquement des extensions vectorielles de base de RISC-V. Sa solution Intelligence X280 est une solution RISC-V Vector multicœur (matérielle et logicielle) pour permettre à ses clients de mettre en œuvre facilement des applications Edge AI optimisées. La solution peut également être utilisée pour mettre en œuvre des applications de centre de données.

Figure 1:

Avantage SiFive :

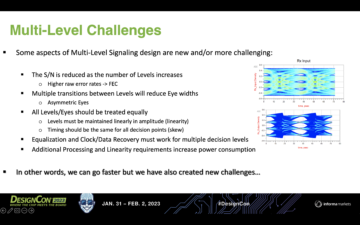

- La solution Intelligence X280 de SiFive prend entièrement en charge les plates-formes open source TensorFlow et TensorFlow Lite pour l'apprentissage automatique (voir Figure 2)

- SiFive fournit un moyen simple de migrer le code existant du client basé sur d'autres architectures vers l'architecture RISC-V Vector. Par exemple, SiFive peut traduire le code ARM Neon en code assembleur RISC-V V

- SiFive permet à ses clients d'explorer l'ajout d'extensions personnalisées à leurs implémentations RISC-V

- SiFive, par l'intermédiaire de son unité commerciale OpenFive, étend ses services de mise en œuvre de puces personnalisées pour répondre aux besoins en silicium spécifiques à un domaine.

Figure 2:

Résumé :

En un mot, les clients de SiFive peuvent facilement et rapidement mettre en œuvre leurs applications, que celles-ci impliquent des charges de travail Edge AI ou des charges de travail de type centre de données traditionnel. Si vous souhaitez bénéficier des solutions SiFive pour accélérer les performances de vos charges de travail ML, je vous recommande de vous inscrire et d'écouter L'intégralité du discours de Chris puis discutez avec SiFive des moyens de tirer parti de leurs différentes offres pour développer vos produits.

Partagez cet article via: Source : https://semiwiki.com/ip/sifive/299157-enhancing-risc-v-vector-extensions-to-accelerate-performance-on-ml-workloads/

- 2021

- 5G

- Choisir

- Adoption

- Avantage

- AI

- Adoption de l'IA

- Formation IA

- Application

- applications

- Avril

- architecture

- BRAS

- public

- la performance des entreprises

- puce

- chips

- code

- Sociétés

- informatique

- Congrès

- conférences

- Clients

- données

- Centre de données

- l'apprentissage en profondeur

- Conception

- développer

- Développement

- entraîné

- risque numérique

- Edge

- informatique de pointe

- ENGINEERING

- exécution

- extensions

- Visage

- RAPIDE

- Figure

- s'adapter

- Flexibilité

- formulaire

- plein

- Général

- l'

- Réservation de groupe

- Croissance

- Croissance

- Matériel

- HTTPS

- idée

- Inc

- industrie

- Infrastructure

- initiative

- Intelligence

- un investissement

- IOT

- IT

- gros

- Nouveautés

- Droit applicable et juridiction compétente

- apprentissage

- Levier

- machine learning

- Manipulation

- Marché

- compte

- ML

- Neon

- réseau et

- Neural

- Réseau neuronal

- offrant

- Offrandes

- ouvert

- Autre

- performant

- Plateformes

- power

- Présentations

- président

- Produit

- Produits

- Exigences

- un article

- Recherche et développement

- Courir

- mise à l'échelle

- Services

- set

- Partager

- So

- Logiciels

- Solutions

- printemps

- Support

- Les soutiens

- Talks

- Les technologies

- Technologie

- tensorflow

- L'initiative

- Formation

- us

- utilisateurs

- semaine

- dans les

- Activités:

- années

- Rendement