L’instrumentation de la validation post-silicium n’est pas une idée nouvelle, mais voici une variante. Utilisation de l'émulation (pré-silicium) pour choisir les structures d'observation de débogage à instrumenter dans le silicium. Paul Cunningham (DG, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, ancien CTO de Synopsys) et moi continuons notre série sur les idées de recherche. Comme toujours, les commentaires sont les bienvenus.

![]()

L'innovation

Le choix de ce mois-ci est Infrastructure d'émulation pour l'évaluation des assertions matérielles pour la validation post-silicium. Le document a été présenté lors des transactions IEEE 2017 sur VLSI. Les auteurs viennent de l'Université McMaster, Hamilton, ON, Canada

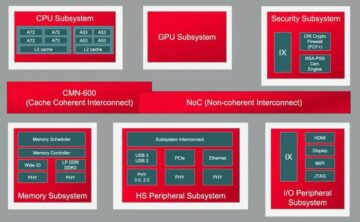

Les auteurs font la distinction entre les erreurs logiques et électriques post-silicium et consacrent leur attention dans cet article aux erreurs électriques, détectables par des retournements de bits dans des flops. Leur approche consiste à déterminer un ensemble optimal d'assertions dans l'analyse pré-silicium. Ils les implémentent ensuite dans le silicium pour prendre en charge le débogage post-silicium. L'analyse pré-silicium est similaire aux erreurs dans les analyses de sécurité, injectant des fautes sur des flops correspondant à des erreurs électriques, comme cela est suggéré dans l'article. Ils génèrent une liste candidate d'assertions à l'aide de la synthèse d'assertions ; le cœur de leur innovation est de fournir une méthode pour évaluer ces assertions en fonction de leur efficacité à détecter plusieurs défauts.

La génération d'entrées est aléatoire, analysant les défauts injectés (traités comme transitoires) en séquence. Ils autorisent un nombre de cycles spécifié par l'utilisateur pour la détection par défaut. Dans une phase ultérieure, ils mesurent l’efficacité à l’aide de deux techniques de couverture différentes. Pour la couverture flip-flop, ils comptent une assertion si elle détecte une erreur injectée sur n'importe quel flop. Dans la couverture bit-flip, ils notent le nombre d'erreurs détectées sur des flops séparés. Ces mesures, ainsi que les estimations de superficie, sont utilisées (en alternance) pour sélectionner les assertions préférées.

le point de vue de Paul

Ce document se marie bien avec notre Blog d'août 2020 sur la détection rapide des erreurs (CQED). QED accélère la détection des bogues fonctionnels post-silicium, ce blog se concentrant sur la détection des bogues électriques post-silicium. L'article est facile à lire, même s'il est utile de lire d'abord la référence [23].

Les bugs électriques sont difficiles à détecter, et même dans ce cas, il est difficile de les reproduire et de trouver la cause physique sous-jacente. Les auteurs proposent une méthode, grâce à une logique intégrée, pour détecter quand de tels bugs provoquent un retournement d’un flop vers une valeur incorrecte (ils ne creusent pas plus loin que la recherche de ces retournements).

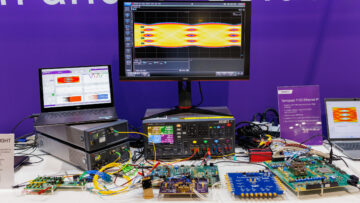

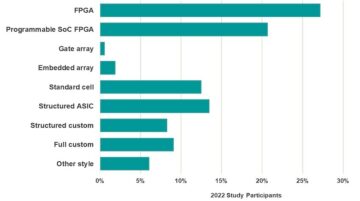

Le cœur de l'article et de sa référence complémentaire [23] est une méthode en plusieurs étapes pour créer et synthétiser cette logique de détection. Cela commence par les propriétés minières de la conception sous forme d'assertions temporelles utilisant le Outil GoldMine. Ils classent les assertions en fonction d'une estimation de leur capacité à détecter les retournements de bits et d'une estimation de la surface/du coût de câblage à mettre en œuvre dans le silicium. Le classement repose sur l'exécution de nombreuses simulations pré-silicium avec des assertions candidates, l'injection d'erreurs de retournement de bits et le comptage des retournements détectés par assertions. Dans l'article original, ils utilisaient la simulation logique. Ici, ils accélèrent ces simulations en mappant la conception sur une carte FPGA Altera.

J'aime la façon dont ils rassemblent plusieurs innovations dans une méthode cohérente pour la détection des retournements de bits post-silicium : l'exploration d'assertions, la synthèse d'assertions et une fonction de classement élégante pour la sélection d'assertions. Cependant, la section des résultats de l'article indique que la détection de retournements de bits dans n % des bascules nécessite une augmentation d'environ n % de la zone de conception. Cela semble difficile pour une application commerciale, d’autant plus que cela permet uniquement de détecter les bugs électriques. On pourrait potentiellement obtenir un résultat similaire en clonant le cône logique pilotant une bascule, puis en comparant le résultat de cette logique clonée à la logique d'origine. Cela semblerait générer une surcharge de zone similaire à celle de leur méthode, dans la limite du clonage de la conception entière (c'est-à-dire une surcharge de zone de 100 %) pour détecter les retournements dans 100 % des échecs de la conception.

Le point de vue de Raul

Le document est autonome et contient pas mal de détails. Les auteurs ont mené des expériences sur 3 circuits séquentiels ISCAS (environ 12 2000 portes, 256 45 FF). Les expériences de préparation injectent 45 erreurs par bascule et en utilisant toutes les assertions générées par GoldMine. En raison de la capacité limitée du FPGA, les auteurs ont divisé les exécutions en 20 « sessions » pour un circuit. Les résultats montrent, même avec 500 sessions, une accélération de l'analyse par rapport à la simulation de 8 à 105 fois (seulement jusqu'à 55 injections d'erreurs car la simulation devient trop lente, 89h). La couverture Flip-Flop maximale réalisable est de 99 %, 3 % et XNUMX % pour les XNUMX circuits. Le nombre d’assertions extraites contrôle la couverture.

L'exécution avec des assertions sélectionnées (correspondant à une surcharge de zone de 5 à 50 %) et 1 à 256 injections entraîne une couverture de bits de 2.2 à 34 %. La plupart du temps, le mineur d’assertion a fonctionné pendant 228 heures. Une chose qui m'a dérouté, ce sont leurs données sur les temps d'exécution par rapport aux erreurs injectées. L'augmentation semble raisonnable (linéaire) en simulation. Mais en émulation ça saute massivement, de 0.045h à 5.4h pour une augmentation de 2 à 8 injections d'erreurs. J'aimerais plus d'explications sur ce point.

Il s’agit d’un document méthodologique. J'aime le fait que presque chaque étape puisse être remplacée par un outil commercial. En plus de l'utilisation d'une grande carte FPGA (comme émulateur), la méthodologie évolue. Les méthodologies sont bien sûr très difficiles à commercialiser, mais c’est une belle application pour la technologie existante !

Mon avis

La méthode d’exploration d’une technique d’analyse de sécurité pour le débogage post-silicium est intrigante. Une idée nouvelle, même si elle conduit à un résultat peu pratique pour une application commerciale.

Partagez cet article via: Source : https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Tous

- selon une analyse de l’Université de Princeton

- Candidature

- Réservé

- auteurs

- Bit

- Blog

- planche

- Punaise

- bogues

- Cadence

- Compétences

- Attraper

- Causes

- commercial

- continuer

- CTO

- données

- Conception

- détail

- Détection

- conduite

- Efficace

- Entrepreneur

- estimations

- juste

- Prénom

- fpga

- fonction

- Portes

- GM

- Matériel

- ici

- Comment

- HTTPS

- idée

- IEEE

- Améliore

- Infrastructure

- Innovation

- IT

- gros

- conduisant

- limité

- Liste

- mesurer

- Métrique

- Mines

- Papier

- proposer

- un article

- Résultats

- pour le running

- Sécurité

- choisi

- Série

- set

- simulation

- scission

- Support

- fiable

- Transactions

- torsion

- université

- Plus-value

- Vérification

- Versus