Dans chaque puce, la puissance est un problème progressif à résoudre. Les concepteurs ont longtemps dû s'appuyer sur une combinaison d'expérience et de connaissances pour résoudre ce dilemme, en attendant généralement la disponibilité du silicium pour effectuer une analyse de puissance avec des charges de travail logicielles réalistes. Cependant, c'est trop tard dans le jeu, car cela devient une proposition coûteuse et chronophage pour résoudre les problèmes d'alimentation post-silicium. Dans cet article de blog, j'expliquerai comment vous pouvez obtenir des résultats de vérification de puissance exploitables en quelques heures sur des conceptions à un milliard de portes dès le début. Avec cette capacité, vous pouvez trouver les régions critiques et les fenêtres temporelles pour la puissance de pointe et, ainsi, optimiser votre RTL et votre logiciel.

L'exécution d'une analyse de puissance post-silicium présente le risque de manquer des situations critiques de haute puissance, ce qui peut créer des problèmes importants de coûts et d'adoption de produits. Les inconvénients de se tromper sur le pouvoir? Un client peut opter pour un autre fournisseur de puces si une conception manque la cible de puissance promise. Ou, un concepteur de système peut être obligé de réduire les performances de la puce pour maintenir l'enveloppe de puissance ciblée, un compromis défavorable dans les applications qui reposent sur des performances de calcul rapides. Dans cet article, initialement publié sur le Blog « Du silicium au logiciel », nous examinerons de plus près certains domaines d'application du SoC où une analyse précise de la puissance est essentielle.

GPU

Les applications GPU traditionnelles sont des entités connues par comparaison, mais cela ne facilite pas la tâche d'analyse de puissance. Considérez un GPU conçu pour un ordinateur portable. Vous pouvez exécuter une analyse de puissance à certains points de mesure sur une période de temps. Cependant, avec potentiellement jusqu'à 10 millions de cycles d'horloge, cette approche n'est clairement pas exhaustive, c'est pourquoi les concepteurs ont traditionnellement dû se fier à leurs meilleures estimations de puissance.

Intelligence artificielle

Dans les puces d'intelligence artificielle (IA), les applications ainsi que la pile logicielle pour les applications et les architectures d'IA sont tous un nouveau territoire, ce qui pose plus de défis du point de vue du profilage de puissance. Pourtant, les récompenses potentielles de l'optimisation des applications d'IA pour la puissance sont grandes. L'efficacité énergétique, après tout, est un avantage que les concepteurs de puces AI aimeraient pouvoir vanter, ainsi que des performances de calcul rapides.

5G

Une autre application critique en termes d'alimentation est la 5G, qui repose sur des performances élevées et une faible latence. Les applications 5G impliquent beaucoup de traitement parallèle et de hautes fréquences, mais, avec une quantité limitée de puissance disponible, elles doivent être optimisées pour fonctionner efficacement. Cela est particulièrement vrai pour les puces de tête radio.

Centres de données

Les centres de données, en particulier les centres de données à grande échelle, sont construits sur des puces ultra-rapides et écoénergétiques qui peuvent aider à maximiser le débit total du système. Avec des milliards de portes et des charges de travail logicielles complexes, les SoC des centres de données sont livrés avec des exigences de vérification et de mise en place de logiciels particulièrement exigeantes.

Breeze Mobile

Compte tenu de leur format compact et de la longue durée de vie souhaitée de la batterie, les appareils mobiles tels que les smartphones ne peuvent pas se permettre d'utiliser des puces qui consomment trop d'énergie. Alors que leurs charges de travail sont devenues de plus en plus complexes, ces appareils, même les GPU énergivores, doivent toujours être en mesure de gérer efficacement ces charges de travail.

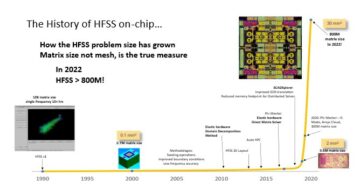

Comment un émulateur de puissance rapide résout le défi du profilage de puissance

Alors que répondre aux exigences d'alimentation dynamique devient de plus en plus difficile, les concepteurs de puces considèrent souvent l'alimentation comme leur principal défi de vérification. La vérification dynamique de la puissance nécessite de trouver la puissance de crête. Pourtant, les événements critiques de puissance de pointe sont entraînés par les charges de travail logicielles réelles. La simulation peut identifier la puissance de crête qui tombe au-dessus ou en dessous du budget de puissance, mais dans les conceptions à milliards de portes, elle ne pourra détecter les événements critiques réels que par pure chance, car les fenêtres qu'une approche basée sur la simulation peut prendre en compte sont beaucoup trop petit. Un outil d'approbation fournirait des mesures de puissance précises, mais s'il est utilisé sur la mauvaise fenêtre temporelle, le concepteur ne serait pas en mesure de déterminer quelle fenêtre a la puissance la plus élevée.

L'identification des bogues à faible consommation nécessite l'exécution de charges de travail logicielles. Les petits tests n'exposeront pas de bogues d'alimentation réalistes liés à la charge de travail. Ce qu'il faut c'est :

- Micrologiciel et système d'exploitation réels lors des tests pré-silicium

- Émulation pour vérifier la puissance sur des millions ou des milliards de cycles

- Vérification de l'alimentation pré-silicium pour le débogage, ce qui n'est pas possible avec le silicium réel

L'émulation à grande vitesse permet aux équipes de conception d'effectuer une vérification de l'alimentation plus tôt dans le cycle de conception, afin de minimiser les risques de bogues d'alimentation et les objectifs d'alimentation SoC manqués. En effet, un émulateur d'alimentation rapide peut être la réponse au dilemme de vérification de l'alimentation matérielle/logicielle, offrant une meilleure précision sur une fenêtre plus large. L'émulateur idéal serait capable d'exécuter plusieurs itérations par jour sur de grandes conceptions avec des charges de travail réalistes. Ce faisant, les concepteurs de puces peuvent obtenir des informations exploitables sur le profil de puissance de leurs conceptions.

Informations exploitables en quelques heures

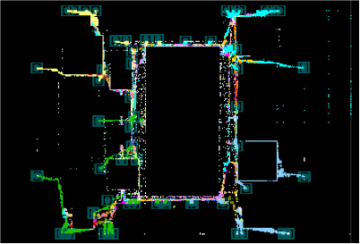

Avec des charges de travail SoC de plusieurs milliards de portes à l'esprit, Synopsys a dévoilé son nouveau système d'émulation Synopsys ZeBu® Empower pour la vérification de l'alimentation matérielle/logicielle. Offrant des performances de calcul maximales, Zébu Empower peut effectuer plusieurs itérations par jour, fournissant des résultats exploitables en quelques heures. Sur la base des profils de puissance résultants, les concepteurs de matériel et de logiciels peuvent, dès le début, identifier les domaines dans lesquels ils peuvent améliorer la puissance dynamique et de fuite. ZeBu Empower utilise Serveur ZeBu technologie matérielle d'émulation rapide pour fournir des délais d'exécution courts.

ZeBu Empower alimente également les blocs critiques en matière d'alimentation et les fenêtres temporelles dans le Moteur Synopsys PrimePower pour accélérer l'analyse de la puissance RTL et l'approbation de la puissance au niveau de la porte. ZeBu Empower et PrimePower font partie du Solution basse consommation basée sur le logiciel Synopsys. Représentée dans le schéma ci-dessous, la solution à faible consommation fournit un flux et une méthodologie de bout en bout allant de l'analyse de l'architecture à l'analyse de la puissance RTL par blocs, en passant par l'analyse et l'optimisation de la puissance SoC.

La solution basse consommation basée sur le logiciel Synopsys est conçue pour aider à réduire la consommation d'énergie dynamique et statique globale des circuits intégrés.

Résumé

La puissance pourrait bien être la partie la plus difficile de l'équation de la puissance, des performances et de la surface (PPA). Et lorsqu'il s'agit de conceptions de plusieurs milliards de portes, la complexité pour obtenir des profils de puissance précis ne fait qu'augmenter. Cependant, avec la solution d'émulation de puissance rapide de Synopsys, les équipes de conception peuvent désormais trouver les régions critiques et les fenêtres temporelles pour la puissance de pointe, afin d'optimiser leur RTL et leur logiciel. En tirant parti du flux de faible puissance complet de Synopsys, les concepteurs disposent d'outils qui peuvent les aider à atteindre leurs objectifs PPA. Compte tenu des charges de travail lourdes et des exigences de performances des applications telles que les GPU, l'IA, la 5G, les centres de données et les mobiles, toute solution pouvant fournir une image de puissance plus précise devrait être un ajout bienvenu à la boîte à outils PPA de tout concepteur.

Partagez cet article via: Source : https://semiwiki.com/eda/synopsys/301320-optimize-rtl-and-software-with-fast-power-verification-results-for-billion-gate-designs/

- 5G

- Adoption

- Avantage

- AI

- Tous

- selon une analyse de l’Université de Princeton

- Application

- applications

- architecture

- Réservé

- intelligence artificielle

- Intelligence artificielle (AI)

- disponibilité

- batterie

- LES MEILLEURS

- Blog

- bogues

- Attraper

- challenge

- puce

- chips

- plus

- calcul

- consommer

- consommation

- données

- Centre de données

- les centres de données

- journée

- livrer

- Conception

- Création de Design

- Compatibles

- entraîné

- "Early Bird"

- efficace

- vous accompagner

- estimations

- événements

- RAPIDE

- flux

- formulaire

- Avant

- jeu

- Portes

- GPU

- GPU

- l'

- Matériel

- front

- Haute

- Comment

- HTTPS

- ICS

- identifier

- idées.

- Intelligence

- vous aider à faire face aux problèmes qui vous perturbent

- IT

- spécialisées

- portatif

- gros

- Location

- love

- million

- Breeze Mobile

- appareils mobiles

- d'exploitation

- le système d'exploitation

- performant

- objectifs

- image

- power

- Produit

- Profil

- Profils

- Radio

- réduire

- Exigences

- Résultats

- Programme de fidélité

- Analyse

- Courir

- pour le running

- Shorts

- simulation

- petit

- smartphones

- So

- Logiciels

- combustion propre

- Target

- Technologie

- tests

- fiable

- top

- Vérification

- attendez

- fenêtres