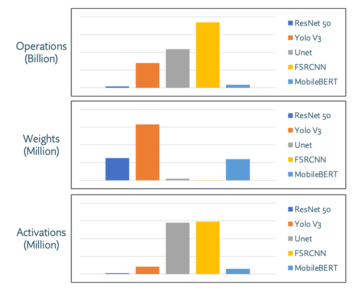

Lorsque nous pensons aux SoC de calcul et d'IA, nous nous concentrons souvent sur le grand nombre de calculs effectués chaque seconde et sur les adresses IP ingénieuses capables d'atteindre des niveaux de performances aussi élevés. Cependant, il existe également un défi important pour maintenir les grandes quantités de données circulant autour de la puce, ce qui est résolu en utilisant un réseau sur puce (NoC). Dans ce webinaire, nous discuterons de certains des défis liés au développement de tels NoC et de ce que nous pouvons faire pour les surmonter.

Lorsque nous pensons aux SoC de calcul et d'IA, nous nous concentrons souvent sur le grand nombre de calculs effectués chaque seconde et sur les adresses IP ingénieuses capables d'atteindre des niveaux de performances aussi élevés. Cependant, il existe également un défi important pour maintenir les grandes quantités de données circulant autour de la puce, ce qui est résolu en utilisant un réseau sur puce (NoC). Dans ce webinaire, nous discuterons de certains des défis liés au développement de tels NoC et de ce que nous pouvons faire pour les surmonter.

Les NoC sont des adresses IP très complexes qui touchent presque toutes les parties d'un SoC. Ils sont intrinsèquement liés au plan d'étage, à l'architecture, aux exigences fonctionnelles, au démarrage, à la sécurité, à la sûreté et à de nombreux autres aspects de la puce. L'exactitude fonctionnelle et les capacités de performance d'un NoC peuvent également prendre du temps et être difficiles à vérifier. Les NoC hautes performances peuvent également occuper une surface importante sur une puce.

Tout cela signifie qu'il peut y avoir une forte probabilité que le NoC subisse des changements tout au long de la vie du projet, et ce changement peut finalement perturber le plan d'étage, et donc avoir un impact significatif sur l'ensemble de la puce.

Pour essayer de réduire la probabilité que cette perturbation se produise, nous utilisons divers outils pour nous permettre d'effectuer une exploration et une vérification des performances au début du processus. En sécurisant les exigences dès le début et en étant en mesure de vérifier rapidement que les spins NoC répondent à ces exigences, nous pouvons également stabiliser le plan d'étage et réduire le roulement inutile dans la conception.

Résumé du webinaire : Les défis liés à la création de chipsets d'IA et de calcul haute performance ne se limitent pas à ceux liés au développement d'IP capables d'effectuer un grand nombre de calculs par seconde. Pour permettre à ces adresses IP de faire leurs calculs, il faut également que des volumes de données de plus en plus importants soient déplacés à grande vitesse dans le SoC. Sondrel explique comment cela peut être fait avec une solution personnalisée de réseau sur puce (NoC).

Ce que vous allez apprendre: Les défis et les solutions pour développer un réseau sur puce dans le cadre d'un grand SoC complexe. Qui devrait y assister : les personnes travaillant sur ou mettant en service de grands SoC

Présentateur: Ben Fletcher est directeur de l'ingénierie chez Sondrel et est impliqué dans tous les aspects du développement SoC, de l'engagement initial du client à la mise en place et à la validation. Il a plus de 20 ans d'expérience principalement dans le développement d'ASIC et de SoC sur le marché de l'électronique grand public, se spécialisant dans l'architecture des chipsets audio, vidéo et IA.

À propos de Sondrel™

Fondée en 2002, Sondrel est le partenaire de confiance de choix pour gérer chaque étape de la création d'un CI. Sa capacité de conseil primée en matière de définition et de conception d'ASIC est entièrement complétée par ses services clés en main pour transformer les conceptions en puces de silicium testées et conditionnées en volume. Ce point de contact unique pour l'ensemble du processus de la chaîne d'approvisionnement garantit un faible risque et des délais de mise sur le marché plus rapides. Basée au Royaume-Uni, Sondrel assiste ses clients dans le monde entier via ses bureaux en Chine, en Inde, en France, au Maroc et en Amérique du Nord. Pour plus d'informations, visitez www.sondrel.com

Partagez cet article via: Source : https://semiwiki.com/semiconductor-services/sondrel/299068-webinar-challenges-in-creating-large-high-performance-compute-socs-in-advanced-geometries/

- AI

- Tous

- Amérique

- architecture

- Réservé

- autour

- ase

- acoustique

- challenge

- Change

- Chine

- puce

- chips

- calcul

- consulting

- consommateur

- Electronique grand public

- La création

- L'engagement des clients

- Clients

- données

- Conception

- Développement

- Directeur

- Perturber

- Perturbation

- "Early Bird"

- Electronique

- ENGINEERING

- exploration

- Focus

- France

- Maniabilité

- Haute

- Comment

- HTTPS

- majeur

- Impact

- Inde

- d'information

- impliqué

- en gardant

- gros

- APPRENTISSAGE

- limité

- LINK

- Marché

- Maroc

- réseau et

- Nord

- Amérique du Nord

- numéros

- Autre

- les partenaires

- Personnes

- performant

- Projet

- réduire

- Exigences

- Analyse

- Sécurité

- sécurité

- Services

- Solutions

- vitesse

- Étape

- Commencez

- la quantité

- chaîne d'approvisionnement

- Les soutiens

- fiable

- -nous

- Uk

- us

- Vérification

- Vidéo

- en direct

- WHO

- dans les

- world

- années