Menginstrumentasikan validasi pasca-silikon bukanlah ide baru, tetapi ada sebuah terobosan. Menggunakan emulasi (pra-silikon) untuk memilih struktur observasi debug untuk instrumen dalam silikon. Paul Cunningham (GM, Verifikasi di Cadence), Raúl Camposano (Silicon Catalyst, pengusaha, mantan CTO Synopsys) dan saya melanjutkan seri ide penelitian kami. Seperti biasa, masukan diterima.

![]()

Inovasi

Pilihan bulan ini adalah Infrastruktur Emulasi untuk Evaluasi Pernyataan Perangkat Keras untuk Validasi Pasca-Silikon. Makalah tersebut dipresentasikan pada IEEE Transactions on VLSI 2017. Penulisnya berasal dari McMaster University, Hamilton, ON, Kanada

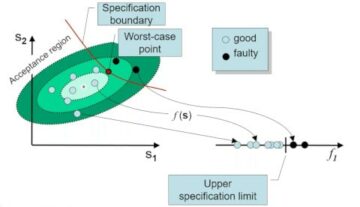

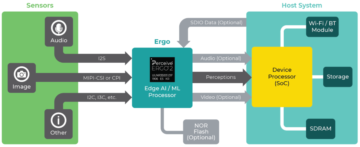

Penulis membedakan antara kesalahan logis dan kesalahan listrik pasca-silikon dan mencurahkan perhatian mereka dalam makalah ini pada kesalahan listrik, yang dapat dideteksi melalui bit-flip pada kegagalan. Pendekatan mereka adalah menentukan serangkaian pernyataan optimal dalam analisis pra-silikon. Ini kemudian mereka terapkan dalam silikon untuk mendukung debug pasca-silikon. Analisis pra-silikon mirip dengan kesalahan dalam analisis keselamatan, memasukkan kesalahan pada jepit yang berhubungan dengan kesalahan listrik, seperti yang diisyaratkan di makalah. Mereka menghasilkan daftar kandidat pernyataan menggunakan sintesis pernyataan; inti dari inovasi mereka adalah menyediakan metode untuk menilai pernyataan-pernyataan ini berdasarkan seberapa efektif pernyataan-pernyataan tersebut dalam mendeteksi banyak kesalahan.

Pembuatan input dilakukan secara acak, menganalisis kesalahan yang dimasukkan (dianggap sementara) secara berurutan. Mereka mengizinkan sejumlah siklus yang ditentukan pengguna untuk deteksi per kesalahan. Pada fase selanjutnya, mereka mengukur efektivitas menggunakan dua teknik cakupan yang berbeda. Untuk cakupan flip-flop, mereka menghitung pernyataan jika ia menangkap kesalahan yang disuntikkan pada kegagalan mana pun. Dalam cakupan bit-flip, mereka mencetak pernyataan jumlah kesalahan yang terdeteksi pada kegagalan terpisah. Metrik ini, bersama dengan perkiraan luas, digunakan (secara bergantian) untuk memilih pernyataan yang diinginkan.

pandangan Paulus

Makalah ini cocok sekali dengan makalah kami Blog Agustus 2020 tentang deteksi kesalahan cepat (QED). QED mempercepat deteksi bug fungsional pasca-silikon, dimana blog ini berfokus pada deteksi bug listrik pasca-silikon. Makalah ini mudah dibaca, meskipun membantu untuk membaca referensi terlebih dahulu [23].

Kutu listrik sulit untuk ditangkap, dan meskipun demikian, sulit untuk ditiru dan menemukan penyebab fisik yang mendasarinya. Penulis mengusulkan sebuah metode, melalui logika tertanam, untuk mendeteksi kapan bug tersebut menyebabkan kegagalan membalik ke nilai yang salah (mereka tidak menggali lebih dalam daripada menemukan pembalikan ini).

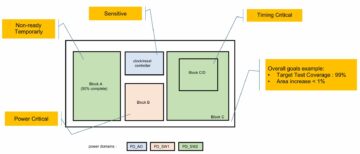

Inti dari makalah ini dan referensi pendampingnya [23] adalah metode multi-langkah untuk membuat dan mensintesis logika deteksi ini. Ini dimulai dengan menambang properti desain sebagai pernyataan temporal menggunakan Alat Tambang Emas. Mereka memberi peringkat pada pernyataan berdasarkan perkiraan kemampuan mereka untuk mendeteksi pembalikan bit, dan perkiraan biaya area/pengkabelan untuk diterapkan dalam silikon. Pemeringkatan bergantung pada menjalankan banyak simulasi pra-silikon dengan pernyataan kandidat, memasukkan kesalahan bit flip, dan menghitung pembalikan yang terdeteksi berdasarkan pernyataan. Dalam makalah aslinya mereka menggunakan simulasi logika, di sini mereka mempercepat simulasi ini dengan memetakan desain ke papan Altera FPGA.

Saya suka bagaimana mereka menyatukan beberapa inovasi menjadi metode yang koheren untuk deteksi bit flip pasca-silikon: penambangan pernyataan, sintesis pernyataan, dan fungsi peringkat yang elegan untuk pemilihan pernyataan. Namun, bagian hasil makalah ini menunjukkan bahwa mendeteksi pembalikan bit pada n% flip-flop memerlukan peningkatan sekitar n% pada area desain. Hal ini tampaknya menantang untuk aplikasi komersial, terutama karena ini hanya membantu menemukan bug listrik. Seseorang berpotensi mencapai hasil serupa dengan mengkloning kerucut logika yang menggerakkan flip-flop, lalu membandingkan keluaran logika yang dikloning ini dengan logika aslinya. Tampaknya hal ini menghasilkan overhead area yang serupa dengan metode mereka, dalam batas mengkloning seluruh desain (yaitu 100% overhead area) untuk mendeteksi flips pada 100% kegagalan dalam desain.

Pandangan Raul

Makalah ini mandiri dengan cukup banyak detail. Penulis menjalankan eksperimen untuk 3 rangkaian sekuensial ISCAS (kira-kira gerbang 12K, 2000 FF). Eksperimen persiapan memasukkan 256 kesalahan per flip flop dan menggunakan semua pernyataan yang dihasilkan oleh GoldMine. Karena terbatasnya kapasitas FPGA, penulis membagi proses menjadi 45 “sesi” untuk satu sirkuit. Hasilnya menunjukkan, bahkan dengan 45 sesi, percepatan analisis terhadap simulasi sebesar 20-500 kali (hanya hingga 8 injeksi kesalahan karena simulasi menjadi terlalu lambat, 105 jam). Cakupan Flip-Flop maksimum yang dapat dicapai adalah 55%, 89% dan 99% untuk 3 sirkuit. Jumlah pernyataan yang ditambang mengontrol cakupan.

Menjalankan dengan pernyataan yang dipilih (sesuai dengan overhead area 5-50%) dan injeksi 1-256 menghasilkan cakupan bit 2.2%-34%. Seringkali, penambang pernyataan berlari selama 228 jam. Satu hal yang membingungkan saya adalah data run-time versus error yang dimasukkan. Peningkatan tersebut terlihat wajar (linier) dalam simulasi. Namun dalam emulasinya melonjak secara besar-besaran, dari 0.045 jam menjadi 5.4 jam dengan peningkatan 2 hingga 8 suntikan kesalahan. Saya ingin penjelasan lebih lanjut tentang hal ini.

Ini adalah makalah metodologi. Saya suka bahwa hampir setiap langkah dapat digantikan oleh alat komersial. Bersamaan dengan penggunaan papan FPGA besar (sebagai emulator), metodologi ini dapat diperluas. Metodologi tentu saja sangat sulit untuk dikomersialkan, namun ini merupakan penerapan yang bagus untuk teknologi yang ada!

Pandangan saya

Metode eksplorasi teknik analisis keamanan untuk debug pasca-silikon sangat menarik. Sebuah ide baru, meskipun memberikan hasil yang agak tidak praktis untuk penerapan komersial.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Semua

- analisis

- Aplikasi

- DAERAH

- penulis

- Bit

- Blog

- papan

- Bug

- bug

- Irama

- Kapasitas

- gulat

- Menyebabkan

- komersial

- terus

- CTO

- data

- Mendesain

- rinci

- Deteksi

- penggerak

- Efektif

- Pengusaha

- perkiraan

- adil

- Pertama

- FPGA

- fungsi

- Gates

- GM

- Perangkat keras

- di sini

- Seterpercayaapakah Olymp Trade? Kesimpulan

- HTTPS

- ide

- IEEE

- Meningkatkan

- Infrastruktur

- Innovation

- IT

- besar

- terkemuka

- Terbatas

- Daftar

- mengukur

- Metrik

- Pertambangan

- kertas

- mengusulkan

- penelitian

- Hasil

- berjalan

- Safety/keselamatan

- terpilih

- Seri

- set

- simulasi

- membagi

- mendukung

- waktu

- Transaksi

- twist

- universitas

- nilai

- Verifikasi

- Lawan