Di setiap chip, daya adalah masalah progresif yang harus dipecahkan. Desainer telah lama bergantung pada kombinasi pengalaman dan pengetahuan untuk mengatasi dilema ini, biasanya harus menunggu hingga ketersediaan silikon untuk melakukan analisis daya dengan beban kerja perangkat lunak yang realistis. Namun, ini sudah terlambat dalam permainan, karena menjadi proposisi yang mahal dan memakan waktu untuk menyelesaikan masalah daya pasca-silikon. Dalam posting blog ini, saya akan menjelaskan bagaimana Anda dapat mencapai hasil verifikasi daya yang dapat ditindaklanjuti dalam hitungan jam pada desain miliaran gerbang sejak dini. Dengan kemampuan ini, Anda dapat menemukan wilayah kritis dan jendela waktu untuk daya puncak dan, dengan demikian, mengoptimalkan RTL dan perangkat lunak Anda.

Melakukan analisis daya pasca-silikon menimbulkan risiko hilangnya situasi daya tinggi yang kritis, yang dapat menimbulkan masalah biaya dan adopsi produk yang signifikan. Kerugian dari kesalahan tentang kekuasaan? Seorang pelanggan dapat memilih untuk pergi dengan vendor chip lain jika sebuah desain meleset dari target daya yang dijanjikan. Atau, perancang sistem mungkin terpaksa memutar balik kinerja chip untuk mempertahankan amplop daya yang ditargetkan—pertukaran yang tidak menguntungkan dalam aplikasi yang mengandalkan kinerja komputasi cepat. Dalam posting ini, yang awalnya diterbitkan di Blog “Dari Silikon ke Perangkat Lunak”, kita akan melihat lebih dekat beberapa area aplikasi SoC di mana analisis daya yang akurat sangat penting.

GPU

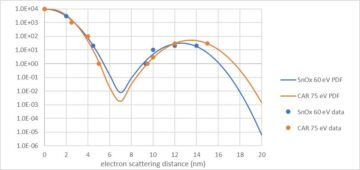

Aplikasi GPU tradisional adalah entitas yang dikenal sebagai perbandingan, tetapi ini tidak membuat tugas analisis daya menjadi lebih mudah. Pertimbangkan GPU yang dirancang untuk komputer laptop. Anda dapat menjalankan analisis daya pada titik pengukuran tertentu selama periode waktu tertentu. Namun, dengan potensi hingga 10 juta siklus clock, pendekatan ini jelas tidak lengkap—itulah sebabnya desainer secara tradisional harus mengandalkan perkiraan terbaik mereka untuk daya.

Kecerdasan Buatan

Dalam chip kecerdasan buatan (AI), aplikasi serta tumpukan perangkat lunak untuk aplikasi dan arsitektur AI semuanya merupakan wilayah baru, yang menghadirkan lebih banyak tantangan dari perspektif profil daya. Namun, manfaat potensial dari pengoptimalan aplikasi AI untuk daya sangat besar. Efisiensi daya, bagaimanapun, adalah keuntungan yang ingin dibanggakan oleh perancang chip AI, bersama dengan kinerja komputasi yang cepat.

5G

Aplikasi penting daya lainnya adalah 5G, yang semuanya tentang kinerja tinggi dan latensi rendah. Aplikasi 5G melibatkan banyak pemrosesan paralel dan frekuensi tinggi, tetapi, dengan hanya begitu banyak daya yang tersedia, aplikasi tersebut harus dioptimalkan agar berjalan secara efisien. Hal ini terutama berlaku untuk chip kepala radio.

Pusat Data

Pusat data, terutama pusat data skala besar, dibangun di atas chip yang sangat cepat dan hemat energi yang dapat membantu memaksimalkan total keluaran sistem. Dengan miliaran gerbang bersama dengan beban kerja perangkat lunak yang kompleks, SoC pusat data hadir dengan persyaratan verifikasi dan peningkatan perangkat lunak yang sangat menuntut.

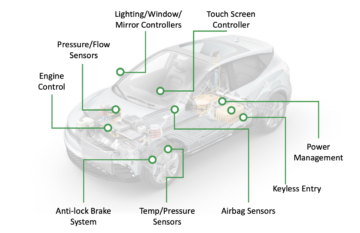

mobil

Mengingat faktor bentuknya yang ringkas dan masa pakai baterai yang lama, perangkat seluler seperti ponsel cerdas tidak dapat menggunakan chip yang menghabiskan terlalu banyak daya. Sementara beban kerja mereka semakin kompleks, perangkat ini—bahkan GPU yang haus daya—masih dapat mengakomodasi beban kerja ini secara efisien.

Bagaimana Fast Power Emulator Memecahkan Tantangan Power Profiling

Karena memenuhi kebutuhan daya dinamis menjadi semakin sulit, perancang chip sering menganggap daya sebagai tantangan verifikasi utama mereka. Verifikasi daya dinamis membutuhkan pencarian daya puncak. Namun, peristiwa daya puncak kritis didorong oleh beban kerja perangkat lunak yang sebenarnya. Simulasi dapat mengidentifikasi daya puncak yang berada di atas dan juga di bawah anggaran daya, tetapi dalam desain gerbang miliaran, itu hanya akan dapat menangkap peristiwa kritis yang sebenarnya dengan keberuntungan murni, karena jendela yang dapat dipertimbangkan oleh pendekatan berbasis simulasi juga sangat banyak. kecil. Alat penanda akan memberikan pengukuran daya yang akurat, tetapi jika digunakan pada jendela waktu yang salah, perancang tidak akan dapat menentukan jendela mana yang memiliki daya tertinggi.

Mengidentifikasi bug berdaya rendah memerlukan beban kerja perangkat lunak yang berjalan. Tes kecil tidak akan mengekspos bug daya yang digerakkan oleh beban kerja yang realistis. Yang dibutuhkan adalah:

- Firmware dan sistem operasi nyata pada pengujian pra-silikon

- Emulasi untuk memverifikasi daya selama jutaan atau miliaran siklus

- Verifikasi daya pra-silikon untuk debug, yang tidak mungkin dilakukan dengan silikon yang sebenarnya

Emulasi berkecepatan tinggi memungkinkan tim desain melakukan verifikasi daya lebih awal dalam siklus desain, sehingga mereka dapat meminimalkan risiko bug daya dan sasaran daya SoC yang terlewatkan. Memang, emulator daya cepat dapat menjadi jawaban untuk dilema verifikasi daya perangkat keras/lunak, memberikan akurasi yang lebih baik di jendela yang lebih luas. Emulator yang ideal akan dapat menjalankan beberapa iterasi sehari pada desain besar dengan beban kerja yang realistis. Dengan demikian, desainer chip dapat memperoleh wawasan yang dapat ditindaklanjuti ke dalam profil kekuatan desain mereka.

Wawasan yang Dapat Ditindaklanjuti dalam hitungan jam

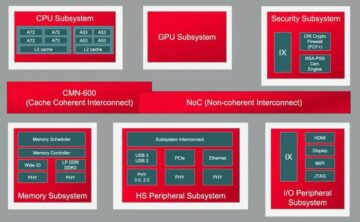

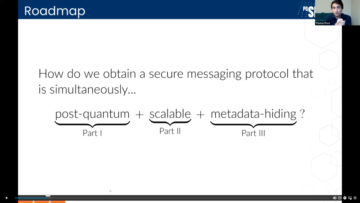

Dengan mempertimbangkan beban kerja SoC multi-miliar gerbang, Synopsys telah meluncurkan sistem emulasi Synopsys ZeBu® Empower baru untuk verifikasi daya perangkat keras/lunak. Memberikan kinerja komputasi maksimum, ZeBu Memberdayakan dapat melakukan beberapa iterasi sehari, memberikan hasil yang dapat ditindaklanjuti dalam hitungan jam. Berdasarkan profil daya yang dihasilkan, perancang perangkat keras dan perangkat lunak dapat, sejak awal, mengidentifikasi area di mana mereka dapat meningkatkan daya dinamis dan kebocoran. ZeBu Memberdayakan menggunakan Server ZeBu teknologi perangkat keras emulasi cepat untuk menyediakan waktu penyelesaian yang singkat.

ZeBu Empower juga memasukkan blok kritis daya dan jendela waktu ke dalam Synopsys mesin PrimePower untuk mempercepat analisis daya RTL dan pemutusan daya tingkat gerbang. Baik ZeBu Empower dan PrimePower adalah bagian dari Solusi daya rendah berbasis perangkat lunak Synopsys. Digambarkan dalam diagram di bawah ini, solusi berdaya rendah menyediakan aliran dan metodologi ujung ke ujung mulai dari analisis arsitektur hingga analisis daya blok RTL hingga analisis dan pengoptimalan daya SoC.

Solusi daya rendah yang digerakkan oleh perangkat lunak Synopsys dirancang untuk membantu mengurangi konsumsi daya IC yang dinamis dan statis secara keseluruhan.

Kesimpulan

Daya mungkin merupakan bagian paling menantang dari persamaan daya, kinerja, dan area (PPA). Dan dalam hal desain multi-miliar gerbang, kompleksitas dalam mencapai profil daya yang akurat semakin bertambah. Namun, dengan solusi emulasi daya cepat dari Synopsys, tim desain kini dapat menemukan wilayah kritis dan jendela waktu untuk daya puncak, sehingga mereka dapat mengoptimalkan RTL dan perangkat lunak mereka. Dengan memanfaatkan aliran daya rendah Synopsys yang komprehensif, desainer mendapatkan alat yang dapat membantu mereka memenuhi target PPA mereka. Mengingat beban kerja yang berat dan tuntutan kinerja aplikasi seperti GPU, AI, 5G, pusat data, dan seluler, solusi apa pun yang dapat memberikan gambaran daya yang lebih akurat harus menjadi tambahan yang disambut baik untuk toolkit PPA desainer mana pun.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/eda/synopsys/301320-optimize-rtl-and-software-with-fast-power-verification-results-for-billion-gate-designs/

- 5G

- Adopsi

- Keuntungan

- AI

- Semua

- analisis

- Aplikasi

- aplikasi

- arsitektur

- DAERAH

- kecerdasan buatan

- Kecerdasan buatan (AI)

- tersedianya

- baterai

- TERBAIK

- Blog

- bug

- gulat

- menantang

- keping

- Keripik

- lebih dekat

- menghitung

- memakan

- konsumsi

- data

- Data Center

- Pusat Data

- hari

- mengantarkan

- Mendesain

- perancang

- Devices

- didorong

- Awal

- efisiensi

- memberdayakan

- perkiraan

- peristiwa

- FAST

- aliran

- bentuk

- Depan

- permainan

- Gates

- GPU

- GPU

- besar

- Perangkat keras

- kepala

- High

- Seterpercayaapakah Olymp Trade? Kesimpulan

- HTTPS

- ICS

- mengenali

- wawasan

- Intelijen

- masalah

- IT

- pengetahuan

- laptop

- besar

- Panjang

- cinta

- juta

- mobil

- telepon genggam

- operasi

- sistem operasi

- prestasi

- perspektif

- gambar

- kekuasaan

- Produk

- Profil

- profil

- radio

- menurunkan

- Persyaratan

- Hasil

- Hadiah

- Risiko

- Run

- berjalan

- Pendek

- simulasi

- kecil

- smartphone

- So

- Perangkat lunak

- sistem

- target

- Teknologi

- tes

- waktu

- puncak

- Verifikasi

- menunggu

- Windows