Achronix dikenal dengan solusi FPGA berkinerja tinggi. Dalam posting ini, saya akan menjelajahi Speedster7T FPGA. Rangkaian FPGA ini dioptimalkan untuk beban kerja bandwidth tinggi dan menghilangkan hambatan kinerja dengan arsitektur inovatif. Dibangun pada proses FinFET 7nm TSMC, rangkaian ini memberikan kinerja tingkat ASIC sambil mempertahankan kemampuan program penuh FPGA. Ada banyak hal yang perlu dipelajari tentang Speedster7T. Achronix sekarang memiliki video yang akan menjawab banyak pertanyaan tersebut. Ada link ke video tersebut dan masih banyak lagi yang akan datang, tapi pertama-tama mari kita lihat apa yang terjadi saat Anda menggunakan Achronix Speedster7t FPGA untuk test drive di lab.

Achronix dikenal dengan solusi FPGA berkinerja tinggi. Dalam posting ini, saya akan menjelajahi Speedster7T FPGA. Rangkaian FPGA ini dioptimalkan untuk beban kerja bandwidth tinggi dan menghilangkan hambatan kinerja dengan arsitektur inovatif. Dibangun pada proses FinFET 7nm TSMC, rangkaian ini memberikan kinerja tingkat ASIC sambil mempertahankan kemampuan program penuh FPGA. Ada banyak hal yang perlu dipelajari tentang Speedster7T. Achronix sekarang memiliki video yang akan menjawab banyak pertanyaan tersebut. Ada link ke video tersebut dan masih banyak lagi yang akan datang, tapi pertama-tama mari kita lihat apa yang terjadi saat Anda menggunakan Achronix Speedster7t FPGA untuk test drive di lab.

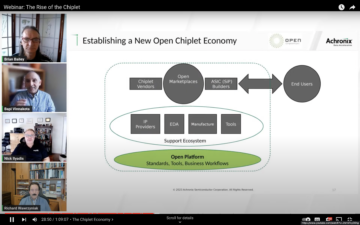

Steve Mensor, VP penjualan dan pemasaran di Achronix memperkenalkan video tersebut. Steve telah bersama Achronix selama hampir sepuluh tahun dan sebelumnya menghabiskan 21 tahun di Altera. Dia tentu tahu banyak tentang FPGA – desain dan aplikasi. Steve memulai dengan menguraikan beberapa elemen arsitektur inovatif yang disebutkan sebelumnya. Ada banyak kemampuan khusus pada Speedster7T. Ini termasuk:

- Layanan 112 Gbps

- 400G Ethernet

- PCIe Gen5

- GDDR6 berjalan pada 4 Tbps

- DDR 4 berjalan pada 3,200 Mbps

- Prosesor pembelajaran mesin berpemilik

- Jaringan 2D pada chip (NoC)

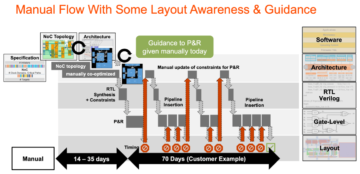

Prosesor pembelajaran mesin berpemilik memberikan banyak fungsi, termasuk operasi floating point, floating point blok, dan integer. NoC 2D adalah kemampuan industri baru untuk FPGA dari Achronix. NoC dapat merutekan data dari antarmuka berkecepatan tinggi mana pun ke inti FPGA fabric pada 2 GHz tanpa menggunakan sumber daya logika FPGA apa pun. Semua teknologi terpasang ini memungkinkan Anda mencapai performa tingkat ASIC dalam FPGA.

Steve kemudian menyerahkan presentasinya kepada Katie Purcell, manajer teknik aplikasi di Achronix. Katie telah bersama Achronix selama empat tahun. Sebelumnya dia adalah seorang desainer ASIC. Dia juga menghabiskan waktu di Xilinx. Katie adalah orang yang menggunakan Speedster7t FPGA untuk test drive di lab, dan dia jelas siap menghadapi tantangan tersebut.

Katie membawa penonton ke lab Achronix tempat dilakukannya penampilan Speedster7T – validasi dan karakterisasi. Demo yang disajikan Katie menunjukkan perangkat yang menjalankan lalu lintas ethernet 400G di Kartu akselerator Achronix VectorPath. Katie memulai dengan merangkum elemen-elemen kunci dari demonstrasi tersebut, yang meliputi:

- Antarmuka eksternal 8X50G

- Antarmuka 400G tunggal dalam subsistem ethernet

- Data dibagi menjadi empat aliran terpisah di NoC 2D

- Setiap aliran diproses secara independen

Katie menghabiskan beberapa waktu di NoC 2D. Dia menunjukkan bahwa kemampuan ini membuat desain lebih sederhana dan lebih mudah untuk menutup waktu. NoC 2D unik ini muncul beberapa kali selama demo. Ada baiknya menggali lebih dalam untuk memahaminya. Achronix sebelumnya mempresentasikan webinar tentang kemampuan unik ini dibahas di SemiWiki bernama 5 Alasan Mengapa SmartNIC Berkinerja Tinggi yang Dapat Dikonfigurasi Ulang Membutuhkan NoC 2D. Kabar baiknya adalah pemutaran ulang webinar yang sangat informatif ini kini telah tersedia. Anda bisa menontonnya di sini.

Katie membawa Anda melihat secara mendetail apa yang terjadi di dalam perangkat Speedster7T saat memproses paket data. Mengetahui detail tersebut membantu memahami kemudahan pengaturan dan akurasi yang ditunjukkan selama demo. Jika menurut Anda perangkat unik seperti ini dapat membantu proyek desain Anda, saya sangat menyarankan Anda menonton demonya. Singkat memang, tapi sangat bermanfaat. Kamu bisa akses video demo di sini.

Sekarang Anda tahu cara menggunakan Achronix Speedster7t FPGA untuk test drive di lab. Anda dapat mengetahui lebih detail mengenai hal ini keluarga FPGA unik di sini.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- akselerator

- Semua

- Aplikasi

- arsitektur

- asic

- Bit

- papan

- menantang

- keping

- kedatangan

- data

- Mendesain

- perancang

- Teknik

- kain

- keluarga

- Pertama

- FPGA

- penuh

- baik

- High

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HTTPS

- Termasuk

- inovatif

- IT

- kunci

- BELAJAR

- pengetahuan

- LINK

- Mesin belajar

- Marketing

- jaringan

- berita

- Operasi

- prestasi

- proyek

- alasan

- Sumber

- Rute

- berjalan

- penjualan

- Pendek

- Solusi

- Teknologi

- uji

- waktu

- lalu lintas

- Video

- Menonton

- webinar

- SIAPA

- bernilai

- X

- tahun