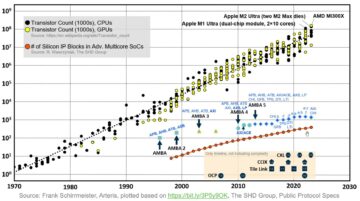

L’industria dei semiconduttori si sta preparando per la migrazione da sistemi proprietari basati su chiplet a un ecosistema di chiplet più aperto, in cui chiplet fabbricati da diverse aziende con varie tecnologie e nodi di dispositivi possano essere integrati in un unico pacchetto con una resa accettabile.

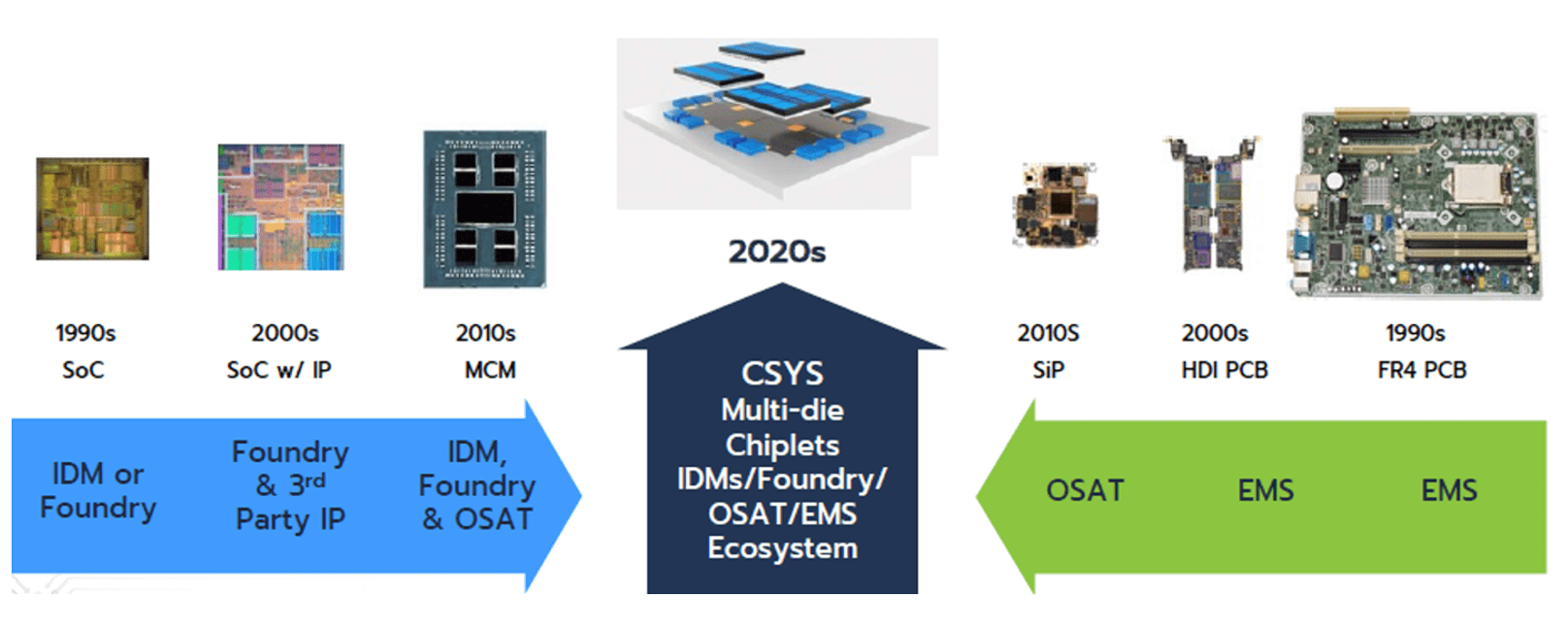

Per far sì che tutto funzioni come previsto, l’industria dei chip dovrà risolvere una serie di problemi tecnici e commerciali ben documentati e dovrà tenere a freno alcune delle visioni più grandiose di ciò che è possibile, almeno inizialmente. La sfida fondamentale è allineare le richieste di prestazioni specifiche del dominio dei sistemi finali, che ne contengono un numero crescente chiplet, con le capacità e le metodologie di assemblaggio e confezionamento di IDM, fonderiee OSAT. Ciò include la creazione di kit di sviluppo dell'assemblaggio (ADK) che sono più o meno l'equivalente dei kit di sviluppo del processo (PDK), che oggi sono codificati con specifiche di produzione.

Un PDK fornisce il livello di dettaglio appropriato necessario per sviluppare chip planari, unendo strumenti di progettazione con processi fab per ottenere un risultato prevedibile. Ma far funzionare tutto questo per un ADK con chiplet eterogenei è molto più complesso. I team di progettazione e assemblaggio devono gestire le co-dipendenze termiche, meccaniche ed elettriche che causano stress elettrici e meccanici, con conseguenti deformazioni, resa ridotta e problemi di affidabilità con carichi di lavoro reali. A ciò si aggiungono le questioni commerciali e legali relative all'imballaggio di diversi dispositivi di diversi produttori.

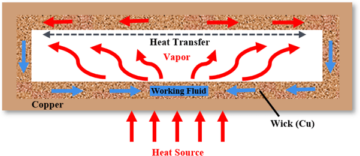

“I chiplet rappresentano una tendenza in crescita, soprattutto nei segmenti HPC e networking, con potenziale di espansione verso altre applicazioni”, ha affermato Gabriela Pereira, analista di tecnologia e mercato per l’imballaggio dei semiconduttori presso Yole Intelligenza. “L'industria ha capito che per collegarli sono necessarie tecnologie di packaging avanzate e di fascia alta, ma la questione è molto più complessa di quanto sembri. La connessione dei chiplet richiede la progettazione di interconnessioni ad alta larghezza di banda a livello di pacchetto, che possono assumere forme diverse – ad esempio 2D, 2.5D o 3D – garantendo al tempo stesso il rispetto dei requisiti termici e di potenza”.

I dispositivi commerciali basati su chiplet generalmente sono specifici del dominio e talvolta sviluppati per un carico di lavoro specifico. Quindi, nonostante la grande spinta del settore per creare un ecosistema mix-and-match simile a LEGO per i chiplet – che oggi include più fornitori IP ed EDA, fonderie, fornitori di memoria, OSAT, fornitori di substrati, ecc. – per far funzionare questo come previsto sarà necessario tempo e una mole enorme di lavoro.

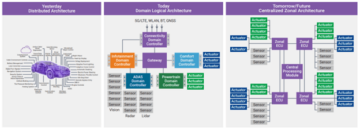

Fig. 1: L'assemblaggio del sistema richiede un accoppiamento più stretto tra produttori di chip e OSAT. Fonte: ASE

Nella creazione integrato eterogeneo progetti, è essenziale avere una collaborazione molto più stretta tra fonderie, IDM, OSAT e produttori di PCB. E poiché ogni sistema basato su chiplet sarà personalizzato, il numero di processi di assemblaggio aumenterà notevolmente. Ad esempio, un OSAT ha notato che tra i suoi circa 5,000 clienti esistono circa 1,000 diversi processi di assemblaggio.

Questa diversità di prodotti e processi rende difficile ottenere risultati prevedibili scegliendo i chiplet da un ampio menu di opzioni.

"Abbiamo già riscontrato numerose limitazioni, tra cui non solo il silicio, ma anche l'integrazione e l'ecosistema", ha affermato Lihong Cao, direttore senior di Gruppo ASE, al forum Road to Chiplets di MEPTEC. Ha sottolineato che i clienti continuano a spingere per un processo di assemblaggio dei chiplet a basso costo, il che sta creando una tensione costruttiva tra lo sviluppo di un processo di assemblaggio sofisticato e le realtà economiche dei diversi settori industriali. I dispositivi informatici per il settore automobilistico, ad esempio, hanno una maggiore sensibilità ai costi rispetto a quelli dei data center, ma i loro chip funzionano in un ambiente più ostile per una durata di vita più lunga.

Ciò che serve è un insieme definito di ricette del processo di assemblaggio – fondamentalmente, un menu di scelte molto limitato – specifiche per l’applicazione finale (HPC, automobilistico, telecomunicazioni RF) al fine di ridurre il costo dei sistemi basati su chiplet. OSAT e fonderie si stanno già muovendo in quella direzione per il calcolo ad alte prestazioni. Ad esempio, in occasione dell’evento Direct Connect del 2024, Intel ha condiviso i suoi sei diversi processi di pacchetto per i chiplet. TSMC e Samsung offrono anche set definiti di processi chiplet. Ma il successo di questi processi di assemblaggio richiede che i team di ingegneri co-ottimizzino flussi, processi e materiali per soddisfare al meglio i requisiti del sistema.

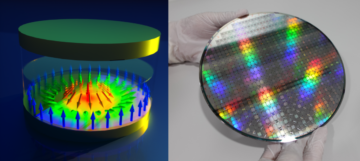

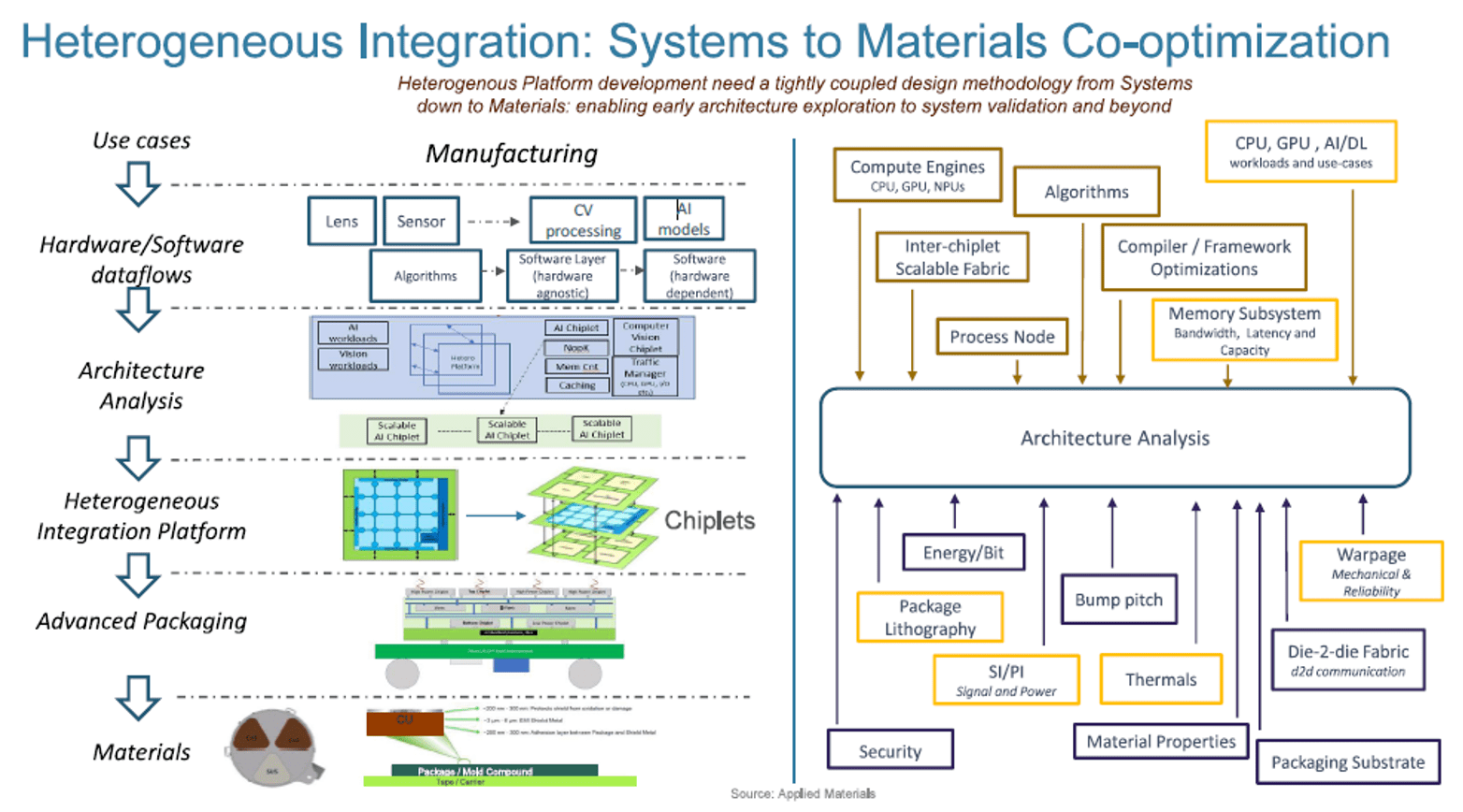

Fig. 2: Lo sviluppo di una piattaforma integrata richiede un'analisi architetturale strettamente accoppiata che coottimizzi la progettazione del sistema con l'architettura, il processo di assemblaggio e la selezione dei materiali di imballaggio. Fonte: materiali applicati

“In precedenza, quando progettavamo un sistema dovevamo preoccuparci solo dei requisiti di sistema. Una volta che iniziamo a separare gli stampi e a rimontarli, dobbiamo iniziare a guardare ad altre cose. Dobbiamo preoccuparci di metterli insieme considerando l’integrità del segnale tra gli stampi, l’affidabilità, le caratteristiche termiche, ecc.”, ha affermato Itai Leshniak, direttore delle soluzioni di sistemi AI presso Applied Materials, al forum MEPTEC. “Se prendiamo il caso della visione artificiale basata sull’intelligenza artificiale, possiamo scomporla strato dopo strato, dal lato hardware, determinando quali processori, sensori e filtri di visione artificiale sono necessari per scomporla nell’architettura a livello. Quindi inizieremo a esaminare come confezionare tutti questi chiplet, quali materiali utilizzare e come trarne vantaggio”.

Materiali e processi di assemblaggio

Concettualmente, gli ingegneri progettisti utilizzeranno i chiplet per progettare un sistema. Tuttavia, la co-progettazione e l’integrazione sono molto più complicate dell’assemblaggio di una serie di blocchi LEGO, perché i chiplet, gli interpositori e i substrati del pacchetto provengono da diverse società di progettazione e impianti di produzione. Le tecnologie di packaging avanzate utilizzate per connettere i chiplet variano con un insieme di nomi alfabetici: FOWLP, FOPLP, CoWoS, ecc., ognuno dei quali pone ulteriori scelte di progettazione e materiali insieme a determinate limitazioni di processo.

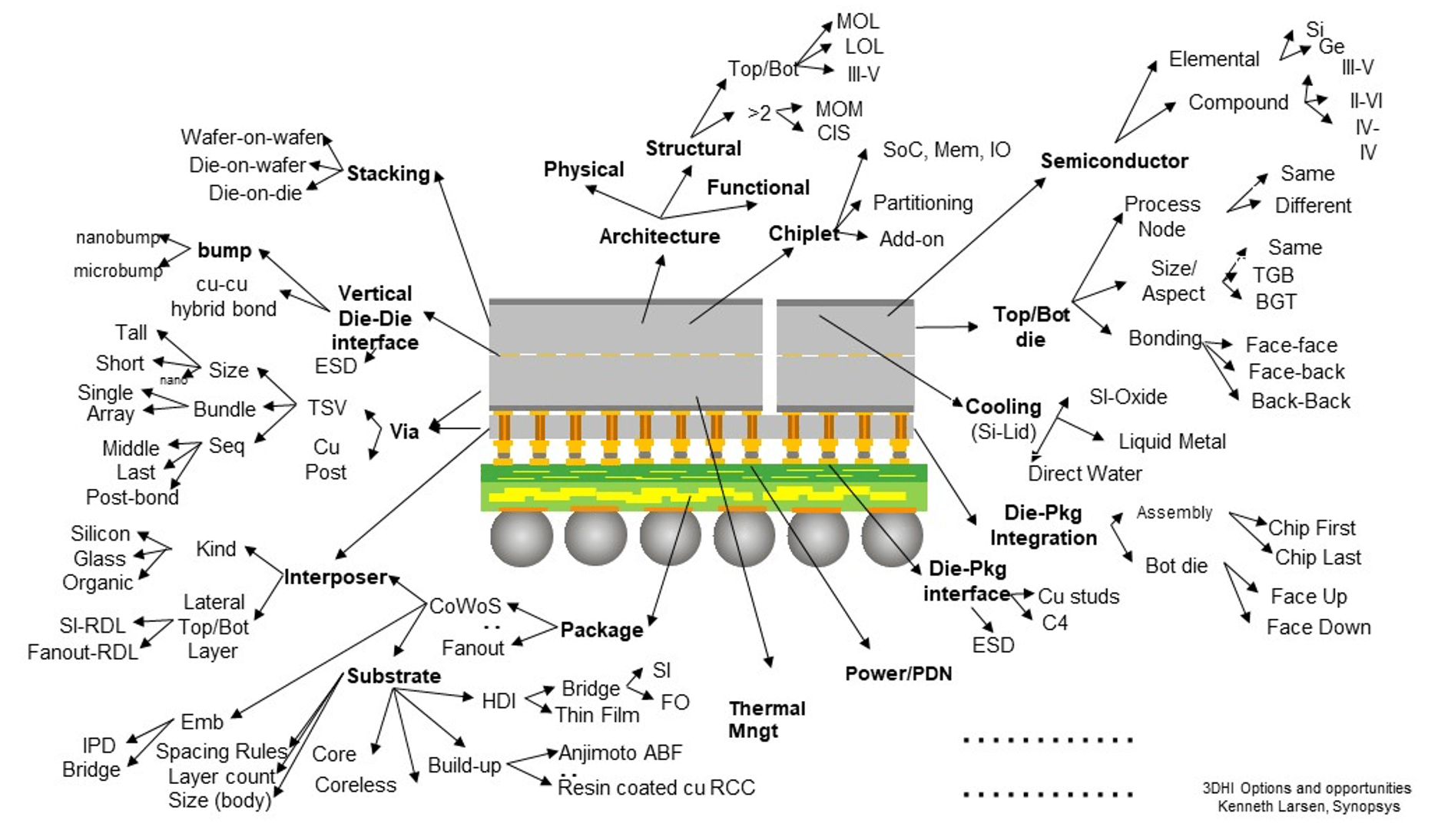

Fig. 3: Esistono numerose scelte nell'imballaggio multi-die, dal layout di alto livello ai substrati, ai materiali, ai metodi di incollaggio e ai materiali di raffreddamento. Fonte: sinossi

Attualmente i team di ingegneri determinano i compromessi tra le diverse opzioni di imballaggio per selezionare i materiali, ricavare una ricetta di processo e determinare le regole di progettazione.

I materiali sono un buon punto di partenza. "I materiali sono molto importanti perché consentono nuovi prodotti e tecnologie di imballaggio", Tanja Braun, vicedirettore del gruppo presso l'Istituto Fraunhofer per l'affidabilità e la microintegrazione IZM. “Man mano che si passa a packaging più avanzati, il processo diventa molto più complesso perché si mettono insieme più cose. Alla fine, si tratta di una combinazione di attrezzature, materiali e sviluppo dei processi."

Ci sono tre parametri termici critici nei processi di assemblaggio dei package: coefficienti di dilatazione termica (CTE), temperatura di transizione vetrosa (Tg) e conduttività termica. Questi fattori influenzano il comportamento di un materiale nei processi di produzione e imballaggio, nonché il comportamento sul campo.

"Le sfide per i nostri materiali includono i limiti di temperatura dei diversi stampi", ha affermato Rama Puligadda, CTO di Scienza del birraio. “Dobbiamo garantire che le temperature utilizzate per l'incollaggio dei materiali non superino i limiti termici di nessuno dei chip integrati nel pacchetto. Inoltre, potrebbero esserci alcuni processi successivi come la formazione o lo stampaggio dello strato di ridistribuzione (RDL). I nostri materiali devono sopravvivere a questi processi. Devono sopravvivere alle sostanze chimiche con cui entrano in contatto durante tutto il processo di confezionamento. Le sollecitazioni meccaniche nel pacchetto aggiungono ulteriori sfide per l’incollaggio dei materiali”.

All'interno di una pila di chiplet su substrato con un interpositore opzionale, le loro caratteristiche materiali influiscono anche sulle sollecitazioni termico-meccaniche tra i materiali vicini. Ciò influisce direttamente sul controllo dimensionale dell'interconnessione su un'area del substrato di vasta area.

“Se si analizzano i numeri, si scoprirà che il livello di tolleranza e controllo richiesto è spaventoso”, ha affermato Dick Otte, CEO di Industrie Promex. "Stiamo parlando di dimensioni di controllo equivalenti alla larghezza di un filo d'erba sulla lunghezza di un campo di calcio, quindi è circa 1 su 100,000."

L'obiettivo è il riscaldamento uniforme della struttura in rifusione per ottenere i migliori risultati di processo ed evitare fessurazioni. "Quando lo si sottopone a uno sbalzo di temperatura di 250 gradi centigradi, è necessario riscaldarlo lentamente in modo che la parte superiore non si scaldi prima che lo faccia il fondo", ha detto Otte.

Multi-fisica per comprendere la co-ottimizzazione

La modellazione multifisica è diventata il metodo di riferimento per co-ottimizzare la progettazione del packaging e lo sviluppo del processo di assemblaggio. Ciò influisce sia sui materiali permanenti che temporanei, nonché sul posizionamento di processori, memorie e altri componenti.

“Si guarda sempre a ciò di cui il cliente ha bisogno dal punto di vista elettrico, perché questo aiuterà a definire il set di materiali. Il set di materiali è ampiamente applicabile a una serie di gamme di velocità. Finché non si esce da tali specifiche elettriche, in teoria dovrebbe essere tutto a posto", ha affermato Mike Kelly, vicepresidente dei pacchetti avanzati e dell'integrazione tecnologica presso Tecnologia Amkor.

Per evitare molte iterazioni di sviluppo basato empiricamente, gli ingegneri possono utilizzare simulazioni basate sulla fisica per comprendere l'impatto delle proprietà di un set di materiali sul processo di assemblaggio, sulla potenza/termica e sulle vibrazioni meccaniche.

Considera che i prodotti chiplet HPC possono consumare circa 1,000 watt alle massime prestazioni, quindi è necessario comprendere appieno le interazioni di potenza e termica.

"Abbiamo lottato, come tutti, con questa bufera di complessità nelle diverse tecniche. Non solo variano a seconda dei diversi fornitori, ma variano anche nel tempo", ha affermato Marc Swinnen, direttore del marketing di prodotto presso Ansis. “Il nostro approccio è stato quello di identificare gli elementi essenziali su cui è necessario lavorare. Lavoriamo insieme ai clienti per sviluppare un flusso di simulazione che realizzi effettivamente ciò che è necessario ora”.

I materiali sono solo un pezzo del puzzle. “Poi ci sono le sollecitazioni di assemblaggio che devono essere modellate per sapere se è possibile assemblare correttamente questo dispositivo. Il terzo è la vibrazione meccanica”, ha detto Swinnen. “Il tuo dispositivo può sopportare quelle vibrazioni regolari? La modellazione di questi attributi si collega direttamente ai nostri strumenti di analisi meccanica: acustica, termica, vibrazione, ecc. Alla fine, dovrai eseguire una simulazione fisica. Stiamo cercando di renderlo accessibile alle persone in molte forme diverse. Ma il fondamento della nostra offerta di strumenti è che disponiamo di ingranare simulazione e analisi. Si tratta di ottenere i dati nel formato giusto in un modo che sia pratico e utilizzabile."

Kit di progettazione di assiemi in evoluzione

Per i pacchetti convenzionali, gli OSAT forniscono regole di progettazione per ciascuna tecnologia di confezionamento. Questi devono considerare i requisiti di progettazione elettrica, meccanica e termica e le limitazioni del processo di produzione. In effetti questo è un riquadro di delimitazione multidimensionale. I fornitori eseguono iterazioni con il cliente per creare una ricetta di processo specifica per il prodotto.

Le regole coprono gli attributi di livello macro. "Come minimo, ciò che si vede dalle regole di progettazione è la dimensione massima del contenitore, la dimensione massima del silicio e se il silicio può essere [montato] su entrambi i lati del substrato, in modo tale che quando si seguono queste costruzioni il prodotto finale avrà una durata di vita di 1,000 cicli termici, per esempio”, spiega Braun del Fraunhofer.

Inoltre, le regole di progettazione devono descrivere i vincoli di instradamento per il interposto e / o strato di ridistribuzione, come la larghezza e gli spazi delle linee RDL, le dimensioni e i passi della griglia/pilastro/pad e il numero massimo di interconnessioni.

La suddivisione di un dispositivo HPC monolitico in più die sposta parte della complessità della progettazione/processo del semiconduttore nello spazio del packaging. Ciò rende le cose molto più complicate. Considerare che per connettere 10 die sono necessarie circa 100,000 tracce all'interno dello strato di ridistribuzione dell'interpositore o del substrato.

Per far fronte alla complessità a livello di chip, l'industria dei circuiti integrati si affida da tempo ai kit di progettazione dei processi (PDK) per acquisire le regole di progettazione in un file elettronico che può essere importato negli strumenti EDA. Le loro controparti, gli Assembly Design Kit (ADK), sono relativamente immaturi.

"Lo chiamiamo Smart Package", ha detto Kelly di Amkor. “È un ADK che diamo a ogni cliente che sta realizzando il proprio progetto. Si tratta di un insieme di macro e della personalizzazione di un database su misura per il progetto particolare del cliente. Per i chiplet, si tratta di una tecnologia di pacchetto fan-out ad alta densità. Ed è consapevole delle limitazioni relative alla densità e alla spaziatura dei metalli, ecc. Ciò ci rende più semplice eseguire i controlli delle regole di progettazione (DRC)."

Ma al momento, con il livello di personalizzazione ancora richiesto, il modo in cui viene derivato un ADK e ciò che comporta è in continuo cambiamento. Sono necessarie partnership tra fornitori di strumenti EDA, OSAT e fornitori di dispositivi a semiconduttore.

"Veniamo dal mondo dei circuiti integrati in cui tutto è molto rigido", ha affermato Kenneth Larsen, direttore della gestione dei prodotti 3D-IC in Synopsys"Gruppo EDA. “Dal punto di vista OSAT, e forse perché è così personalizzato, le regole di progettazione sembrano una scheda tecnica. Quindi costruisci e ottimizzi i prodotti nel tempo o in collaborazione con l'OSAT. Non è uno scambio elettronico. Nel mondo dei circuiti integrati, questo sarebbe del tutto inaudito. Sebbene sia possibile modificare alcune cose, è necessario un processo di qualificazione. E sembra che questo non sia ancora arrivato per il packaging."

I materiali e le ricette di assemblaggio associate determinano in definitiva ciò che è possibile fare per uno stack chiplet-substrato in termini di passo dei pilastri, larghezze e spazi delle linee RDL, processi di incollaggio e tolleranze di posizionamento dei chiplet. Ma all’interno di una manciata di ADK, ci sono molte possibili interazioni da considerare.

L'attenzione attuale è rivolta alla co-ottimizzazione della progettazione del sistema con il processo di assemblaggio dei chiplet, che porta a un flusso di sviluppo del processo di assemblaggio (vedere figura 4). Questo flusso considera le esigenze di personalizzazione di un processo di assemblaggio e crea le regole di progettazione necessarie che devono essere utilizzate dai progettisti di imballaggi.

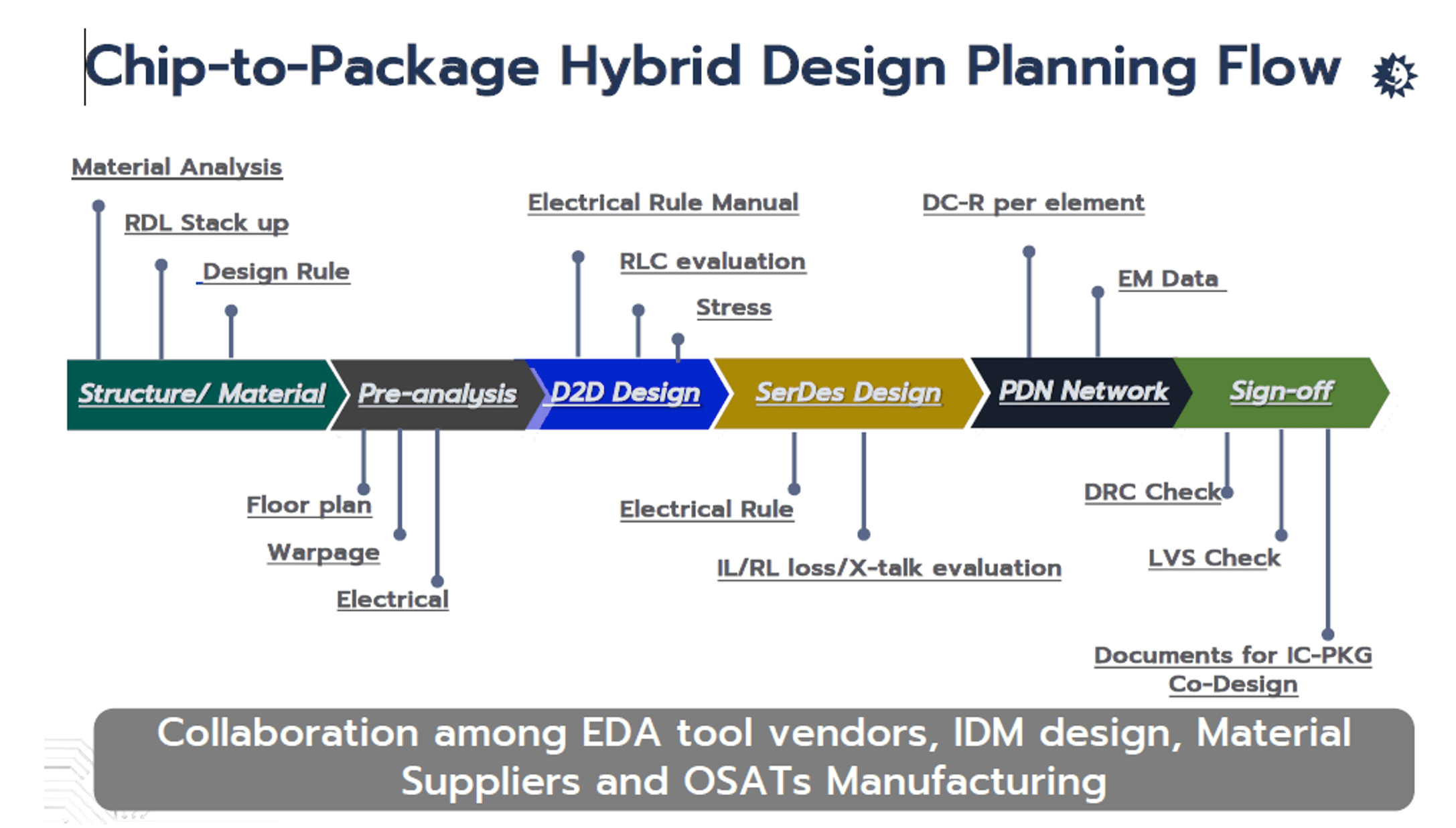

Fig. 4: Flusso ibrido chip-package. Fonte: ASE

“Per prima cosa devi definire la tua struttura utilizzando i chiplet. Stai utilizzando il substrato RDL, 2.5D RDL o un bridge? Dopodiché devi considerare i materiali della tua struttura. Che tipo di materiale scegli per soddisfare le tue prestazioni elettriche e i requisiti di stress meccanico", ha affermato Cao. "Dopodiché, esegui un'analisi preliminare per garantire che tutte le strutture e i materiali utilizzati siano utilizzabili in termini di stress elettrico, deformazione e meccanico."

Il flusso di pianificazione della progettazione include anche la valutazione delle interconnessioni die-to-die attraverso i documenti per l'approvazione della co-progettazione.

Conclusione

Prima che i progetti basati su chiplet possano essere abilitati al di fuori del modello IDM, il settore deve completare l’ecosistema che collega la complessità della produzione e della progettazione. Questo perché è essenziale la necessità di co-ottimizzare l’architettura del sistema in base a materiali, processi e capacità di integrazione. Sebbene ciò sarebbe più semplice con una serie di prodotti ben definiti su cui far avanzare l’ecosistema dei chiplet, ciò non è ancora accaduto.

I team di ingegneri a livello di progettazione e produzione dovranno collaborare per scegliere i materiali, le architetture, i processi ecc. appropriati per sviluppare un prodotto finale basato su chiplet che sia progettabile. Come ha osservato Cao del gruppo ASE, “Un ecosistema integrato di progettazione e produzione è importante. È molto fondamentale la collaborazione tra IDM, venditori e fornitori di materiali. Tutti devono lavorare insieme per consentire davvero l’integrazione delle applicazioni reali”.

ARTICOLI CORRELATI

Il packaging fan-out diventa competitivo

La producibilità raggiunge un livello sufficiente per competere con il flip-chip BGA e 2.5D.

Tecnologia fan-out interna a livello di pannello

Gli esperti del panel di Fraunhofer approfondiscono le ragioni per cui questo approccio è necessario e quali sono le sfide per farlo funzionare.

Passaggi successivi per l'imballaggio a livello di pannello

Dove sta funzionando e quali sfide rimangono per un'adozione ancora più ampia.

Mini-consorzi che si formano intorno ai chiplet

I mercati commerciali dei chiplet sono ancora all’orizzonte, ma le aziende stanno iniziando presto con partnership più limitate.

Cosa può andare storto nell'integrazione eterogenea

I flussi di lavoro e gli strumenti sono disconnessi, lo stress meccanico non è ben definito e la completa complanarità è quasi impossibile. Ma ci sono soluzioni all’orizzonte.

Le sfide meccaniche aumentano con l'integrazione eterogenea

Ma le lacune negli strumenti rendono difficile affrontare deformazioni, problemi strutturali e nuovi materiali nei progetti multi-die/multi-chiplet.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiengineering.com/what-works-best-for-chiplets/

- :ha

- :È

- :non

- :Dove

- $ SU

- 000

- 000 clienti

- 1

- 10

- 100

- 2%

- 2024

- 250

- 2D

- 3d

- 4

- a

- Chi siamo

- accettabile

- accessibile

- Raggiungere

- Realizza

- operanti in

- effettivamente

- aggiungere

- aggiunta

- aggiuntivo

- Inoltre

- indirizzo

- Adozione

- Avanzate

- Vantaggio

- influenzare

- colpisce

- Dopo shavasana, sedersi in silenzio; saluti;

- AI

- Sistemi di intelligenza artificiale

- allineamento

- Tutti

- lungo

- Alfabeto

- già

- anche

- sempre

- tra

- quantità

- an

- .

- analista

- ed

- in qualsiasi

- applicabile

- Applicazioni

- applicazioni

- applicato

- approccio

- opportuno

- architettonico

- architettura

- architetture

- SONO

- RISERVATA

- in giro

- AS

- montaggio

- associato

- At

- raggiungere

- gli attributi

- settore automobilistico

- evitare

- basato

- basic

- fondamentalmente

- BE

- perché

- diventare

- stato

- prima

- iniziare

- essendo

- MIGLIORE

- fra

- Big

- LAMA

- bufera di neve

- Blocchi

- entrambi

- Entrambe le parti

- Parte inferiore

- Scatola

- Rompere

- BRIDGE

- ponti

- più ampia

- in linea di massima

- costruire

- Mazzo

- affari

- ma

- by

- chiamata

- Materiale

- cao

- funzionalità

- catturare

- Custodie

- Causare

- centri

- ceo

- certo

- Challenge

- sfide

- il cambiamento

- Controlli

- chimico

- patata fritta

- Chips

- scelte

- Scegli

- la scelta

- codificata

- coefficienti

- consapevole

- collaboreranno

- collaborazione

- combinazione

- Venire

- Aziende

- competere

- completamento di una

- complesso

- complessità

- complicato

- componenti

- comprendere

- computer

- Visione computerizzata

- informatica

- conduttività

- Connettiti

- Collegamento

- Prendere in considerazione

- considerando

- ritiene

- vincoli

- costruzioni

- costruttivo

- consumare

- contatti

- contenere

- continua

- di controllo

- controllo

- convenzionale

- correttamente

- Costo

- omologhi

- accoppiato

- coprire

- screpolatura

- creare

- crea

- Creazione

- creazione

- critico

- CTO

- Corrente

- costume

- cliente

- le esigenze dei clienti

- Clienti

- personalizzazione

- personalizzate

- cicli

- dati

- data center

- Banca Dati

- definire

- definito

- richieste

- densità

- vice

- derivare

- derivato

- descrivere

- Design

- progettato

- designer e gli illustratori veneziani,

- disegni

- Nonostante

- dettaglio

- Determinare

- determinazione

- sviluppare

- sviluppato

- in via di sviluppo

- Mercato

- dispositivo

- dispositivi

- *

- diverso

- forme diverse

- difficile

- DIG

- dimensioni

- dirette

- direzione

- direttamente

- Direttore

- scollegato

- lontano

- Diversità

- do

- documenti

- effettua

- non

- fare

- Dont

- giù

- guidare

- e

- ogni

- Presto

- più facile

- Economico

- ecosistema

- effetto

- Elettronico

- empiricamente

- enable

- abilitato

- fine

- Ingegneria

- Ingegneri

- garantire

- assicurando

- comporta

- Ambiente

- usate

- Equivalente

- particolarmente

- essential

- essenziali

- eccetera

- valutazione

- Anche

- Evento

- Ogni

- tutti

- tutti

- qualunque cosa

- esempio

- superare

- exchange

- espansione

- previsto

- esperti

- strutture

- Fattori

- lontano

- pochi

- campo

- Fico

- figura

- Compila il

- filtri

- finale

- Trovare

- flusso

- flussi

- FLUSSO

- Focus

- seguire

- Calcio

- Nel

- formato

- formazione

- formando

- forme

- Forum

- Avanti

- da

- Adempiere

- soddisfatto

- completamente

- lacune

- generalmente

- ottenere

- si

- ottenere

- Dare

- vetro.

- Go

- scopo

- andando

- buono

- erba

- Gruppo

- Gruppo

- Crescere

- Crescita

- ha avuto

- manciata

- successo

- Hardware

- più duro

- Avere

- Aiuto

- Alta

- High-End

- alto livello

- Alte prestazioni

- superiore

- vivamente

- orizzonte

- HOT

- case

- Come

- Tutorial

- Tuttavia

- hpc

- HTTPS

- IBRIDO

- identificare

- Impact

- impatti

- importante

- impossibile

- in

- includere

- inclusi

- Compreso

- industria

- inizialmente

- Istituto

- integrato

- integrazione

- interezza

- Intel

- interazioni

- interconnessioni

- ai miglioramenti

- IP

- sicurezza

- IT

- iterazioni

- SUO

- ad appena

- solo uno

- kenneth

- Genere

- Sapere

- grandi

- strato

- stratificato

- disposizione

- principale

- meno

- Legale

- Aspetti legali

- Lunghezza

- Livello

- tutta la vita

- piace

- limiti

- Limitato

- linea

- Lunghi

- più a lungo

- cerca

- lotto

- a basso costo

- inferiore

- macro

- make

- FA

- Fare

- gestire

- gestione

- direttore

- Produttori

- consigliato per la

- molti

- Rappresentanza

- Marketing

- mercati

- sposare

- massiccio

- partita

- materiale

- Materiale

- max-width

- massimo

- Maggio..

- può essere

- meccanico

- memorie

- Memorie

- Menu

- metallo

- metodo

- metodologie

- metodi

- migrazione

- microfono

- ordine

- modello

- modellismo

- Monolitico

- Scopri di più

- cambiano

- in movimento

- molti

- multiplo

- moltitudine

- nomi

- quasi

- necessaria

- Bisogno

- di applicazione

- esigenze

- vicini

- internazionale

- New

- prodotti nuovi

- nodi

- noto

- adesso

- numero

- numeri

- of

- offrire

- offerte

- Va bene

- on

- una volta

- ONE

- esclusivamente

- aprire

- operare

- OTTIMIZZA

- Opzioni

- or

- minimo

- Altro

- nostro

- Risultato

- al di fuori

- ancora

- proprio

- pacchetto

- Packages

- imballaggio

- pannello di eventi

- parametri

- particolare

- partnership

- pcb

- Corrente di

- Persone

- eseguire

- performance

- permanente

- Fisica

- pezzo

- Pilastro

- Intonazione

- piazzole

- collocamento

- previsto

- pianificazione

- piattaforma

- Platone

- Platone Data Intelligence

- PlatoneDati

- punto

- pone

- possibile

- potenziale

- energia

- Pratico

- Prevedibile

- preparazione

- Presidente

- processi

- i processi

- processori

- Prodotto

- gestione del prodotto

- Prodotti

- proprietà

- proprio

- fornire

- fornitori

- fornisce

- Spingi

- Mettendo

- puzzle

- maglieria in

- domanda

- gamme

- raggiunge

- di rose

- mondo reale

- realtà

- veramente

- ricetta

- Ricette

- Ridotto

- Basic

- relazionato

- relativamente

- problemi di

- rimanere

- richiedere

- necessario

- Requisiti

- richiede

- risultante

- Risultati

- destra

- rigido

- Aumento

- strada

- approssimativamente

- instradamento

- Regola

- norme

- Suddetto

- Samsung

- Risparmi

- Scala

- schema

- Settori

- vedere

- sembrare

- sembra

- segmenti

- select

- semiconduttore

- anziano

- Sensibilità

- sensore

- set

- Set

- condiviso

- lei

- foglio

- Turni

- dovrebbero

- lato

- lati

- Signal

- Silicio

- simulazione

- simulazioni

- singolo

- SIX

- Taglia

- Lentamente

- smart

- So

- Soluzioni

- RISOLVERE

- alcuni

- a volte

- sofisticato

- zuppa

- Fonte

- lo spazio

- spazi

- specifico

- Specifiche tecniche

- velocità

- pila

- inizia a

- Di partenza

- step

- Passi

- Ancora

- stress

- strutturale

- La struttura

- strutture

- successivo

- sostanzialmente

- substrato

- il successo

- tale

- sufficiente

- fornitori

- sopravvivere

- sistema

- SISTEMI DI TRATTAMENTO

- su misura

- Fai

- presa

- parlando

- le squadre

- Consulenza

- tecniche

- Tecnologie

- Tecnologia

- telecomunicazioni

- temporaneo

- condizioni

- di

- che

- I

- loro

- Li

- poi

- teoricamente

- Là.

- termico

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- cose

- Terza

- questo

- quelli

- tre

- Attraverso

- per tutto

- Cravatte

- stretto

- strettamente

- tempo

- volte

- a

- oggi

- insieme

- tolleranza

- tolleranze

- strumenti

- top

- COMPLETAMENTE

- compromessi

- transizione

- Trend

- cerca

- tsmc

- pizzicare

- in definitiva

- per

- capire

- inteso

- su

- us

- utilizzabile

- uso

- utilizzato

- utilizzando

- varietà

- vario

- variare

- variando

- fornitori

- molto

- vice

- Vicepresidente

- visione

- visioni

- watt

- Modo..

- we

- WELL

- ben definita

- Che

- Che cosa è l'

- quando

- se

- quale

- while

- perché

- wikipedia

- volere

- con

- entro

- Lavora

- lavorare insieme

- lavorato

- lavoro

- lavori

- mondo

- preoccupato

- preoccuparsi

- sarebbe

- Wrong

- ancora

- dare la precedenza

- Tu

- Trasferimento da aeroporto a Sharm

- zefiro