Durante la scrittura il blog del mese scorso che utilizzava alcuni dei grafici di tendenza che abbiamo visto, ho notato che molti dati terminano nel 2020 o prima, ma ero troppo vicino alla scadenza per sedermi e apportare aggiornamenti ordinati ad alcuni grafici. Lavorando quotidianamente nell'area dell'integrazione SoC e delle reti su chip (NoC), il classico grafico basato su Karl Rupp ha ormai 50 anni come elaboratore di dati che sovrappone i transistor della legge di Moore con prestazioni a thread singolo, frequenza del processore, potenza tipica e numero di core del processore è rilevante, ma non del tutto perfetto. Sì, i core del processore sono essenziali, ma esistono molti altri tipi di blocchi IP in silicio (SIP) da collegare utilizzando NoC e integrare utilizzando ciò che noi di arteris chiama "Automazione dell'integrazione SoC".

Quindi, ho cercato i dati di origine rilevanti e ho sviluppato alcune nuove visualizzazioni.

Complessità del protocollo NoC

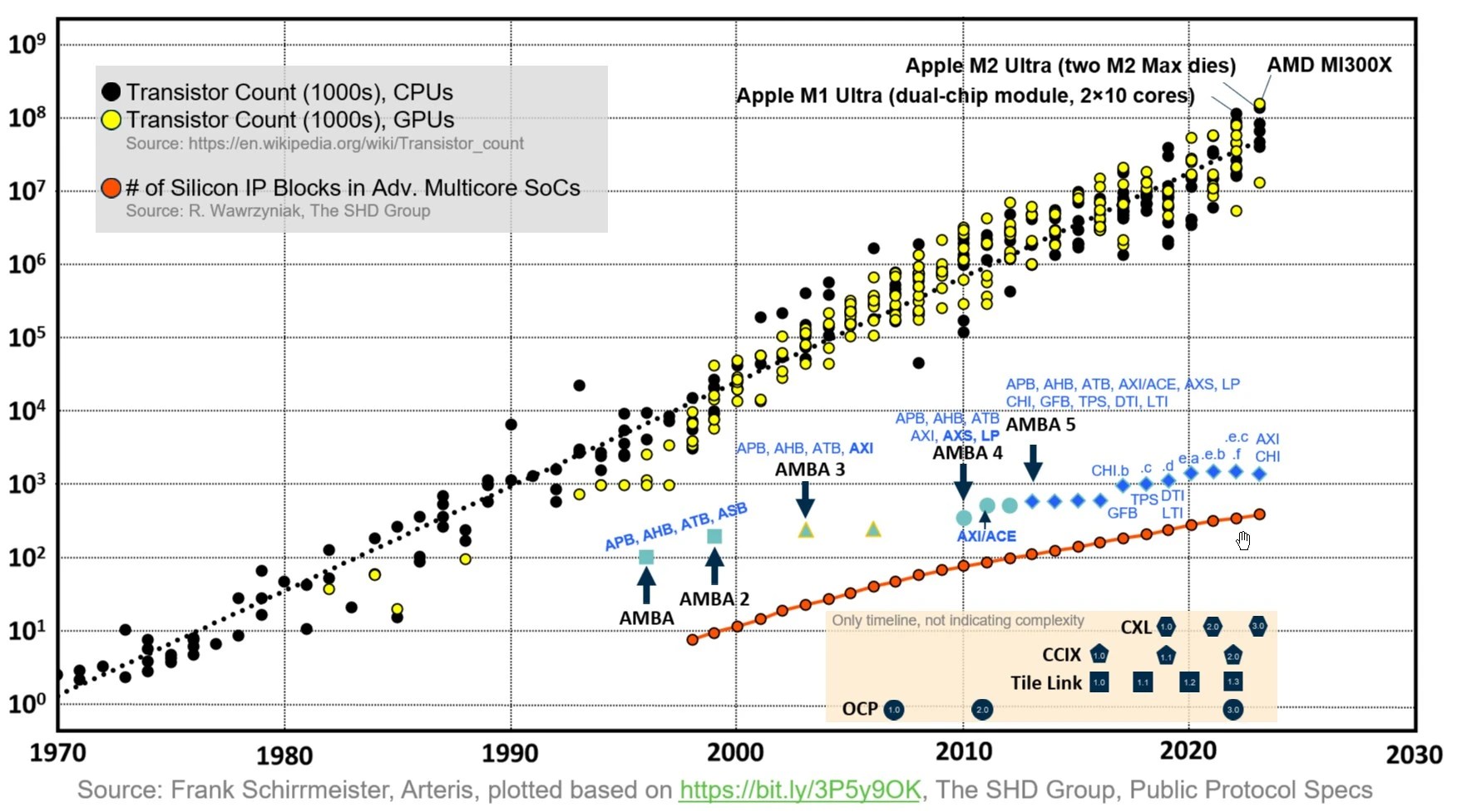

Innanzitutto, esaminiamo le NoC nel contesto della complessità. Il grafico seguente mostra l'evoluzione della complessità dei transistor come delineato nella tabella Pagina Wikipedia sui transistor. Ho separato CPU e GPU; quest’ultimo sta prendendo piede seriamente a metà degli anni ’1990. Non sorprende che questa parte del grafico mostri la legge di Moore senza considerare il costo dei transistor, che intendo sovrapporre in una versione futura.

I punti dati rossi rappresentano il numero di blocchi SIP, con il permesso di Richard Wawrzyniak di The SHD Group. Arriveremo a circa 400 blocchi SIP per SoC multicore avanzati nel 2023. Si noti che questo è su scala logaritmica, quindi all'inizio degli anni 2000, il settore era nelle due cifre inferiori per numero di blocchi SIP e il numero era in crescita veloce.

![]()

Fig. 1: Complessità dei transistor e della rete su chip (NoC) nel tempo.

Tutti questi blocchi SIP devono comunicare tra loro, il che ha dato origine allo sviluppo di protocolli per NoC. Il protocollo più importante è il Architettura bus avanzata del microcontrollore (AMBA). È un liberamente disponibile, standard aperto per connettere e gestire blocchi funzionali e grafici con la loro complessità misurata nel numero di pagine. La prima versione di AMBA, rilasciata nel 1996, includeva due bus, Advanced System Bus (ASB) e Advanced Peripheral Bus (APB), e aveva 106 pagine. La seconda versione, rilasciata nel 1999, aggiungeva l'AMBA High-performance Bus (AHB), un protocollo single clock-edge. Le specifiche avevano 204 pagine.

La terza versione di AMBA è stata rilasciata nel 2003 e ha introdotto AMBA Advanced eXtensible Interface (AXI), un protocollo multicanale ad alte prestazioni. Il numero totale di pagine è cresciuto fino a 260 pagine nel 2006. AMBA 4 è stato rilasciato nel 2010 e ha aggiunto i protocolli AMBA AXI Coherency Extensions (ACE) e AMBA Low-power Interface (LPI), che consentono la coerenza della cache e la gestione dell'alimentazione. Le specifiche sono cresciute fino a raggiungere un totale di 534 pagine nel 2012.

AMBA 5, l'ultima versione, rilasciata nel 2013, ha introdotto l'architettura AMBA Coherent Hub Interface (CHI), che definisce le interfacce per connettere processori pienamente coerenti e interconnessioni ad alte prestazioni. Ha inoltre esteso i protocolli precedenti per supportare nuove funzionalità come la qualità del servizio e le operazioni atomiche. Entro il 2023, il numero totale di pagine delle specifiche relative ad AMBA 5 è cresciuto fino a 1398, con varie versioni di CHI e specifiche di profili di traffico adattivi (contrassegnati come ATP), un protocollo GFP (Generic Flash Bus), un'interfaccia di traduzione distribuita (DTI) e un'interfaccia di traduzione locale (LTI), che definisce il protocollo punto a punto tra un dispositivo I/O e l'unità buffer lookaside di traduzione (TLBU) di un'unità di gestione della memoria del sistema Arm (SMMU).

A proposito, grazie ad Arm's Francisco Socal per il suo contributo a questo progetto. Mi avvertì che la complessità dell'AMBA sarebbe leggermente diminuita nel 2003 a causa della recente introduzione di AXI-J. Semplifica notevolmente il documento rimuovendo i contenuti legacy e AXI5 ora dispone di un'interfaccia generica che può essere configurata come ACE5-Lite, ACE5-LiteDVM e AXI5-Lite.

Se a questo punto hai, come me, i “TLA e FLA Blues” (acronimi di tre e quattro lettere), allora diventa chiaro che i NoC per AMBA richiedono competenze particolari. È qui che entriamo noi di Arteris con il nostro FlexNoC ed Ncore IP per protocolli non coerenti e coerenti.

Ma aspetta, c'è di più.

L'angolo in basso a destra del grafico sopra mostra la sequenza temporale dell'introduzione di altri quattro protocolli correlati:

- Il Protocollo Open Core (OCP) è uno standard per le interconnessioni su chip. È stato introdotto per la prima volta nel 2007 dal Consorzio SPIRIT. L'ultima versione, OCP 3.0, è stata rilasciata nel 2022.

- Il Protocollo TileLink NoC è uno standard per le interconnessioni su chip incentrato su RISC-V. È stato introdotto per la prima volta nel 2016 dalla Fondazione RISC-V. L'ultima versione, TileLink 1.3, è stata rilasciata nel 2022.

- Il Interconnessione coerente della cache per acceleratori (CCIX) è uno standard di interconnessione ad alta velocità per la connessione di processori, memoria e acceleratori, introdotto per la prima volta nel 2016.

- Il Compute Express Link (CXL) è uno standard di interconnessione ad alta velocità per la connessione di processori, memoria e acceleratori, introdotto per la prima volta nel 2019.

Il grafico mostra solo la complessità di questi protocolli come numero di pagine, solo le sequenze temporali, quindi vengono richiamati in un blocco diverso.

In conclusione: è un mondo complesso di NoC, fondamentali per abilitare SoC complessi e, sempre di più, progetti basati su chiplet.

Complessità di integrazione del SoC

Bene, ora hai molti blocchi SIP commerciali e tutti i tuoi blocchi differenzianti. Dove andare da qui? L'automazione dell'integrazione del SoC è la risposta. Il grafico seguente mostra come il settore ha reagito e continua a reagire alla crescente complessità e al numero crescente di blocchi SIP nel tempo:

![]()

Fig. 2: Complessità dell'integrazione di transistor e SoC nel tempo.

Questo grafico ripete la complessità dei transistor e il numero di blocchi SIP descritti sopra. Ma ora si sovrappone ai tentativi e agli standard che riguardano l'assemblaggio del SoC, cioè la gestione della marea di blocchi RTL, sia acquisiti commercialmente che sviluppati internamente. IP-XACT è il termine fondamentale da ricordare qui.

Come illustrato, la VSI Alliance era un'organizzazione fondata nel 1996 per migliorare la produttività della comunità di progettazione SoC fornendo standard e soluzioni per il riutilizzo della proprietà intellettuale. Il Consorzio SPIRIT è stata un'altra organizzazione fondata nel 2003 per sviluppare e specificare lo standard IP-XACT, un formato XML per descrivere componenti e progetti IP. Nel 2008, la VSI Alliance e il Consorzio SPIRIT si sono fusi in Accellera, un'associazione di settore dedicata alla creazione di standard di progettazione e verifica. Accellera mantiene e aggiorna lo standard IP-XACT.

Il 2004 ha segnato il rilascio di IP-XACT 1.0 come prima versione di IP-XACT. Si è concentrato sulla descrizione del comportamento del livello di trasferimento di registro (RTL) dei blocchi SIP. Quindi, nel 2005, la versione 1.1 ha aggiunto il supporto per definire il comportamento del modello TLM (transaction-level modeling) del blocco SIP; nel 2006, la versione 1.2 ha aggiunto il supporto per descrivere l'implementazione fisica dei blocchi IP. La versione 1.4 ha aggiunto il supporto per definire la verifica dei blocchi IP nel 2008. Dopo la fusione, IEEE Std. 1685-2009 è stata la prima versione di IP-XACT approvata dall'IEEE nel 2009. IEEE Std. 1685-2014 ha aggiunto il supporto per descrivere la sicurezza dei blocchi IP. Oggi, l'ultima versione di IP-XACT, IEEE Std. 1685-2022, supporta la definizione delle estensioni del fornitore dei blocchi SIP.

Outlook

Mentre i grafici illustrano le tendenze che portano ad oggi, al 2023, sia i progetti SoC che quelli basati su chiplet stanno diventando sempre più complessi da qui. I protocolli NoC diventeranno più complessi e il mare di blocchi RTL da collegare diventa sempre più profondo ed esteso. Vuoi eseguire il refactoring manuale di RTL durante la ridefinizione delle regioni di potenza? No, non lo fai! È qui che entra in gioco l'automazione dell'integrazione SoC basata su IP-XACT.

Il riutilizzo SIP NoC e l'automazione dell'integrazione SoC basata su IP-XACT sono fondamentali per tenere sotto controllo i costi di progettazione e aumentare la produttività per l'età d'oro dei semiconduttori!

Frank Schirmeister

(tutti i post)

Frank Schirrmeister è vicepresidente delle soluzioni e dello sviluppo aziendale di Arteris. Dirige attività nei settori verticale automobilistico, data center, comunicazioni 5G/6G, mobile, aerospaziale e data center e le tecnologie orizzontali intelligenza artificiale, apprendimento automatico e sicurezza. Prima di Arteris, Schirrmeister ha ricoperto varie posizioni dirigenziali presso Cadence Design Systems, Synopsys e Imperas, concentrandosi su marketing e gestione dei prodotti, soluzioni, iniziative strategiche dei partner dell'ecosistema e coinvolgimento dei clienti.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Automobilistico/VE, Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Grafico Prime. Migliora il tuo gioco di trading con ChartPrime. Accedi qui.

- BlockOffset. Modernizzare la proprietà della compensazione ambientale. Accedi qui.

- Fonte: https://semiengineering.com/design-complexity-in-the-golden-age-of-semiconductors/

- :ha

- :È

- :non

- :Dove

- $ SU

- 1

- 1.3

- 1996

- 1999

- 2005

- 2006

- 2008

- 2009

- 2010

- 2012

- 2013

- 2016

- 2019

- 2020

- 2022

- 2023

- 50

- 50 anni

- 80

- a

- WRI

- sopra

- acceleratori

- asso

- acquisito

- Acronimi

- attività

- aggiunto

- Avanzate

- Aeronautico

- Dopo shavasana, sedersi in silenzio; saluti;

- Tutti

- Tutti i messaggi

- alleanza

- anche

- an

- ed

- Un altro

- rispondere

- approvato

- architettura

- SONO

- RISERVATA

- ARM

- in arrivo

- artificiale

- intelligenza artificiale

- AS

- montaggio

- Associazione

- At

- Tentativi

- Automazione

- settore automobilistico

- disponibile

- basato

- BE

- diventare

- diventa

- prima

- comportamento

- sotto

- fra

- Bloccare

- Blocchi

- entrambi

- Parte inferiore

- bufferizzare

- autobus

- Gli autobus

- affari

- sviluppo commerciale

- ma

- by

- nascondiglio

- Cadenza

- chiamata

- detto

- Materiale

- centro

- Grafico

- Grafici

- dai un'occhiata

- classico

- pulire campo

- Chiudi

- COERENTE

- viene

- arrivo

- commercialmente

- Comunicazioni

- comunità

- complesso

- complessità

- componenti

- configurato

- Connettiti

- collegato

- Collegamento

- considerando

- consorzio

- contenuto

- contesto

- Nucleo

- Costo

- Costi

- Creazione

- critico

- cliente

- Il coinvolgimento del cliente

- dati

- Banca dati

- punti dati

- giorno per giorno

- affare

- dedicato

- definisce

- definizione

- definizione

- descritta

- Design

- sistemi di progettazione

- disegni

- sviluppare

- sviluppato

- Mercato

- dispositivo

- diverso

- cifre

- distribuito

- do

- documento

- giù

- Cadere

- DTI

- dovuto

- e

- ogni

- In precedenza

- Presto

- ecosistema

- enable

- consentendo

- finisce

- Fidanzamento

- accrescere

- essential

- evoluzione

- competenza

- esprimere

- estensioni

- estensivo

- FAST

- Caratteristiche

- Nome

- Cromatografia

- concentrato

- messa a fuoco

- Nel

- formato

- Fondazione

- Fondato

- quattro

- franco

- Frequenza

- da

- completamente

- funzionale

- futuro

- ottenere

- Go

- d'oro

- GPU

- è cresciuto

- Gruppo

- Crescita

- cresciuto

- ha avuto

- Avere

- he

- Eroe

- quindi

- qui

- Alta

- Alte prestazioni

- il suo

- Come

- HTTPS

- Hub

- i

- IEEE

- implementazione

- in

- incluso

- crescente

- industria

- iniziative

- ingresso

- integrato

- integrazione

- Intelligence

- interconnessioni

- Interfaccia

- interfacce

- internamente

- ai miglioramenti

- introdotto

- Introduzione

- IP

- IT

- SUO

- jpg

- conservazione

- con i più recenti

- Legge

- Leadership

- principale

- Leads

- apprendimento

- Eredità

- Livello

- piace

- linea

- LINK

- locale

- Guarda

- guardò

- lotto

- inferiore

- macchina

- machine learning

- mantiene

- make

- gestire

- gestione

- manualmente

- molti

- segnato

- Marketing

- max-width

- me

- misurato

- Memorie

- Fusione

- Mobile

- modellismo

- Scopri di più

- maggior parte

- Bisogno

- New

- Nuove funzionalità

- no

- Nota

- adesso

- numero

- of

- on

- esclusivamente

- aprire

- Operazioni

- or

- organizzazione

- Altro

- nostro

- su

- delineato

- ancora

- pagina

- pagine

- parte

- particolare

- partner

- perfetta

- performance

- periferico

- autorizzazione

- foto

- Fisico

- piano

- Platone

- Platone Data Intelligence

- PlatoneDati

- punto

- punti

- posizioni

- Post

- energia

- Presidente

- Precedente

- Processore

- processori

- Prodotto

- della produttività

- Profili

- profonda

- progetto

- prominente

- protocollo

- protocolli

- fornitura

- qualità

- recente

- Rosso

- Ridefinendo

- Refactoring

- regioni

- relazionato

- rilasciare

- rilasciato

- pertinente

- ricorda

- rimozione

- richiedere

- riutilizzare

- Richard

- destra

- Sicurezza

- Scala

- MARE

- Secondo

- problemi di

- visto

- Semiconduttori

- anziano

- dirigenza senior

- servizio

- Spettacoli

- significativamente

- Silicio

- singolo

- sedere

- So

- Soluzioni

- alcuni

- Fonte

- specificazione

- occhiali

- spirito

- Standard

- standard

- Ancora

- Strategico

- tale

- supporto

- supporti

- sistema

- SISTEMI DI TRATTAMENTO

- Parlare

- Tecnologia

- termine

- Grazie

- che

- Il

- L'area

- la sicurezza

- poi

- Là.

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- Terza

- questo

- tre

- miniature

- tempo

- time line

- timeline

- TLM

- a

- oggi

- pure

- Totale

- traffico

- Traduzione

- Trend

- tendenze

- seconda

- Tipi di

- tipico

- unità

- Aggiornamenti

- utilizzato

- utilizzando

- vario

- venditore

- Convalida

- versione

- versioni

- verticali

- vice

- Vicepresidente

- aspettare

- volere

- Prima

- Modo..

- we

- WebP

- Che

- quando

- quale

- wikipedia

- volere

- con

- senza

- lavoro

- mondo

- sarebbe

- scrittura

- XML

- anni

- sì

- Tu

- Trasferimento da aeroporto a Sharm

- zefiro