Strumentare la convalida post-silicio non è un'idea nuova, ma ecco una svolta. Utilizzo dell'emulazione (pre-silicio) per scegliere le strutture di osservazione del debug da strumentare in silicio. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, imprenditore, ex Synopsys CTO) e io continuiamo la nostra serie sulle idee di ricerca. Come sempre, feedback graditi.

![]()

L'innovazione

La scelta di questo mese è Infrastruttura di emulazione per la valutazione di asserzioni hardware per la convalida post-silicone. Il documento è stato presentato alle IEEE Transactions on VLSI 2017. Gli autori provengono dalla McMaster University, Hamilton, ON, Canada

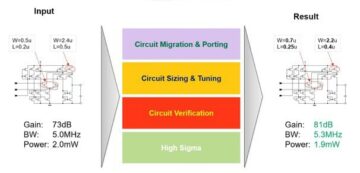

Gli autori distinguono tra errori logici ed elettrici post-silicio e dedicano la loro attenzione in questo articolo agli errori elettrici, rilevabili tramite bit-flip in flop. Il loro approccio consiste nel determinare un insieme ottimale di asserzioni nell'analisi pre-silicio. Questi vengono poi implementati in silicio a supporto del debug post-silicio. L'analisi pre-silicio è simile all'errore nelle analisi di sicurezza, poiché inietta errori su flop corrispondenti a errori elettrici, come suggeriscono nel documento. Generano un elenco di asserzioni candidate utilizzando la sintesi di asserzioni; il nucleo della loro innovazione è fornire un metodo per valutare queste asserzioni in base all'efficacia di ciascuna nel rilevare più errori.

La generazione di input è casuale, analizzando i guasti iniettati (trattati come transitori) in sequenza. Consentono un numero di cicli specificato dall'utente per il rilevamento per guasto. In una fase successiva, misurano l'efficacia utilizzando due diverse tecniche di copertura. Per la copertura flip-flop, contano un'asserzione se rileva un errore iniettato su qualsiasi flop. Nella copertura bit-flip, assegnano un punteggio alle asserzioni sul numero di errori rilevati su flop separati. Queste metriche, insieme alle stime dell'area, usano (in alternativa) per selezionare quali asserzioni preferite.

Il punto di vista di Paolo

Questa carta si abbina bene con il nostro Blog di agosto 2020 sul rilevamento rapido degli errori (QED). QED accelera il rilevamento dei bug funzionali post-silicio, in cui questo blog si concentra sul rilevamento dei bug elettrici post-silicio. Il documento è di facile lettura, anche se aiuta a leggere prima il riferimento [23].

I bug elettrici sono difficili da rilevare e, anche in questo caso, sono difficili da replicare e trovare la causa fisica sottostante. Gli autori propongono un metodo, attraverso la logica incorporata, per rilevare quando tali bug causano il ribaltamento di un flop a un valore errato (non scavano più a fondo che trovare questi ribaltamenti).

Il cuore del documento e il suo riferimento complementare [23] è un metodo a più fasi per creare e sintetizzare questa logica di rilevamento. Inizia con le proprietà minerarie del design come asserzioni temporali utilizzando il Strumento GoldMine. Classificano le asserzioni in base a una stima della loro capacità di rilevare i bit flip e una stima dell'area / costo del cablaggio da implementare nel silicio. La classifica si basa sull'esecuzione di molte simulazioni pre-silicio con asserzioni candidate, sull'inserimento di errori di rotazione dei bit e sul conteggio dei lanci rilevati in base alle asserzioni. Nel documento originale utilizzavano la simulazione logica, qui accelerano queste simulazioni mappando il progetto su una scheda FPGA Altera.

Mi piace il modo in cui mettono insieme diverse innovazioni in un metodo coerente per il rilevamento del bit flip post-silicio: mining di asserzioni, sintesi di asserzioni e un'elegante funzione di classificazione per la selezione di asserzioni. Tuttavia, la sezione dei risultati dell'articolo indica che il rilevamento di ribaltamenti di bit nell'n% dei flip-flop richiede circa un aumento dell'n% nell'area di progettazione. Questo sembra impegnativo per l'applicazione commerciale, soprattutto perché aiuta solo a trovare bug elettrici. Si potrebbe potenzialmente ottenere un risultato simile clonando il cono logico che guida un flip-flop, quindi confrontare l'output di questa logica clonata con la logica originale. Ciò sembrerebbe generare un sovraccarico di area simile al loro metodo, clonando al limite l'intero progetto (cioè il 100% di sovraccarico dell'area) per rilevare i flip nel 100% dei flop nel progetto.

Il punto di vista di Raull

Il documento è autonomo con una discreta quantità di dettagli. Gli autori hanno condotto esperimenti per 3 circuiti sequenziali ISCAS (ca. 12K gate, 2000 FF). Gli esperimenti di preparazione iniettano 256 errori per flip flop e utilizzano tutte le asserzioni generate da GoldMine. A causa della capacità limitata dell'FPGA, gli autori hanno suddiviso le corse in 45 "sessioni" per un circuito. I risultati mostrano, anche con 45 sessioni, un'accelerazione dell'analisi rispetto alla simulazione di 20-500 volte (solo fino a 8 iniezioni di errore perché la simulazione diventa troppo lenta, 105 ore). La massima copertura Flip-Flop ottenibile è del 55%, 89% e 99% per i 3 circuiti. Il numero di asserzioni estratte controlla la copertura.

L'esecuzione con asserzioni selezionate (corrispondenti a un sovraccarico dell'area del 5-50%) e 1-256 iniezioni comporta una copertura di bit del 2.2%-34%. Il più delle volte, il minatore di asserzioni è stato eseguito per 228 ore. Una cosa che mi ha confuso sono i loro dati per i tempi di esecuzione rispetto agli errori inseriti. L'aumento sembra ragionevole (lineare) nella simulazione. Ma in emulazione salta in modo massiccio, da 0.045h a 5.4h per un aumento da 2 a 8 iniezioni di errore. Vorrei maggiori spiegazioni su questo punto.

Questo è un documento di metodologia. Mi piace che praticamente ogni passaggio possa essere sostituito da uno strumento commerciale. Insieme all'utilizzo di una grande scheda FPGA (come emulatore), la metodologia scala. Le metodologie sono ovviamente molto difficili da commercializzare, ma è una bella applicazione per la tecnologia esistente!

La mia opinione

Il metodo per esplorare una tecnica di analisi della sicurezza per il debug post-silicio è interessante. Un'idea nuova, anche se porta a un risultato alquanto poco pratico per l'applicazione commerciale.

Condividi questo post tramite: Fonte: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Tutti

- .

- Applicazioni

- RISERVATA

- gli autori

- Po

- Blog

- tavola

- Insetto

- bug

- Cadenza

- Ultra-Grande

- lotta

- Causare

- continua

- CTO

- dati

- Design

- dettaglio

- rivelazione

- guida

- Efficace

- Imprenditore

- stime

- fiera

- Nome

- FPGA

- function

- Gates

- GM

- Hardware

- qui

- Come

- HTTPS

- idea

- IEEE

- Aumento

- Infrastruttura

- Innovazione

- IT

- grandi

- principale

- Limitato

- Lista

- misurare

- Metrica

- Siti di estrazione mineraria

- Carta

- offre

- riparazioni

- Risultati

- running

- Sicurezza

- selezionato

- Serie

- set

- simulazione

- dividere

- supporto

- tempo

- Le transazioni

- twist

- Università

- APPREZZIAMO

- Convalida

- contro