Achronix è noto per le sue soluzioni FPGA ad alte prestazioni. In questo post, esplorerò l'FPGA Speedster7T. Questa famiglia di FPGA è ottimizzata per carichi di lavoro a larghezza di banda elevata ed elimina i colli di bottiglia delle prestazioni con un'architettura innovativa. Basata sul processo FinFET a 7 nm di TSMC, la famiglia offre prestazioni di livello ASIC pur mantenendo la piena programmabilità di un FPGA. C'è molto da imparare sullo Speedster7T. Achronix ora ha un video disponibile che risponderà a molte di queste domande. C'è un collegamento a quel video e altri in arrivo, ma prima vediamo cosa succede quando si porta l'FPGA Achronix Speedster7t per un giro di prova in laboratorio.

Achronix è noto per le sue soluzioni FPGA ad alte prestazioni. In questo post, esplorerò l'FPGA Speedster7T. Questa famiglia di FPGA è ottimizzata per carichi di lavoro a larghezza di banda elevata ed elimina i colli di bottiglia delle prestazioni con un'architettura innovativa. Basata sul processo FinFET a 7 nm di TSMC, la famiglia offre prestazioni di livello ASIC pur mantenendo la piena programmabilità di un FPGA. C'è molto da imparare sullo Speedster7T. Achronix ora ha un video disponibile che risponderà a molte di queste domande. C'è un collegamento a quel video e altri in arrivo, ma prima vediamo cosa succede quando si porta l'FPGA Achronix Speedster7t per un giro di prova in laboratorio.

Steve Mensor, vicepresidente vendite e marketing di Achronix, presenta il video. Steve è stato con Achronix per quasi dieci anni e prima ha trascorso 21 anni ad Altera. Sicuramente sa molto sugli FPGA: progettazione e applicazione. Steve inizia delineando alcuni degli elementi dell'architettura innovativa menzionata in precedenza. Ci sono molte capacità dedicate a bordo dello Speedster7T. Ciò comprende:

- SerDe da 112 Gbps

- 400G Ethernet

- PCIe Gen5

- GDDR6 in esecuzione a 4 Tbps

- DDR 4 in esecuzione a 3,200 Mbps

- Un processore di machine learning proprietario

- Rete 2D su chip (NoC)

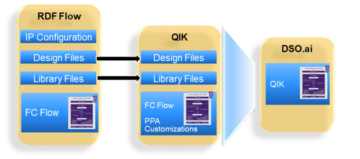

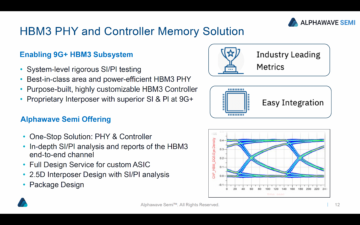

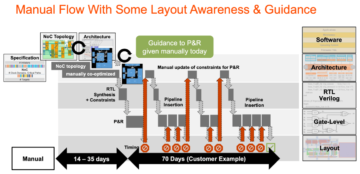

Il processore di apprendimento automatico proprietario offre molte funzionalità, tra cui operazioni in virgola mobile, blocco in virgola mobile e numeri interi. Il 2D NoC è una funzionalità nuova nel settore per gli FPGA di Achronix. Il NoC può instradare i dati da qualsiasi interfaccia ad alta velocità al fabric FPGA principale a 2 GHz senza consumare nessuna delle risorse logiche FPGA. Tutta questa tecnologia integrata consente di ottenere prestazioni di livello ASIC in un FPGA.

Steve passa quindi la presentazione a Katie Purcell, responsabile dell'ingegneria delle applicazioni presso Achronix. Katie lavora con Achronix da quattro anni. In precedenza era una progettista ASIC. Ha anche trascorso del tempo a Xilinx. Katie è quella che porta l'FPGA Speedster7t a fare un giro di prova in laboratorio, ed è decisamente all'altezza della sfida.

Katie porta lo spettatore nel laboratorio Achronix dove viene eseguito il pull-up dello Speedster7T: convalida e caratterizzazione. La demo presentata da Katie mostra il dispositivo che esegue traffico Ethernet 400G sul Scheda acceleratore Achronix VectorPath. Katie inizia riassumendo gli elementi chiave della dimostrazione, che includono:

- Interfaccia esterna 8 X 50G

- Singola interfaccia 400G nel sottosistema Ethernet

- Dati divisi in quattro flussi separati nel NoC 2D

- Ogni flusso è stato elaborato in modo indipendente

Katie passa un po' di tempo sul 2D NoC. Sottolinea che questa capacità rende il design più semplice e più facile da chiudere i tempi. Questo NoC 2D unico è apparso diverse volte durante la demo. Vale la pena scavare un po' di più per capirlo. Achronix ha presentato in precedenza un webinar su questa capacità unica che era coperto su SemiWiki detto 5 motivi per cui uno SmartNIC riconfigurabile ad alte prestazioni richiede un NoC 2D. La buona notizia è che ora è disponibile un replay di questo webinar molto informativo. Puoi vederlo qui.

Katie ti guida attraverso uno sguardo dettagliato a cosa sta succedendo all'interno del dispositivo Speedster7T mentre elabora i pacchetti di dati. Conoscere questi dettagli aiuta a comprendere la facilità di installazione e la precisione fornita che viene mostrata durante la demo. Se pensi che un dispositivo unico come questo possa aiutare il tuo progetto di design, ti consiglio vivamente di guardare la demo. È breve, ma molto utile. Puoi accedere al video dimostrativo qui.

Ora sai come portare l'FPGA Achronix Speedster7t a fare un giro di prova in laboratorio. Puoi trovare maggiori dettagli su questo unica famiglia FPGA qui.

Condividi questo post tramite: Fonte: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- acceleratore

- Tutti

- Applicazioni

- architettura

- ASIC

- Po

- tavola

- Challenge

- patata fritta

- arrivo

- dati

- Design

- Designer

- Ingegneria

- tessuto

- famiglia

- Nome

- FPGA

- pieno

- buono

- Alta

- Come

- Tutorial

- HTTPS

- Compreso

- creativi e originali

- IT

- Le

- IMPARARE

- apprendimento

- LINK

- machine learning

- Marketing

- Rete

- notizie

- Operazioni

- performance

- progetto

- motivi

- Risorse

- strada

- running

- vendite

- Corti

- Soluzioni

- Tecnologia

- test

- tempo

- traffico

- Video

- Orologio

- webinar

- OMS

- valore

- X

- anni