포스트 실리콘 검증을 계측하는 것은 새로운 아이디어는 아니지만 여기에 반전이 있습니다. (실리콘 전) 에뮬레이션을 사용하여 실리콘 내 계측을 위한 디버그 관찰 구조를 선택합니다. Paul Cunningham(GM, Verification at Cadence), Raúl Camposano(실리콘 촉매, 기업가, 전 Synopsys CTO)와 저는 연구 아이디어에 대한 시리즈를 계속합니다. 언제나처럼 피드백을 환영합니다.

![]()

혁신

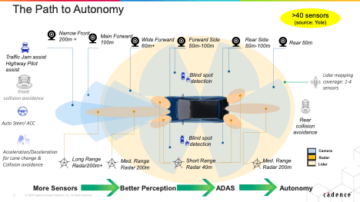

이번 달의 선택은 실리콘 이후 검증을 위한 하드웨어 어설션 평가를 위한 에뮬레이션 인프라. 이 논문은 2017 IEEE Transactions on VLSI에서 발표되었습니다. 저자는 캐나다 온타리오 주 해밀턴 소재 McMaster University 출신입니다.

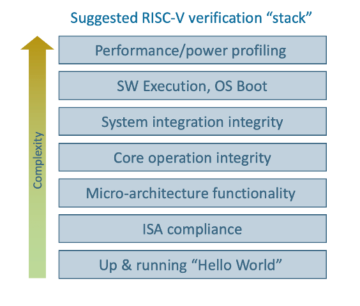

저자는 실리콘 이후의 논리적 오류와 전기적 오류를 구별하고 본 논문에서는 플롭의 비트플립을 통해 감지할 수 있는 전기적 오류에 집중했습니다. 그들의 접근 방식은 실리콘 이전 분석에서 최적의 주장 세트를 결정하는 것입니다. 그런 다음 실리콘 이후 디버그를 지원하기 위해 이를 실리콘으로 구현합니다. 실리콘 전 분석은 안전 분석의 결함과 유사하며, 논문에서 암시하는 것처럼 전기적 오류에 해당하는 플롭에 결함을 주입합니다. 어설션 합성을 사용하여 어설션 후보 목록을 생성합니다. 혁신의 핵심은 이러한 주장이 여러 결함을 감지하는 데 얼마나 효과적인지에 따라 등급을 매기는 방법을 제공하는 것입니다.

입력 생성은 무작위로 이루어지며 주입된 결함(일시적인 것으로 처리됨)을 순차적으로 분석합니다. 이는 오류당 감지를 위해 사용자가 지정한 주기 수를 허용합니다. 후속 단계에서는 두 가지 서로 다른 적용 범위 기술을 사용하여 효율성을 측정합니다. 플립플롭 적용 범위의 경우 플롭에서 주입된 오류를 포착하면 어설션을 계산합니다. 비트플립 적용 범위에서는 별도의 플롭에서 감지된 오류 수에 대한 어설션 점수를 매깁니다. 이러한 측정항목은 면적 추정치와 함께 (또는) 선호하는 주장을 선택하는 데 사용됩니다.

바울의 견해

이 논문은 우리의 논문과 잘 어울립니다. 빠른 오류 감지에 관한 2020년 XNUMX월 블로그 (QED). QED는 포스트 실리콘 기능 버그 감지를 가속화합니다. 이 블로그에서는 포스트 실리콘 전기 버그 감지에 중점을 둡니다. 이 논문은 쉽게 읽을 수 있지만 먼저 참고문헌 [23]을 읽는 데 도움이 됩니다.

전기적 버그는 잡기 어렵고, 심지어 근본적인 물리적 원인을 복제하고 찾기도 어렵습니다. 저자는 내장된 로직을 통해 이러한 버그로 인해 플롭이 잘못된 값으로 반전되는 경우를 감지하는 방법을 제안합니다(이러한 플립을 찾는 것보다 더 깊이 파고들지는 않습니다).

논문의 핵심과 동반 참고문헌[23]은 이 탐지 논리를 생성하고 합성하는 다단계 방법입니다. 이는 설계의 마이닝 속성을 사용하여 시간적 주장으로 시작합니다. 금광 도구. 그들은 비트 플립을 감지하는 능력에 대한 추정치와 실리콘에서 구현하기 위한 면적/배선 비용의 추정치를 기반으로 주장의 순위를 매깁니다. 순위 지정은 후보 어설션을 사용하여 많은 실리콘 이전 시뮬레이션을 실행하고, 비트 플립 오류를 주입하고, 어설션별로 감지된 플립 수를 계산하는 데 의존합니다. 원래 논문에서는 논리 시뮬레이션을 사용했지만 여기서는 설계를 Altera FPGA 보드에 매핑하여 이러한 시뮬레이션을 가속화했습니다.

나는 그들이 몇 가지 혁신을 포스트 실리콘 비트 플립 감지를 위한 일관된 방법(어설션 마이닝, 어설션 합성 및 어설션 선택을 위한 우아한 순위 기능)으로 통합하는 방법을 좋아합니다. 그러나 논문의 결과 섹션에서는 n%의 플립플롭에서 비트 플립을 감지하려면 설계 영역에서 대략 n%의 증가가 필요하다는 것을 나타냅니다. 이는 특히 전기적 버그를 찾는 데만 도움이 되므로 상업적인 적용에는 어려운 것 같습니다. 플립플롭을 구동하는 로직 콘을 복제한 다음 이 복제된 로직의 출력을 원래 로직과 비교하면 유사한 결과를 얻을 수 있습니다. 이는 설계에 있는 플롭의 100%에서 플립을 감지하기 위해 전체 설계(즉, 100% 영역 오버헤드)를 복제하는 한계에서 그들의 방법과 유사한 영역 오버헤드를 생성하는 것처럼 보입니다.

라울의 견해

이 논문은 상당한 양의 세부 사항을 포함하고 있습니다. 저자는 3개의 ISCAS 순차 회로(약 12K 게이트, 2000FF)에 대한 실험을 실행했습니다. 준비 실험에서는 GoldMine에서 생성된 모든 어설션을 사용하여 플립플롭당 256개의 오류를 주입합니다. FPGA의 제한된 용량으로 인해 저자는 하나의 회로에 대해 45개의 "세션"으로 실행을 분할했습니다. 결과는 45개 세션에서도 20~500회 시뮬레이션에 대한 분석 가속화를 보여줍니다(시뮬레이션이 너무 느려지므로 최대 8회 오류 주입, 105시간만 가능). 달성 가능한 최대 플립플롭 범위는 55개 회로에 대해 89%, 99%, 3%입니다. 마이닝된 주장의 수는 적용 범위를 제어합니다.

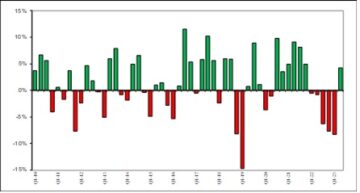

선택한 어설션(5~50% 영역 오버헤드에 해당)과 1~256회 주입으로 실행하면 2.2%~34%의 비트 적용 범위가 발생합니다. 대부분의 경우 어설션 마이너는 228시간 동안 실행되었습니다. 저를 혼란스럽게 했던 한 가지는 런타임과 오류에 대한 데이터가 주입되었다는 것입니다. 시뮬레이션에서는 증가가 합리적(선형)으로 보입니다. 그러나 에뮬레이션에서는 오류 주입이 0.045회에서 5.4회로 증가하여 2h에서 8h로 대폭 향상됩니다. 이 점에 대해 더 많은 설명을 듣고 싶습니다.

방법론 논문입니다. 나는 거의 모든 단계를 상용 도구로 대체할 수 있다는 점을 좋아합니다. 대형 FPGA 보드(에뮬레이터)를 사용하면 방법론이 확장됩니다. 방법론은 물론 상용화하기가 매우 어렵지만 기존 기술에 대한 훌륭한 응용 프로그램입니다!

내 견해

포스트 실리콘 디버그를 위한 안전성 분석 기술을 탐색하는 방법은 매우 흥미롭습니다. 비록 상업적인 적용에는 다소 비현실적인 결과를 가져오지만 참신한 아이디어입니다.

다음을 통해이 게시물 공유 : 출처: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/