Het instrumenteren van post-siliciumvalidatie is geen nieuw idee, maar hier is een wending. Met behulp van (pre-silicium) emulatie om debug-observatiestructuren te kiezen om in-silicium te instrumenteren. Paul Cunningham (GM, Verification bij Cadence), Raúl Camposano (Silicon Catalyst, ondernemer, voormalig CTO van Synopsys) en ik vervolgen onze serie over onderzoeksideeën. Zoals altijd: feedback welkom.

![]()

De innovatie

De keuze van deze maand is Emulatie-infrastructuur voor de evaluatie van hardwarebeweringen voor post-siliciumvalidatie. Het artikel werd gepresenteerd tijdens de IEEE Transactions on VLSI 2017. De auteurs zijn afkomstig van McMaster University, Hamilton, ON, Canada

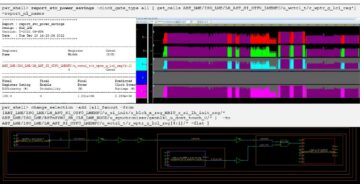

De auteurs maken onderscheid tussen logische en elektrische fouten post-silicium en besteden in dit artikel hun aandacht aan elektrische fouten, detecteerbaar via bit-flips in flops. Hun aanpak is het bepalen van een optimale reeks beweringen in pre-siliciumanalyse. Deze implementeren ze vervolgens in silicium ter ondersteuning van post-silicium-debug. De pre-siliciumanalyse is vergelijkbaar met fouten in veiligheidsanalyses, waarbij fouten op flops worden geïnjecteerd die overeenkomen met elektrische fouten, zoals aangegeven in het artikel. Ze genereren een kandidatenlijst met beweringen met behulp van beweringsynthese; De kern van hun innovatie is het bieden van een methode om deze beweringen te beoordelen op basis van hoe effectief ze zijn bij het opsporen van meerdere fouten.

Het genereren van invoer is willekeurig, waarbij de geïnjecteerde fouten (die als voorbijgaand worden behandeld) in volgorde worden geanalyseerd. Ze maken een door de gebruiker opgegeven aantal detectiecycli per fout mogelijk. In een volgende fase meten ze de effectiviteit met behulp van twee verschillende dekkingstechnieken. Voor flip-flopdekking tellen ze een bewering als er op een flop een geïnjecteerde fout optreedt. Bij bit-flip-dekking scoren ze het aantal fouten dat op afzonderlijke flops is gedetecteerd. Deze statistieken, samen met gebiedsschattingen, gebruiken ze (afwisselend) om te selecteren welke beweringen de voorkeur hebben.

De mening van Paul

Dit papier past mooi bij ons Blog van augustus 2020 over snelle foutdetectie (QED). QED versnelt de detectie van functionele bugs na silicium, waarbij deze blog zich richt op de detectie van elektrische bugs na silicium. Het artikel is gemakkelijk te lezen, hoewel het helpt om eerst de referentie te lezen [23].

Elektrische bugs zijn moeilijk op te sporen, en zelfs dan zijn ze moeilijk te repliceren en de onderliggende fysieke oorzaak te vinden. De auteurs stellen een methode voor, door middel van ingebedde logica, om te detecteren wanneer dergelijke bugs ervoor zorgen dat een flop naar een onjuiste waarde flipt (ze graven niet dieper dan het vinden van deze flips).

De kern van het artikel en de bijbehorende referentie [23] is een meerstapsmethode om deze detectielogica te creëren en te synthetiseren. Het begint met het ontginnen van eigenschappen van het ontwerp als tijdelijke beweringen met behulp van de GoldMine-tool. Ze rangschikken beweringen op basis van een schatting van hun vermogen om bitflips te detecteren, en een schatting van de oppervlakte-/bedradingskosten die in silicium moeten worden geïmplementeerd. De rangschikking is afhankelijk van het uitvoeren van veel pre-siliciumsimulaties met kandidaat-beweringen, het injecteren van bitflip-fouten en het tellen van gedetecteerde salto's per bewering. In het originele artikel gebruikten ze logische simulatie, hier versnellen ze deze simulaties door het ontwerp in kaart te brengen op een Altera FPGA-bord.

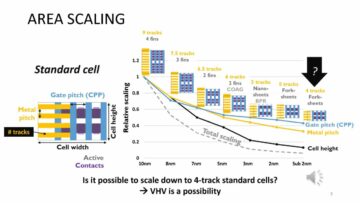

Ik vind het leuk hoe ze verschillende innovaties samenbrengen in een coherente methode voor post-silicium bit-flip-detectie: assertion mining, assertion synthese en een elegante rangschikkingsfunctie voor assertion-selectie. Het resultatengedeelte van het artikel geeft echter aan dat het detecteren van bitflips in n% van de flip-flops ruwweg een n% toename van het ontwerpgebied vereist. Dit lijkt een uitdaging voor commerciële toepassingen, vooral omdat het alleen maar helpt bij het opsporen van elektrische bugs. Je zou mogelijk een soortgelijk resultaat kunnen bereiken door de logische kegel die een flip-flop aanstuurt te klonen en vervolgens de uitvoer van deze gekloonde logica te vergelijken met de oorspronkelijke logica. Dit lijkt een vergelijkbare oppervlakte-overhead te genereren als hun methode, waarbij in de limiet het hele ontwerp wordt gekloond (dat wil zeggen 100% oppervlakte-overhead) om salto's te detecteren in 100% van de flops in het ontwerp.

De mening van Raúl

Het document staat op zichzelf en bevat behoorlijk wat details. De auteurs voerden experimenten uit voor 3 ISCAS-sequentiële circuits (poorten van ongeveer 12K, 2000 FF). Voorbereidingsexperimenten injecteren 256 fouten per flip-flop en gebruiken alle beweringen gegenereerd door GoldMine. Vanwege de beperkte capaciteit van de FPGA splitsen de auteurs de runs op tot 45 “sessies” voor één circuit. De resultaten tonen, zelfs met 45 sessies, een versnelling in de analyse ten opzichte van de simulatie van 20-500 keer (slechts tot 8 foutinjecties omdat de simulatie te langzaam wordt, 105 uur). De maximaal haalbare Flip-Flop dekking bedraagt 55%, 89% en 99% voor de 3 circuits. Het aantal gedolven beweringen bepaalt de dekking.

Het uitvoeren met geselecteerde beweringen (overeenkomend met een oppervlakte-overhead van 5-50%) en 1-256 injecties resulteert in een bitdekking van 2.2%-34%. Meestal draaide de beweringsmijnwerker 228 uur. Eén ding dat mij in verwarring bracht, zijn hun gegevens over runtimes versus geïnjecteerde fouten. De toename ziet er in simulatie redelijk (lineair) uit. Maar bij emulatie springt het enorm omhoog, van 0.045 uur naar 5.4 uur, wat een toename van 2 naar 8 foutinjecties oplevert. Ik zou graag meer uitleg willen op dit punt.

Dit is een methodologiepaper. Ik vind het leuk dat vrijwel elke stap kan worden vervangen door een commercieel hulpmiddel. Samen met het gebruik van een groot FPGA-bord (als emulator) wordt de methodologie geschaald. Methodologieën zijn uiteraard heel moeilijk te commercialiseren, maar het is een mooie toepassing voor bestaande technologie!

Mijn mening

De methode voor het onderzoeken van een veiligheidsanalysetechniek voor post-siliciumdebug is intrigerend. Een nieuw idee, ook al leidde het tot een enigszins onpraktisch resultaat voor commerciële toepassing.

Deel dit bericht via: Bron: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Alles

- analyse

- Aanvraag

- GEBIED

- auteurs

- Beetje

- Blog

- boord

- Bug

- bugs

- Cadans

- Inhoud

- het worstelen

- Veroorzaken

- commercieel

- voortzetten

- CTO

- gegevens

- Design

- detail

- Opsporing

- aandrijving

- effectief

- Ondernemer

- schattingen

- eerlijk

- Voornaam*

- FPGA

- functie

- Gates

- GM

- Hardware

- hier

- Hoe

- HTTPS

- idee

- IEEE

- Laat uw omzet

- Infrastructuur

- Innovatie

- IT

- Groot

- leidend

- Beperkt

- Lijst

- maatregel

- Metriek

- Mijnbouw

- Papier

- voorstellen

- onderzoek

- Resultaten

- lopend

- Veiligheid

- gekozen

- -Series

- reeks

- simulatie

- spleet

- ondersteuning

- niet de tijd of

- Transacties

- twist

- universiteit-

- waarde

- Verificatie

- Tegen