I løpet av uken 19. aprilth, Linley Group holdt sin vårprosessorkonferanse 2021. Linley Group har et rykte for å innkalle til utmerkede konferanser. Og årets vårkonferanse var intet unntak. Det var en rekke svært informative foredrag fra ulike selskaper som oppdaterte publikum om det siste forsknings- og utviklingsarbeidet som skjer i bransjen. Presentasjonene hadde blitt kategorisert under åtte ulike emner. Temaene var Edge AI, Embedded SoC Design, Scaling AI Training, AI SoC Design, Network Infrastructure for AI og 5G, Edge AI Software, Signal Processing and Efficient AI Inference.

Kunstig intelligens (AI) som teknologi har fått mye oppmerksomhet og investeringer de siste årene. Konferansen reflekterte absolutt det i antall emnekategorier knyttet til AI. Innenfor den bredere kategorien AI var Edge AI et emne som hadde en urettferdig andel av presentasjonene og med rette. Edge computing opplever rask vekst drevet av IoT, 5G og andre applikasjoner med lav latenskrav.

En av presentasjonene i Edge AI-kategorien hadde tittelen "Forbedre RISC-V Vector Extensions for å akselerere ytelsen på ML-arbeidsbelastninger." Foredraget ble holdt av Chris Lattner, President, Engineering and Product i SiFive, Inc. Chris gjorde en sterk sak for hvorfor SiFives RISC-V vektorutvidelsesbaserte løsning passer utmerket for AI-drevne applikasjoner. Følgende er min oppfatning.

Markedskrav:

Så raskt som markedet for edge computing vokser, blir ytelses- og strømkravene til disse applikasjonene også mer og mer krevende. Mange av disse applikasjonene er AI-drevet og faller inn under kategorien maskinlæring (ML) arbeidsbelastninger. Og AI-adopsjon presser behandlingskravene mer mot datamanipulering i stedet for generell databehandling. Dyp læring ligger til grunn for ML-modeller og involverer behandling av store arrays av data. Med ML-modeller i rask utvikling, vil en ideell løsning være en som optimerer for: ytelse, kraft, enkel inkorporering av nye ML-modeller og omfanget av resulterende maskinvare- og/eller programvareendringer.

RISC-V vektor fordel:

Den opprinnelige motivasjonen bak initiativet som har gitt oss RISC-V-arkitekturen er eksperimentering. Eksperimenterer for å utvikle brikkedesign som gir bedre ytelse i møte med forventet nedgang i Moores lov. RISC-V er bygget på ideen om å kunne skreddersy spesielle brikker der du kan velge hvilke instruksjonssett-utvidelser du bruker. Vektorutvidelser gjør det mulig å behandle vektorer av hvilken som helst lengde ved å bruke funksjoner som behandler vektorer med faste lengder. Vektorbehandling gjør at eksisterende programvare kan kjøres uten rekompilering når maskinvare oppgraderes i form av flere ALUer og andre funksjonelle enheter. Betydelig fremgang har skjedd når det gjelder etablert maskinvarebase og støttende økosystem som kompilatorteknologier.

RISC-V kan optimaliseres for et bestemt domene eller applikasjon gjennom tilpassede utvidelser. Som en åpen standard instruksjonssettarkitektur nyter RISC-V-brukere mye fleksibilitet når de velger en leverandør for deres chipdesignbehov.

SiFives tilbud:

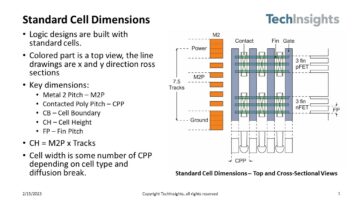

SiFive har forbedret RISC-V Vector-fordelen ved å legge til nye vektorutvidelser for å akselerere utførelse av mange forskjellige nevrale nettverksmodeller. Se figur 1 for å se et eksempel på typen speedup som kan oppnås ved å bruke SiFives tilleggsutvidelser sammenlignet med å bruke bare basisvektorutvidelsene til RISC-V. Intelligence X280-løsningen er en RISC-V Vector-løsning med flere kjerner (maskinvare og programvare) for å gjøre det enkelt for kundene å implementere optimaliserte Edge AI-applikasjoner. Løsningen kan også brukes til å implementere datasenterapplikasjoner.

Figur 1:

SiFive fordel:

- SiFives Intelligence X280-løsning støtter fullt ut TensorFlow og TensorFlow Lite åpen kildekode-plattformer for maskinlæring (se figur 2)

- SiFive gir en enkel måte å migrere kundens eksisterende kode basert på andre arkitekturer til RISC-V Vector-arkitektur. For eksempel kan SiFive oversette ARM Neon-kode til RISC-V V-monteringskode

- SiFive lar sine kunder utforske å legge til tilpassede utvidelser til deres RISC-V-implementeringer

- SiFive gjennom sin OpenFive forretningsenhet utvider tilpassede brikkeimplementeringstjenester for å møte domenespesifikke silisiumbehov

Figur 2:

Sammendrag:

I et nøtteskall kan SiFive-kunder enkelt og raskt implementere applikasjonene sine, enten applikasjonene involverer Edge AI-arbeidsbelastninger eller tradisjonelle datasentertyper. Hvis du er interessert i å dra nytte av SiFives løsninger for å akselerere ytelsen til ML-arbeidsbelastningene dine, anbefaler jeg at du registrerer deg og lytter til Hele foredraget til Chris og diskuter deretter med SiFive om måter å utnytte deres forskjellige tilbud for å utvikle produktene dine.

Del dette innlegget via: Kilde: https://semiwiki.com/ip/sifive/299157-enhancing-risc-v-vector-extensions-to-accelerate-performance-on-ml-workloads/

- 2021

- 5G

- Tillegg

- Adopsjon

- Fordel

- AI

- AI adopsjon

- AI-trening

- Søknad

- søknader

- April

- arkitektur

- ARM

- publikum

- virksomhet

- chip

- chips

- kode

- Selskaper

- databehandling

- Konferanse

- konferanser

- Kunder

- dato

- Datasenter

- dyp læring

- utforming

- utvikle

- Utvikling

- drevet

- økosystem

- Edge

- kanten beregning

- Ingeniørarbeid

- gjennomføring

- utvidelser

- Face

- FAST

- Figur

- passer

- fleksibilitet

- skjema

- fullt

- general

- flott

- Gruppe

- Økende

- Vekst

- maskinvare

- HTTPS

- Tanken

- Inc.

- industri

- Infrastruktur

- Initiative

- Intelligens

- investering

- IOT

- IT

- stor

- siste

- Law

- læring

- Leverage

- maskinlæring

- Manipulasjon

- marked

- Saker

- ML

- Neon

- nettverk

- neural

- nevrale nettverket

- tilby

- tilbud

- åpen

- Annen

- ytelse

- Plattformer

- makt

- Presentasjoner

- president

- Produkt

- Produkter

- Krav

- forskning

- forskning og utvikling

- Kjør

- skalering

- Tjenester

- sett

- Del

- So

- Software

- Solutions

- vår

- støtte

- Støtter

- Snakker

- Technologies

- Teknologi

- tensorflow

- Initiativet

- Kurs

- us

- Brukere

- uke

- innenfor

- Arbeid

- år

- Utbytte