Instrumentering av post-silisiumvalidering er ikke en ny idé, men her er en vri. Bruke (pre-silisium) emulering for å velge feilsøkingsobservasjonsstrukturer for å instrumentere i silisium. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, gründer, tidligere Synopsys CTO) og jeg fortsetter serien vår om forskningsideer. Som alltid, tilbakemeldinger velkommen.

![]()

Innovasjonen

Denne månedens valg er Emuleringsinfrastruktur for evaluering av maskinvarepåstander for post-silisiumvalidering. Oppgaven ble presentert på 2017 IEEE Transactions on VLSI. Forfatterne er fra McMaster University, Hamilton, ON, Canada

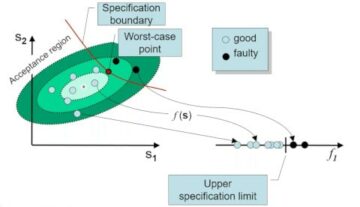

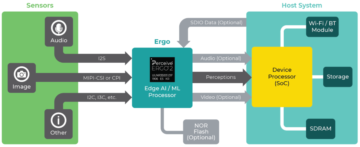

Forfatterne skiller mellom logiske og elektriske feil etter silisium og vier sin oppmerksomhet i denne artikkelen til elektriske feil, som kan oppdages gjennom bit-flips i flops. Deres tilnærming er å bestemme et optimalt sett med påstander i pre-silisiumanalyse. Disse implementerer de deretter i silisium til støtte for post-silisiumfeilsøking. Pre-silisiumanalysen ligner på feil i sikkerhetsanalyser, injisering av feil på flopper som tilsvarer elektriske feil, som de antyder i papiret. De genererer en kandidatliste over påstander ved å bruke påstandssyntese; kjernen i innovasjonen deres er å gi en metode for å gradere disse påstandene etter hvor effektiv hver enkelt er når det gjelder å oppdage flere feil.

Inndatagenerering er tilfeldig, og analyserer injiserte feil (behandlet som forbigående) i rekkefølge. De tillater et brukerspesifisert antall sykluser for deteksjon per feil. I en påfølgende fase måler de effektivitet ved å bruke to forskjellige dekningsteknikker. For flip-flop-dekning teller de en påstand hvis den fanger en injisert feil på en flopp. I bit-flip-dekning scorer de påstander antall feil oppdaget på separate flopper. Disse beregningene, sammen med arealestimater, bruker de (alternativt) for å velge hvilke foretrukne påstander.

Paulus syn

Dette papiret passer fint sammen med vår August 2020-blogg om rask feiloppdagelse (QED). QED akselererer post-silisium funksjonell feildeteksjon, hvor denne bloggen fokuserer på post-silisium elektrisk feildeteksjon. Oppgaven er lettlest, selv om det hjelper å lese referansen først [23].

Elektriske feil er vanskelig å fange, og selv da er det vanskelig å replikere og finne den underliggende fysiske årsaken. Forfatterne foreslår en metode, gjennom innebygd logikk, for å oppdage når slike feil får en flopp til å snu til en feil verdi (de graver ikke dypere enn å finne disse flippene).

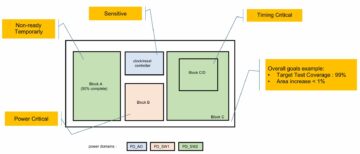

Hjertet i papiret og dens ledsagerreferanse [23] er en flertrinnsmetode for å lage og syntetisere denne deteksjonslogikken. Det begynner med gruveegenskapene til designet som tidsmessige påstander ved å bruke GoldMine verktøy. De rangerer påstander basert på et estimat av deres evne til å oppdage bitflip, og et estimat av arealet/ledningskostnadene for å implementere i silisium. Rangering er avhengig av å kjøre mange pre-silisiumsimuleringer med kandidatpåstander, injisere bitflip-feil og telle oppdagede flips etter påstander. I den originale artikkelen brukte de logikksimulering, her akselererer de disse simuleringene ved å kartlegge designet til et Altera FPGA-kort.

Jeg liker hvordan de trekker sammen flere innovasjoner til en sammenhengende metode for post-silicon bit flip-deteksjon: assertion mining, assertion syntese og en elegant rangeringsfunksjon for assertion valg. Resultatdelen av papiret indikerer imidlertid at det å oppdage bitflips i n % av flip-floppene krever omtrent en n % økning i designområdet. Dette virker utfordrende for kommersiell bruk, spesielt siden det bare hjelper å finne elektriske feil. Man kan potensielt oppnå et lignende resultat ved å klone logikkkjeglen som driver en flip-flop, og deretter sammenligne utdata fra denne klonede logikken med den opprinnelige logikken. Dette ser ut til å generere en lignende områdeoverhead som metoden deres, i grensen for kloning av hele designet (dvs. 100 % områdeoverhead) for å oppdage flips i 100 % av floppene i designet.

Raúl syn

Papiret er selvstendig med en god del detaljer. Forfatterne kjørte eksperimenter for 3 ISCAS sekvensielle kretser (ca. 12K porter, 2000 FF). Forberedelseseksperimenter injiserer 256 feil per flip flop og bruker alle påstander generert av GoldMine. På grunn av den begrensede kapasiteten til FPGA går forfatteroppdelingen til 45 "økter" for en krets. Resultatene viser, selv med 45 økter, en akselerasjon i analyse over simulering på 20-500 ganger (bare opptil 8 feilinjeksjoner fordi simuleringen blir for sakte, 105 timer). Maksimal oppnåelig flip-flop-dekning er 55 %, 89 % og 99 % for de 3 kretsene. Antall påstander som utvinnes kontrollerer dekningen.

Å kjøre med utvalgte påstander (tilsvarer en 5-50 % arealoverhead) og 1-256 injeksjoner resulterer i 2.2 %-34 % bitdekning. Mesteparten av tiden løp gruvearbeideren i 228 timer. En ting som forvirret meg er dataene deres for kjøretider versus injiserte feil. Økningen ser rimelig ut (lineær) i simulering. Men i emulering hopper den massivt, fra 0.045 t til 5.4 t for en økning på 2 til 8 feilinjeksjoner. Jeg ønsker mer forklaring på dette punktet.

Dette er en metodikkoppgave. Jeg liker at stort sett hvert trinn kan erstattes av et kommersielt verktøy. Sammen med bruk av et stort FPGA-kort (som emulator) skalerer metodikken. Metoder er selvfølgelig veldig vanskelige å kommersialisere, men det er en fin applikasjon for eksisterende teknologi!

Mitt syn

Metoden for å utforske en sikkerhetsanalyseteknikk for post-silisiumfeilsøking er spennende. En ny idé, selv om den fører til et noe upraktisk resultat for kommersiell bruk.

Del dette innlegget via: Kilde: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Alle

- analyse

- Søknad

- AREA

- forfattere

- Bit

- Blogg

- borde

- Bug

- bugs

- Cadence

- Kapasitet

- Catch

- Årsak

- kommersiell

- fortsette

- CTO

- dato

- utforming

- detalj

- Gjenkjenning

- kjøring

- Effektiv

- Gründer

- estimater

- rettferdig

- Først

- FPGA

- funksjon

- Gates

- GM

- maskinvare

- her.

- Hvordan

- HTTPS

- Tanken

- IEEE

- Øke

- Infrastruktur

- Innovasjon

- IT

- stor

- ledende

- Begrenset

- Liste

- måle

- Metrics

- Gruvedrift

- Papir

- foreslå

- forskning

- Resultater

- rennende

- Sikkerhet

- valgt

- Serien

- sett

- simulering

- splittet

- støtte

- tid

- Transaksjoner

- vri

- universitet

- verdi

- Verifisering

- Versus