Walidacja oprzyrządowania po krzemie nie jest nowym pomysłem, ale mamy tu pewną odmianę. Używanie emulacji (przed krzemem) do wyboru struktur obserwacji debugowania w celu oprzyrządowania w krzemie. Paul Cunningham (GM, Verification w Cadence), Raúl Camposano (Silicon Catalyst, przedsiębiorca, były dyrektor ds. technicznych Synopsys) i ja kontynuujemy naszą serię dotyczącą pomysłów badawczych. Jak zawsze, opinie mile widziane.

![]()

Innowacja

Wybór w tym miesiącu to Infrastruktura emulacyjna do oceny asercji sprzętowych na potrzeby walidacji po krzemie. Artykuł został zaprezentowany podczas konferencji IEEE Transactions on VLSI 2017. Autorzy pochodzą z Uniwersytetu McMaster w Hamilton, ON, Kanada

Autorzy rozróżniają błędy logiczne i elektryczne postsilikonowe i poświęcają w tym artykule swoją uwagę błędom elektrycznym, wykrywalnym poprzez przerzucanie bitów w flopach. Ich podejście polega na określeniu optymalnego zestawu twierdzeń w analizie przedkrzemowej. Następnie wdrażają je w krzemie w celu wsparcia debugowania po krzemie. Analiza przedsilikonowa przypomina błędy w analizach bezpieczeństwa, polegające na wstrzykiwaniu błędów na flopie odpowiadających błędom elektrycznym, jak sugeruje artykuł. Generują listę kandydatów twierdzeń za pomocą syntezy twierdzeń; Istotą ich innowacji jest zapewnienie metody oceny tych twierdzeń według skuteczności każdego z nich w wykrywaniu wielu błędów.

Generowanie danych wejściowych jest losowe i analizuje po kolei wprowadzone błędy (traktowane jako przejściowe). Umożliwiają one określoną przez użytkownika liczbę cykli wykrywania każdego błędu. W kolejnej fazie mierzą skuteczność, stosując dwie różne techniki pokrycia. W przypadku pokrycia przerzutnika liczą asercję, jeśli wyłapie ona wprowadzony błąd na dowolnym flopie. W przypadku przerzucania bitów oceniają liczbę asercji błędów wykrytych w oddzielnych flopach. Metryki te wraz z szacunkami obszaru służą (na przemian) do wyboru preferowanych twierdzeń.

Pogląd Pawła

Ten papier świetnie komponuje się z naszymi Blog z sierpnia 2020 r. na temat szybkiego wykrywania błędów (CO BYŁO DO OKAZANIA). QED przyspiesza wykrywanie błędów funkcjonalnych po krzemie, a ten blog skupia się na wykrywaniu błędów elektrycznych po krzemie. Artykuł jest łatwy w czytaniu, chociaż warto najpierw zapoznać się z literaturą [23].

Błędy elektryczne są trudne do wyłapania, a nawet wtedy trudno je odtworzyć i znaleźć ich fizyczną przyczynę. Autorzy proponują metodę, wykorzystującą wbudowaną logikę, do wykrywania, kiedy takie błędy powodują zmianę flopa na niepoprawną wartość (nie sięgają głębiej niż tylko znalezienie tych rzutów).

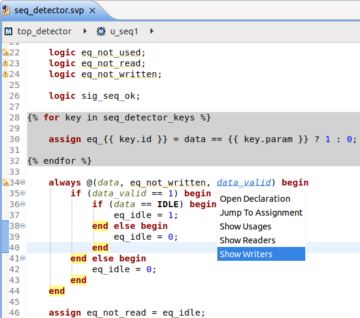

Sercem artykułu i towarzyszącej mu publikacji [23] jest wieloetapowa metoda tworzenia i syntezy logiki wykrywania. Zaczyna się od właściwości eksploracyjnych projektu jako twierdzeń czasowych przy użyciu Narzędzie GoldMine. Oceniają twierdzenia w oparciu o szacunkową zdolność do wykrywania przeskoków bitów oraz szacunkowy koszt powierzchni/okablowania do wdrożenia w krzemie. Ranking polega na przeprowadzaniu wielu symulacji przed krzemem z potencjalnymi asercjami, wstrzykiwaniu błędów odwracania bitów i liczeniu wykrytych odwracań na podstawie asercji. W oryginalnej pracy wykorzystano symulację logiczną, tutaj przyspieszono te symulacje, mapując projekt na płytkę Altera FPGA.

Podoba mi się, jak łączą kilka innowacji w spójną metodę wykrywania odwracania bitów po krzemie: eksploracja asercji, synteza asercji i elegancka funkcja rankingowa do selekcji asercji. Jednakże część artykułu dotycząca wyników wskazuje, że wykrywanie przełączeń bitów w n% przerzutników wymaga w przybliżeniu n% zwiększenia obszaru projektowego. Wydaje się to trudne w przypadku zastosowań komercyjnych, zwłaszcza że pomaga jedynie w znajdowaniu usterek elektrycznych. Potencjalnie można osiągnąć podobny wynik, klonując stożek logiczny sterujący przerzutnikiem, a następnie porównując dane wyjściowe tej sklonowanej logiki z logiką pierwotną. Wydaje się, że generuje to podobny narzut obszaru jak ich metoda, w limicie klonowania całego projektu (tj. 100% narzutu obszaru) w celu wykrycia przewrotów w 100% przepięć w projekcie.

Pogląd Raula

Papier jest samowystarczalny i zawiera sporo szczegółów. Autorzy przeprowadzili eksperymenty dla 3 kolejnych obwodów ISCAS (bramki ok. 12K, 2000 FF). Eksperymenty przygotowawcze wstrzykują 256 błędów na przerzutnik i wykorzystują wszystkie twierdzenia wygenerowane przez GoldMine. Ze względu na ograniczoną pojemność FPGA autorzy podzielili przebiegi na 45 „sesji” dla jednego obwodu. Wyniki pokazują, że nawet przy 45 sesjach przyspieszenie analizy w porównaniu z symulacją wynosi 20–500 razy (tylko do 8 wstrzyknięć błędów, ponieważ symulacja jest zbyt wolna, 105 godzin). Maksymalne osiągalne pokrycie typu flip-flop wynosi 55%, 89% i 99% dla 3 obwodów. Liczba wydobytych stwierdzeń kontroluje pokrycie.

Praca z wybranymi asercjami (odpowiadającymi 5–50% narzutu obszaru) i 1–256 wstrzyknięć skutkuje pokryciem bitów na poziomie 2.2%–34%. W większości przypadków górnik asercyjny działał przez 228 godzin. Jedną rzeczą, która mnie zdezorientowała, są dane dotyczące czasu wykonania w porównaniu z wprowadzonymi błędami. Wzrost wygląda rozsądnie (liniowo) w symulacji. Ale w emulacji skacze masowo, z 0.045 h do 5.4 h, co oznacza wzrost o 2 do 8 zastrzyków błędów. Chciałbym więcej wyjaśnień w tej kwestii.

Jest to dokument metodologiczny. Podoba mi się to, że prawie każdy krok można zastąpić narzędziem komercyjnym. Wraz z wykorzystaniem dużej płytki FPGA (jako emulatora) metodologia skaluje się. Metodologie są oczywiście bardzo trudne do skomercjalizowania, ale jest to niezłe zastosowanie dla istniejącej technologii!

Mój widok

Intrygująca jest metoda badania techniki analizy bezpieczeństwa na potrzeby debugowania po krzemie. Nowatorski pomysł, choć prowadzący do nieco niepraktycznego wyniku w zastosowaniu komercyjnym.

Udostępnij ten post przez: Źródło: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Wszystkie kategorie

- analiza

- Zastosowanie

- POWIERZCHNIA

- Autorzy

- Bit

- Blog

- deska

- Bug

- błędy

- Kadencja

- Pojemność

- zapasy

- Spowodować

- handlowy

- kontynuować

- CTO

- dane

- Wnętrze

- detal

- Wykrywanie

- jazdy

- Efektywne

- Przedsiębiorca

- Szacunki

- sprawiedliwy

- i terminów, a

- FPGA

- funkcjonować

- Bramy

- GM

- sprzęt komputerowy

- tutaj

- W jaki sposób

- HTTPS

- pomysł

- IEEE

- Zwiększać

- Infrastruktura

- Innowacja

- IT

- duży

- prowadzący

- Ograniczony

- Lista

- zmierzyć

- Metryka

- Górnictwo

- Papier

- zaproponować

- Badania naukowe

- Efekt

- bieganie

- Bezpieczeństwo

- wybrany

- Serie

- zestaw

- symulacja

- dzielić

- wsparcie

- czas

- transakcje

- twist

- uniwersytet

- wartość

- Weryfikacja

- Przeciw