Achronix é conhecida por suas soluções FPGA de alto desempenho. Neste post, explorarei o FPGA Speedster7T. Esta família de FPGA é otimizada para cargas de trabalho de alta largura de banda e elimina gargalos de desempenho com uma arquitetura inovadora. Construída no processo FinFET de 7nm da TSMC, a família oferece desempenho de nível ASIC, mantendo a programabilidade total de um FPGA. Há muito o que aprender sobre o Speedster7T. A Achronix agora tem disponível um vídeo que responderá a muitas dessas perguntas. Há um link para esse vídeo e muito mais, mas primeiro vamos ver o que acontece quando você leva o FPGA Achronix Speedster7t para um test drive no laboratório.

Achronix é conhecida por suas soluções FPGA de alto desempenho. Neste post, explorarei o FPGA Speedster7T. Esta família de FPGA é otimizada para cargas de trabalho de alta largura de banda e elimina gargalos de desempenho com uma arquitetura inovadora. Construída no processo FinFET de 7nm da TSMC, a família oferece desempenho de nível ASIC, mantendo a programabilidade total de um FPGA. Há muito o que aprender sobre o Speedster7T. A Achronix agora tem disponível um vídeo que responderá a muitas dessas perguntas. Há um link para esse vídeo e muito mais, mas primeiro vamos ver o que acontece quando você leva o FPGA Achronix Speedster7t para um test drive no laboratório.

Steve Mensor, vice-presidente de vendas e marketing da Achronix apresenta o vídeo. Steve está na Achronix há quase dez anos e antes disso passou 21 anos na Altera. Ele certamente sabe muito sobre FPGAs – design e aplicação. Steve começa descrevendo alguns dos elementos da arquitetura inovadora mencionada anteriormente. Há muitos recursos dedicados a bordo do Speedster7T. Isso inclui:

- SerDes de 112 Gbps

- 400G Ethernet

- PCIe Gen5

- GDDR6 rodando a 4 Tbps

- DDR 4 rodando a 3,200 Mbps

- Um processador proprietário de aprendizado de máquina

- Rede 2D no chip (NoC)

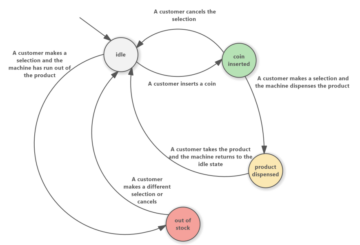

O processador proprietário de aprendizado de máquina oferece muitas funcionalidades, incluindo ponto flutuante, ponto flutuante de bloco e operações inteiras. O 2D NoC é um recurso novo na indústria para FPGAs da Achronix. O NoC pode rotear dados de qualquer uma das interfaces de alta velocidade para a estrutura principal do FPGA a 2 GHz sem consumir nenhum dos recursos lógicos do FPGA. Toda essa tecnologia integrada permite obter desempenho de nível ASIC em um FPGA.

Steve então passa a apresentação para Katie Purcell, gerente de engenharia de aplicação da Achronix. Katie está na Achronix há quatro anos. Antes disso, ela era designer ASIC. Ela também passou um tempo na Xilinx. Katie é quem leva o FPGA Speedster7t para um test drive no laboratório e ela está definitivamente à altura do desafio.

Katie leva o espectador ao laboratório Achronix, onde está sendo realizada a apresentação do Speedster7T – validação e caracterização. A demonstração que Katie apresenta mostra o dispositivo executando tráfego Ethernet 400G no Placa aceleradora Achronix VectorPath. Katie começa resumindo os elementos-chave da demonstração, que incluem:

- Interface externa 8X50G

- Interface única 400G no subsistema Ethernet

- Dados divididos em quatro fluxos separados no NoC 2D

- Cada fluxo processado de forma independente

Katie passa algum tempo no NoC 2D. Ela ressalta que essa capacidade torna o projeto mais simples e facilita o fechamento do tempo. Este NoC 2D exclusivo apareceu várias vezes durante a demonstração. Vale a pena aprofundar um pouco mais para entender. A Achronix apresentou anteriormente um webinar sobre esta capacidade única que foi coberto no SemiWiki chamado 5 razões pelas quais um SmartNIC reconfigurável de alto desempenho exige um NoC 2D. A boa notícia é que uma repetição deste webinar muito informativo já está disponível. Você pode assistir aqui.

Katie mostra detalhadamente o que está acontecendo dentro do dispositivo Speedster7T enquanto ele processa os pacotes de dados. Conhecer esses detalhes ajuda a compreender a facilidade de configuração e a precisão fornecida mostrada durante a demonstração. Se você acha que um dispositivo exclusivo como esse pode ajudar em seu projeto de design, recomendo fortemente que você assista à demonstração. É curto, mas muito útil. Você pode acesse o vídeo de demonstração aqui.

Agora você sabe como levar o FPGA Achronix Speedster7t para um test drive no laboratório. Você pode descobrir mais detalhes sobre isso família FPGA única aqui.

Compartilhe esta postagem via: Fonte: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- acelerador

- Todos os Produtos

- Aplicação

- arquitetura

- ASIC

- Pouco

- borda

- desafiar

- lasca

- vinda

- dados,

- Design

- Designer

- Engenharia

- tecidos

- família

- Primeiro nome

- FPGA

- cheio

- Bom estado, com sinais de uso

- Alta

- Como funciona o dobrador de carta de canal

- Como Negociar

- HTTPS

- Incluindo

- inovadores

- IT

- Chave

- APRENDER

- aprendizagem

- LINK

- aprendizado de máquina

- Marketing

- rede

- notícias

- Operações

- atuação

- projeto

- razões

- Recursos

- Rota

- corrida

- vendas

- Baixo

- Soluções

- Equipar

- teste

- tempo

- tráfego

- Vídeo

- Assistir

- webinar

- QUEM

- Equivalente há

- X

- anos