Under veckan den 19 aprilth, Linley Group höll sin Spring Processor Conference 2021. Linley Group har ett rykte om att sammankalla utmärkta konferenser. Och årets vårkonferens var inget undantag. Det var ett antal mycket informativa föredrag från olika företag som uppdaterade publiken om det senaste forsknings- och utvecklingsarbetet som pågår i branschen. Presentationerna hade kategoriserats under åtta olika ämnesområden. Ämnena var Edge AI, Embedded SoC Design, Scaling AI Training, AI SoC Design, Network Infrastructure for AI och 5G, Edge AI Software, Signal Processing och Efficient AI Inference.

Artificiell intelligens (AI) som teknik har fått mycket uppmärksamhet och investeringar under de senaste åren. Konferensen återspeglade verkligen det i antalet ämneskategorier relaterade till AI. Inom den bredare kategorin AI var Edge AI ett ämne som hade en orättvis andel presentationer och med rätta. Edge computing ser snabb tillväxt driven av IoT, 5G och andra applikationer med låg latenskrav.

En av presentationerna inom kategorin Edge AI hade titeln "Förbättra RISC-V Vector Extensions för att accelerera prestanda på ML-arbetsbelastningar." Talet hölls av Chris Lattner, VD, Engineering and Product på SiFive, Inc. Chris gjorde ett starkt argument för varför SiFives RISC-V vektortilläggsbaserade lösning passar utmärkt för AI-drivna applikationer. Följande är min uppfattning.

Marknadskrav:

Så snabbt som marknaden för edge computing växer, blir prestanda- och effektkraven för dessa applikationer också mer och mer krävande. Många av dessa applikationer är AI-drivna och faller inom kategorin maskininlärning (ML) arbetsbelastningar. Och AI-användning driver bearbetningskraven mer mot datamanipulation snarare än generell datoranvändning. Deep learning ligger till grund för ML-modeller och involverar bearbetning av stora mängder data. Med ML-modeller som utvecklas snabbt, skulle en idealisk lösning vara en som optimerar för: prestanda, kraft, lätthet att införliva nya ML-modeller och omfattningen av resulterande hårdvaru- och/eller mjukvaruförändringar.

RISC-V Vector Advantage:

Den ursprungliga motivationen bakom initiativet som har gett oss RISC-V-arkitekturen är experimenterande. Experimenterar för att utveckla chipdesigner som ger bättre prestanda inför förväntad avmattning av Moores lag. RISC-V bygger på idén att kunna skräddarsy speciella marker där du kan välja vilka instruktionsförlängningar du använder. Vektorförlängningar möjliggör bearbetning av vektorer av valfri längd med hjälp av funktioner som behandlar vektorer med fasta längder. Vektorbearbetning gör att befintlig programvara kan köras utan omkompilering när hårdvaran uppgraderas i form av fler ALU och andra funktionella enheter. Betydande framsteg har skett när det gäller etablerad hårdvarubas och stödjande ekosystem som kompilatorteknik.

RISC-V kan optimeras för en viss domän eller applikation genom anpassade tillägg. Som en öppen standardinstruktionsuppsättningsarkitektur har RISC-V-användare stor flexibilitet när de väljer en leverantör för deras chipdesignbehov.

SiFives erbjudande:

SiFive har förbättrat fördelen med RISC-V Vector genom att lägga till nya vektortillägg för att påskynda exekvering av många olika neurala nätverksmodeller. Se figur 1 för att se ett exempel på den typ av snabbhet som kan uppnås med SiFives tilläggstillägg jämfört med att bara använda basvektorförlängningarna av RISC-V. Dess Intelligence X280-lösning är en flerkärnig RISC-V Vector-lösning (hårdvara och mjukvara) för att göra det enkelt för sina kunder att implementera optimerade Edge AI-applikationer. Lösningen kan även användas för att implementera datacenterapplikationer.

Figur 1:

SiFive fördel:

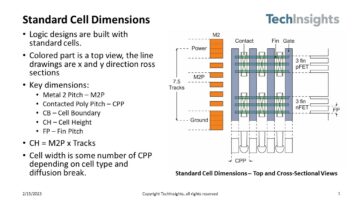

- SiFives Intelligence X280-lösning stöder fullt ut TensorFlow och TensorFlow Lite open source-plattformar för maskininlärning (se figur 2)

- SiFive ger ett enkelt sätt att migrera kundens befintliga kod baserat på andra arkitekturer till RISC-V Vector-arkitektur. Till exempel kan SiFive översätta ARM Neon-kod till RISC-V V-monteringskod

- SiFive låter sina kunder utforska att lägga till anpassade tillägg till sina RISC-V-implementeringar

- SiFive utökar genom sin OpenFive affärsenhet anpassade chipimplementeringstjänster för att tillgodose domänspecifika kiselbehov

Figur 2:

Sammanfattning:

I ett nötskal kan SiFive-kunder enkelt och snabbt implementera sina applikationer, oavsett om applikationerna involverar Edge AI-arbetsbelastningar eller traditionella datacentertyper. Om du är intresserad av att dra nytta av SiFives lösningar för att accelerera prestanda för dina ML-arbetsbelastningar rekommenderar jag att du registrerar dig och lyssnar på Chris hela tal och diskutera sedan med SiFive om sätt att utnyttja deras olika erbjudanden för att utveckla dina produkter.

Dela det här inlägget via: Källa: https://semiwiki.com/ip/sifive/299157-enhancing-risc-v-vector-extensions-to-accelerate-performance-on-ml-workloads/

- 2021

- 5G

- Tillägg

- Antagande

- Fördel

- AI

- AI-antagande

- AI-utbildning

- Ansökan

- tillämpningar

- April

- arkitektur

- ARM

- publik

- företag

- chip

- Pommes frites

- koda

- Företag

- databehandling

- Konferens

- konferenser

- Kunder

- datum

- Data Center

- djupt lärande

- Designa

- utveckla

- Utveckling

- driven

- ekosystemet

- kant

- kanten beräkning

- Teknik

- utförande

- förlängningar

- Ansikte

- SNABB

- Figur

- passa

- Flexibilitet

- formen

- full

- Allmänt

- stor

- Grupp

- Odling

- Tillväxt

- hårdvara

- HTTPS

- Tanken

- Inc.

- industrin

- Infrastruktur

- Initiativ

- Intelligens

- investering

- iot

- IT

- Large

- senaste

- Lag

- inlärning

- Hävstång

- maskininlärning

- Manipulation

- marknad

- Betyder Något

- ML

- neon

- nät

- neural

- neurala nätverk

- erbjuda

- offer~~POS=TRUNC

- öppet

- Övriga

- prestanda

- Plattformar

- kraft

- Presentationer

- VD

- Produkt

- Produkter

- Krav

- forskning

- forskning och utveckling

- Körning

- skalning

- Tjänster

- in

- Dela

- So

- Mjukvara

- Lösningar

- vår

- stödja

- Stöder

- Talks

- Tekniken

- Teknologi

- tensorflow

- Initiativet

- Utbildning

- us

- användare

- vecka

- inom

- Arbete

- år

- Avkastning