Instrumentering av post-kiselvalidering är ingen ny idé men här är en twist. Använda (pre-silikon) emulering för att välja felsökningsobservationsstrukturer för att instrumentera in-silikon. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entreprenör, tidigare Synopsys CTO) och jag fortsätter vår serie om forskningsidéer. Som alltid välkomnas feedback.

![]()

Innovation

Den här månadens val är Emuleringsinfrastruktur för utvärdering av hårdvarupåståenden för post-kiselvalidering. Uppsatsen presenterades vid 2017 IEEE Transactions on VLSI. Författarna är från McMaster University, Hamilton, ON, Kanada

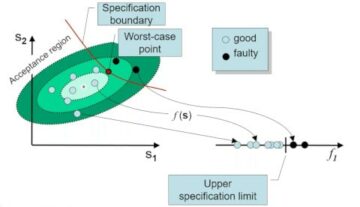

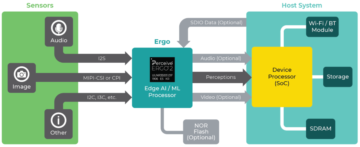

Författarna skiljer mellan logiska och elektriska fel efter kisel och ägnar sin uppmärksamhet i denna artikel åt elektriska fel, som kan upptäckas genom bit-flips i floppar. Deras tillvägagångssätt är att bestämma en optimal uppsättning av påståenden i pre-silikonanalys. Dessa implementerar de sedan i kisel till stöd för felsökning efter kisel. Pre-silikonanalysen liknar fel i säkerhetsanalyser, injicering av fel på floppar som motsvarar elektriska fel, som de antyder i tidningen. De genererar en kandidatlista med påståenden genom att använda påståendesyntes; kärnan i deras innovation är att tillhandahålla en metod för att gradera dessa påståenden efter hur effektiva var och en är för att upptäcka flera fel.

Ingångsgenereringen är slumpmässig och analyserar injicerade fel (behandlas som övergående) i sekvens. De tillåter ett användarspecificerat antal cykler för upptäckt per fel. I en efterföljande fas mäter de effektiviteten med hjälp av två olika täckningstekniker. För flip-flop-täckning räknar de ett påstående om det fångar ett injicerat fel på någon flopp. I bit-flip-täckning poängsätter de påståenden antal fel som upptäckts på separata floppar. Dessa mätvärden, tillsammans med areauppskattningar, använder de (växelvis) för att välja vilka föredragna påståenden.

Pauls syn

Detta papper passar bra ihop med vår Augusti 2020 blogg om snabb felsökning (QED). QED accelererar detektering av funktionella buggar efter kisel, där den här bloggen fokuserar på upptäckt av elektriska buggar efter kisel. Uppsatsen är lätt att läsa, även om det hjälper att först läsa referens [23].

Elektriska buggar är svåra att fånga, och även då är de svåra att replikera och hitta den underliggande fysiska orsaken. Författarna föreslår en metod, genom inbäddad logik, för att upptäcka när sådana buggar får en flopp att vända till ett felaktigt värde (de gräver inte djupare än att hitta dessa flipar).

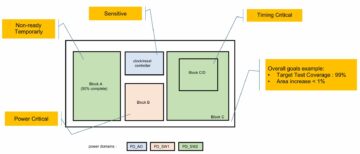

Hjärtat i tidningen och dess medföljande referens [23] är en flerstegsmetod för att skapa och syntetisera denna detekteringslogik. Det börjar med gruvegenskaper hos designen som tidsmässiga påståenden med hjälp av GoldMine verktyg. De rangordnar påståenden baserat på en uppskattning av deras förmåga att upptäcka bitflip och en uppskattning av arean/ledningskostnaden att implementera i kisel. Rankning förlitar sig på att köra många pre-silikon-simuleringar med kandidatpåståenden, injicera bitflip-fel och räkna upptäckta vändningar för påståenden. I originalet använde de logisk simulering, här accelererar de dessa simuleringar genom att kartlägga designen till ett Altera FPGA-kort.

Jag gillar hur de drar ihop flera innovationer till en sammanhängande metod för post-kiselbitflip-detektion: assertion mining, assertion-syntes och en elegant rankningsfunktion för assertion-selektion. Emellertid indikerar resultatsektionen av uppsatsen att detektering av bitvippor i n% av vipporna kräver ungefär en n% ökning av designarean. Detta verkar utmanande för kommersiell tillämpning, särskilt eftersom det bara hjälper till att hitta elektriska buggar. Man skulle potentiellt kunna uppnå ett liknande resultat genom att klona logikkonen som driver en flip-flop och sedan jämföra utdata från denna klonade logik med den ursprungliga logiken. Detta verkar generera en liknande area overhead som deras metod, i gränsen för kloning av hela designen (dvs. 100% area overhead) för att upptäcka flips i 100% av flopparna i designen.

Raúls syn

Tidningen är fristående med en hel del detaljer. Författarna körde experiment för 3 ISCAS sekventiella kretsar (ca 12K grindar, 2000 FF). Förberedelseexperiment injicerar 256 fel per flip flop och använder alla påståenden som genereras av GoldMine. På grund av den begränsade kapaciteten hos FPGA:n löper uppdelningen av författare till 45 "sessioner" för en krets. Resultaten visar, även med 45 sessioner, en acceleration i analys över simulering på 20-500 gånger (endast upp till 8 felinjektioner eftersom simuleringen blir för långsam, 105h). Den maximala möjliga flip-flop-täckningen är 55 %, 89 % och 99 % för de 3 kretsarna. Antalet påståenden som utvinns styr täckningen.

Att köra med utvalda påståenden (motsvarande en 5-50% area overhead) och 1-256 injektioner resulterar i 2.2%-34% bittäckning. För det mesta sprang gruvarbetaren i 228 timmar. En sak som förvirrade mig är deras data för körtider kontra injicerade fel. Ökningen ser rimlig (linjär) ut i simulering. Men i emulering hoppar den massivt, från 0.045h till 5.4h för en ökning med 2 till 8 felinjektioner. Jag skulle vilja ha mer förklaring på denna punkt.

Detta är ett metoduppsats. Jag gillar att i stort sett varje steg kan ersättas av ett kommersiellt verktyg. Tillsammans med att använda ett stort FPGA-kort (som emulator) skalar metodiken. Metoder är naturligtvis väldigt svåra att kommersialisera, men det är en trevlig applikation för befintlig teknik!

Min åsikt

Metoden att utforska en säkerhetsanalysteknik för post-kiselfelsökning är spännande. En ny idé, även om den leder till ett något opraktiskt resultat för kommersiell tillämpning.

Dela det här inlägget via: Källa: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Alla

- analys

- Ansökan

- OMRÅDE

- Författarna

- Bit

- Blogg

- ombord

- Bug

- fel

- Kadens

- Kapacitet

- brottning

- Orsak

- kommersiella

- fortsätta

- CTO

- datum

- Designa

- detalj

- Detektering

- drivande

- Effektiv

- Entrepreneur

- uppskattningar

- verkligt

- Förnamn

- FPGA

- fungera

- grindar

- GM

- hårdvara

- här.

- Hur ser din drömresa ut

- HTTPS

- Tanken

- IEEE

- Öka

- Infrastruktur

- Innovation

- IT

- Large

- ledande

- Begränsad

- Lista

- mäta

- Metrics

- Gruvdrift

- Papper

- föreslå

- forskning

- Resultat

- rinnande

- Säkerhet

- vald

- Serier

- in

- simulering

- delas

- stödja

- tid

- Transaktioner

- vridning

- universitet

- värde

- Verifiering

- Kontra