Achronix är känt för sina högpresterande FPGA-lösningar. I det här inlägget kommer jag att utforska Speedster7T FPGA. Denna FPGA-familj är optimerad för arbetsbelastningar med hög bandbredd och eliminerar prestandaflaskhalsar med en innovativ arkitektur. Byggd på TSMC:s 7nm FinFET-process, levererar familjen prestanda på ASIC-nivå samtidigt som den behåller den fullständiga programmerbarheten hos en FPGA. Det finns mycket att lära om Speedster7T. Achronix har nu en video tillgänglig som kommer att svara på många av dessa frågor. Det finns en länk till den videon och mer kommer, men låt oss först se vad som händer när du tar Achronix Speedster7t FPGA för en provkörning i labbet.

Achronix är känt för sina högpresterande FPGA-lösningar. I det här inlägget kommer jag att utforska Speedster7T FPGA. Denna FPGA-familj är optimerad för arbetsbelastningar med hög bandbredd och eliminerar prestandaflaskhalsar med en innovativ arkitektur. Byggd på TSMC:s 7nm FinFET-process, levererar familjen prestanda på ASIC-nivå samtidigt som den behåller den fullständiga programmerbarheten hos en FPGA. Det finns mycket att lära om Speedster7T. Achronix har nu en video tillgänglig som kommer att svara på många av dessa frågor. Det finns en länk till den videon och mer kommer, men låt oss först se vad som händer när du tar Achronix Speedster7t FPGA för en provkörning i labbet.

Steve Mensor, VP för försäljning och marknadsföring på Achronix presenterar videon. Steve har varit med Achronix i nästan tio år och tillbringade 21 år på Altera innan dess. Han vet verkligen mycket om FPGA:er – design och tillämpning. Steve börjar med att beskriva några av elementen i den tidigare nämnda innovativa arkitekturen. Det finns mycket dedikerad kapacitet ombord på Speedster7T. Detta inkluderar:

- 112 Gbps SerDes

- 400G Ethernet

- PCIe Gen5

- GDDR6 körs med 4 Tbps

- DDR 4 körs på 3,200 XNUMX Mbps

- En egen maskininlärningsprocessor

- 2D-nätverk på chip (NoC)

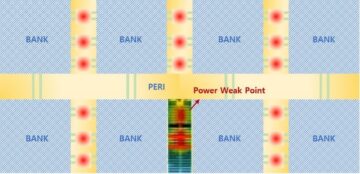

Den egenutvecklade maskininlärningsprocessorn levererar en mängd funktioner, inklusive flyttal, block flyttal och heltalsoperationer. 2D NoC är en nytillverkad funktion för FPGA:er från Achronix. NoC kan dirigera data från vilket som helst av höghastighetsgränssnitten till FPGA-kärnan vid 2 GHz utan att förbruka någon av FPGA-logikresurserna. All denna inbyggda teknik gör att du kan nå prestanda på ASIC-nivå i en FPGA.

Steve lämnar sedan över presentationen till Katie Purcell, applikationsingenjörschef på Achronix. Katie har varit med Achronix i fyra år. Dessförinnan var hon ASIC-designer. Hon tillbringade också tid på Xilinx. Katie är den som tar Speedster7t FPGA för en provkörning i labbet, och hon klarar definitivt utmaningen.

Katie tar med tittaren till Achronix-labbet där uppfödning av Speedster7T utförs – validering och karaktärisering. Demon Katie presenterar visar enheten som kör 400G Ethernet-trafik på Achronix VectorPath acceleratorkort. Katie börjar med att sammanfatta de viktigaste delarna av demonstrationen, som inkluderar:

- 8 X 50G externt gränssnitt

- Enkelt 400G-gränssnitt i Ethernet-delsystem

- Data uppdelad i fyra separata strömmar i 2D NoC

- Varje ström bearbetas oberoende

Katie tillbringar lite tid på 2D NoC. Hon påpekar att denna förmåga gör designen enklare och lättare att stänga timing. Denna unika 2D NoC kom upp flera gånger under demot. Det är värt att gräva i lite mer för att förstå det. Achronix presenterade tidigare ett webinar om denna unika förmåga som var täcks av SemiWiki kallas 5 skäl till varför en omkonfigurerbar SmartNIC med hög prestanda kräver en 2D NoC. Den goda nyheten är att en repris av detta mycket informativa webbseminarium nu är tillgängligt. Du kan se den här.

Katie tar dig igenom en detaljerad titt på vad som händer inuti Speedster7T-enheten när den bearbetar datapaketen. Att känna till dessa detaljer hjälper till att förstå den enkla installationen och den levererade noggrannheten som visas under demon. Om du tror att en unik enhet som denna kan hjälpa ditt designprojekt rekommenderar jag starkt att du tittar på demon. Den är kort, men väldigt användbar. Du kan se demovideon här.

Nu vet du hur du tar Achronix Speedster7t FPGA för en provkörning i labbet. Du kan få mer information om detta unik FPGA-familj här.

Dela det här inlägget via: Källa: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- accelerator

- Alla

- Ansökan

- arkitektur

- ASIC

- Bit

- ombord

- utmanar

- chip

- kommande

- datum

- Designa

- designer

- Teknik

- tyg

- familj

- Förnamn

- FPGA

- full

- god

- Hög

- Hur ser din drömresa ut

- How To

- HTTPS

- Inklusive

- innovativa

- IT

- Nyckel

- LÄRA SIG

- inlärning

- LINK

- maskininlärning

- Marknadsföring

- nät

- nyheter

- Verksamhet

- prestanda

- projektet

- skäl

- Resurser

- Rutt

- rinnande

- försäljning

- Kort

- Lösningar

- Teknologi

- testa

- tid

- trafik

- Video

- Kolla på

- webbseminarium

- VEM

- värt

- X

- år