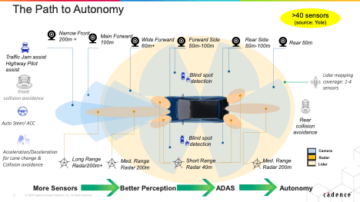

การตรวจสอบความถูกต้องของโพสต์ซิลิคอนไม่ใช่แนวคิดใหม่ แต่นี่คือจุดหักมุม การใช้การจำลอง (พรีซิลิคอน) เพื่อเลือกโครงสร้างการสังเกตการแก้ไขจุดบกพร่องสำหรับอุปกรณ์ในซิลิคอน Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, ผู้ประกอบการ, อดีต Synopsys CTO) และฉันดำเนินซีรีส์เกี่ยวกับแนวคิดการวิจัยต่อไป เช่นเคยยินดีรับข้อเสนอแนะ

![]()

นวัตกรรม

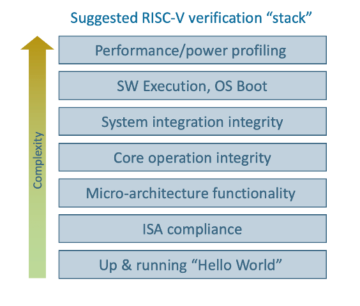

เลือกเดือนนี้ โครงสร้างพื้นฐานการจำลองสำหรับการประเมินการยืนยันฮาร์ดแวร์สำหรับการตรวจสอบความถูกต้องหลังซิลิคอน. บทความนี้ถูกนำเสนอในธุรกรรม IEEE ปี 2017 บน VLSI ผู้เขียนมาจาก McMaster University, Hamilton, ON, Canada

ผู้เขียนแยกแยะระหว่างข้อผิดพลาดทางตรรกะและข้อผิดพลาดทางไฟฟ้าหลังซิลิคอน และให้ความสนใจในบทความนี้ไปที่ข้อผิดพลาดทางไฟฟ้า ซึ่งตรวจพบได้ผ่านการพลิกบิตในความล้มเหลว แนวทางของพวกเขาคือการกำหนดชุดการยืนยันที่เหมาะสมที่สุดในการวิเคราะห์พรีซิลิกอน จากนั้นพวกเขาจะนำไปใช้ในซิลิคอนเพื่อรองรับการแก้ไขข้อบกพร่องหลังซิลิคอน การวิเคราะห์พรีซิลิกอนนั้นคล้ายคลึงกับการเกิดข้อบกพร่องในการวิเคราะห์ด้านความปลอดภัย โดยการฉีดข้อผิดพลาดไปที่ฟล็อปปี้ดิสก์ที่สอดคล้องกับข้อผิดพลาดทางไฟฟ้า ตามที่กล่าวไว้ในรายงาน พวกเขาสร้างรายการการยืนยันที่ผู้สมัครใช้การสังเคราะห์การยืนยัน หัวใจหลักของนวัตกรรมคือการจัดเตรียมวิธีการให้คะแนนการยืนยันเหล่านี้โดยพิจารณาจากประสิทธิภาพของแต่ละข้อในการตรวจจับข้อผิดพลาดหลายรายการ

การสร้างอินพุตเป็นแบบสุ่ม โดยวิเคราะห์ข้อบกพร่องที่ฉีดเข้าไป (ถือเป็นภาวะชั่วคราว) ตามลำดับ โดยอนุญาตให้ผู้ใช้ระบุจำนวนรอบในการตรวจจับต่อข้อผิดพลาด ในระยะต่อมา จะวัดประสิทธิภาพโดยใช้เทคนิคการครอบคลุมที่แตกต่างกันสองแบบ สำหรับการครอบคลุมฟลิปฟล็อป พวกเขาจะนับการยืนยันหากพบข้อผิดพลาดที่แทรกอยู่ในฟล็อปใดๆ ในการครอบคลุมบิตฟลิป จะให้คะแนนการยืนยันจำนวนข้อผิดพลาดที่ตรวจพบในฟล็อปแยกกัน เมตริกเหล่านี้ร่วมกับการประมาณพื้นที่ใช้ (สลับกัน) เพื่อเลือกการยืนยันที่ต้องการ

มุมมองของพอล

กระดาษนี้เข้ากันได้ดีกับเรา บล็อกเดือนสิงหาคม 2020 เกี่ยวกับการตรวจหาข้อผิดพลาดอย่างรวดเร็ว (คิวอีดี). QED เร่งการตรวจจับจุดบกพร่องในการทำงานของโพสต์ซิลิคอน โดยที่บล็อกนี้มุ่งเน้นไปที่การตรวจจับจุดบกพร่องทางไฟฟ้าหลังซิลิคอน บทความนี้อ่านง่าย แม้ว่าจะช่วยในการอ่านข้อมูลอ้างอิงก่อน [23] ก็ตาม

แมลงไฟฟ้านั้นจับได้ยาก และถึงอย่างนั้นก็ยากที่จะทำซ้ำและค้นหาสาเหตุทางกายภาพที่ซ่อนอยู่ ผู้เขียนเสนอวิธีการโดยใช้ตรรกะแบบฝังตัว เพื่อตรวจจับเมื่อจุดบกพร่องดังกล่าวทำให้ฟล็อปพลิกไปเป็นค่าที่ไม่ถูกต้อง (พวกเขาไม่ได้เจาะลึกไปกว่าการค้นหาการพลิกเหล่านี้)

หัวใจของบทความนี้และการอ้างอิงร่วม [23] เป็นวิธีการหลายขั้นตอนในการสร้างและสังเคราะห์ตรรกะการตรวจจับนี้ มันเริ่มต้นด้วยคุณสมบัติการขุดของการออกแบบเป็นการยืนยันชั่วคราวโดยใช้ เครื่องมือ GoldMine. พวกเขาจัดอันดับการยืนยันโดยพิจารณาจากการประเมินความสามารถในการตรวจจับการพลิกของบิต และการประมาณพื้นที่/ต้นทุนการเดินสายไฟในซิลิคอน การจัดอันดับขึ้นอยู่กับการรันการจำลองพรีซิลิกอนจำนวนมากพร้อมการยืนยันตัวเลือก การแทรกข้อผิดพลาดการพลิกบิต และการนับการพลิกที่ตรวจพบตามการยืนยัน ในรายงานต้นฉบับ พวกเขาใช้การจำลองเชิงตรรกะ ในที่นี้ พวกเขาเร่งการจำลองเหล่านี้โดยการแมปการออกแบบกับบอร์ด Altera FPGA

ฉันชอบวิธีที่พวกเขารวบรวมนวัตกรรมหลายอย่างเข้าด้วยกันเป็นวิธีการที่สอดคล้องกันสำหรับการตรวจจับการพลิกของบิตหลังซิลิคอน: การขุดการยืนยัน การสังเคราะห์การยืนยัน และฟังก์ชันการจัดอันดับที่หรูหราสำหรับการเลือกการยืนยัน อย่างไรก็ตาม ส่วนผลลัพธ์ของรายงานระบุว่าการตรวจจับบิตพลิกใน n% ของฟลิปฟล็อปนั้นต้องการพื้นที่การออกแบบเพิ่มขึ้นประมาณ n% สิ่งนี้ดูท้าทายสำหรับการใช้งานเชิงพาณิชย์ โดยเฉพาะอย่างยิ่งเนื่องจากจะช่วยค้นหาจุดบกพร่องทางไฟฟ้าเท่านั้น เราอาจบรรลุผลลัพธ์ที่คล้ายกันได้โดยการโคลนลอจิกกรวยที่ขับเคลื่อนฟลิปฟล็อป จากนั้นเปรียบเทียบเอาต์พุตของลอจิกที่ถูกโคลนนี้กับลอจิกดั้งเดิม สิ่งนี้ดูเหมือนจะสร้างค่าใช้จ่ายในพื้นที่ที่คล้ายกันตามวิธีการของพวกเขา ในขีดจำกัดการโคลนการออกแบบทั้งหมด (เช่น ค่าใช้จ่ายในพื้นที่ 100%) เพื่อตรวจจับการพลิกใน 100% ของความล้มเหลวในการออกแบบ

มุมมองของราอูล

กระดาษมีเนื้อหาครบถ้วนและมีรายละเอียดพอสมควร ผู้เขียนทำการทดลองสำหรับวงจรลำดับ ISCAS 3 วงจร (เกทประมาณ 12K, 2000 FF) การทดลองเตรียมการฉีดข้อผิดพลาด 256 รายการต่อฟลิปฟล็อป และใช้การยืนยันทั้งหมดที่สร้างโดย GoldMine เนื่องจากความจุที่จำกัดของ FPGA ผู้แต่งจึงแบ่งรันเป็น 45 “เซสชัน” สำหรับหนึ่งวงจร ผลลัพธ์แสดงให้เห็นว่า แม้จะมีเซสชัน 45 ก็ตาม ความเร่งในการวิเคราะห์เหนือการจำลอง 20-500 ครั้ง (การฉีดข้อผิดพลาดสูงสุด 8 ครั้งเท่านั้น เนื่องจากการจำลองช้าเกินไป 105 ชม.) ความครอบคลุม Flip-Flop ที่ทำได้สูงสุดคือ 55%, 89% และ 99% สำหรับ 3 วงจร จำนวนการยืนยันที่ขุดได้ครอบคลุมการควบคุมความครอบคลุม

การรันด้วยการยืนยันที่เลือก (สอดคล้องกับโอเวอร์เฮดของพื้นที่ 5-50%) และการฉีด 1-256 ส่งผลให้ได้ความครอบคลุมบิต 2.2%-34% ส่วนใหญ่แล้ว นักขุดยืนยันจะวิ่งเป็นเวลา 228 ชั่วโมง สิ่งหนึ่งที่ทำให้ฉันสับสนคือข้อมูลรันไทม์เทียบกับข้อผิดพลาดที่แทรกเข้ามา การเพิ่มขึ้นดูสมเหตุสมผล (เชิงเส้น) ในการจำลอง แต่ในการจำลอง มันจะกระโดดอย่างหนาแน่น จาก 0.045 ชม. เป็น 5.4 ชม. เพื่อเพิ่มข้อผิดพลาด 2 ถึง 8 ครั้ง ฉันต้องการคำอธิบายเพิ่มเติมเกี่ยวกับประเด็นนี้

นี่เป็นรายงานเกี่ยวกับระเบียบวิธี ฉันชอบที่ทุกขั้นตอนสามารถทดแทนได้ด้วยเครื่องมือเชิงพาณิชย์ เมื่อใช้ร่วมกับบอร์ด FPGA ขนาดใหญ่ (เป็นตัวจำลอง) วิธีการจะปรับขนาด แน่นอนว่าวิธีการต่างๆ นั้นยากที่จะทำเป็นเชิงพาณิชย์ แต่เป็นการประยุกต์ใช้ที่ดีสำหรับเทคโนโลยีที่มีอยู่!

มุมมองของฉัน

วิธีการสำรวจเทคนิคการวิเคราะห์ความปลอดภัยสำหรับการแก้ไขข้อบกพร่องหลังซิลิคอนเป็นเรื่องที่น่าสนใจ แนวคิดใหม่ แม้ว่าจะนำไปสู่ผลลัพธ์ที่ค่อนข้างทำไม่ได้สำหรับการนำไปใช้ในเชิงพาณิชย์

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- ทั้งหมด

- การวิเคราะห์

- การใช้งาน

- AREA

- ผู้เขียน

- บิต

- บล็อก

- คณะกรรมการ

- Bug

- เป็นโรคจิต

- จังหวะ

- ความจุ

- จับ

- ก่อให้เกิด

- เชิงพาณิชย์

- ต่อ

- CTO

- ข้อมูล

- ออกแบบ

- รายละเอียด

- การตรวจพบ

- การขับขี่

- มีประสิทธิภาพ

- ผู้ประกอบการ

- ประมาณการ

- ธรรม

- ชื่อจริง

- FPGA

- ฟังก์ชัน

- เกตส์

- GM

- ฮาร์ดแวร์

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- ความคิด

- อีอีอี

- เพิ่ม

- โครงสร้างพื้นฐาน

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- IT

- ใหญ่

- ชั้นนำ

- ถูก จำกัด

- รายการ

- วัด

- ตัวชี้วัด

- การทำเหมืองแร่

- กระดาษ

- เสนอ

- การวิจัย

- ผลสอบ

- วิ่ง

- ความปลอดภัย

- เลือก

- ชุด

- ชุด

- จำลอง

- แยก

- สนับสนุน

- เวลา

- การทำธุรกรรม

- บิด

- มหาวิทยาลัย

- ความคุ้มค่า

- การตรวจสอบ

- กับ