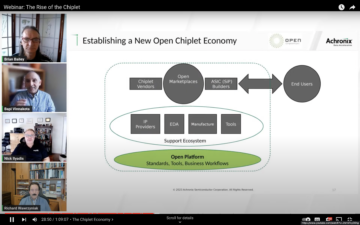

Achronix มีชื่อเสียงในด้านโซลูชัน FPGA ประสิทธิภาพสูง ในโพสต์นี้ ฉันจะสำรวจ Speedster7T FPGA ตระกูล FPGA นี้ได้รับการปรับให้เหมาะสมสำหรับปริมาณงานที่มีแบนด์วิธสูงและขจัดปัญหาคอขวดด้านประสิทธิภาพด้วยสถาปัตยกรรมที่เป็นนวัตกรรมใหม่ สร้างขึ้นบนกระบวนการ 7nm FinFET ของ TSMC ตระกูลนี้มอบประสิทธิภาพระดับ ASIC ในขณะที่ยังคงความสามารถในการตั้งโปรแกรมเต็มรูปแบบของ FPGA มีอะไรอีกมากมายให้เรียนรู้เกี่ยวกับ Speedster7T ตอนนี้ Achronix มีวิดีโอที่จะตอบคำถามเหล่านี้มากมาย มีลิงก์ไปยังวิดีโอดังกล่าวและอื่นๆ อีกมากมาย แต่ก่อนอื่นเรามาดูกันว่าจะเกิดอะไรขึ้นเมื่อคุณนำ Achronix Speedster7t FPGA ไปทดลองขับในห้องปฏิบัติการ

Achronix มีชื่อเสียงในด้านโซลูชัน FPGA ประสิทธิภาพสูง ในโพสต์นี้ ฉันจะสำรวจ Speedster7T FPGA ตระกูล FPGA นี้ได้รับการปรับให้เหมาะสมสำหรับปริมาณงานที่มีแบนด์วิธสูงและขจัดปัญหาคอขวดด้านประสิทธิภาพด้วยสถาปัตยกรรมที่เป็นนวัตกรรมใหม่ สร้างขึ้นบนกระบวนการ 7nm FinFET ของ TSMC ตระกูลนี้มอบประสิทธิภาพระดับ ASIC ในขณะที่ยังคงความสามารถในการตั้งโปรแกรมเต็มรูปแบบของ FPGA มีอะไรอีกมากมายให้เรียนรู้เกี่ยวกับ Speedster7T ตอนนี้ Achronix มีวิดีโอที่จะตอบคำถามเหล่านี้มากมาย มีลิงก์ไปยังวิดีโอดังกล่าวและอื่นๆ อีกมากมาย แต่ก่อนอื่นเรามาดูกันว่าจะเกิดอะไรขึ้นเมื่อคุณนำ Achronix Speedster7t FPGA ไปทดลองขับในห้องปฏิบัติการ

Steve Mensor รองประธานฝ่ายขายและการตลาดของ Achronix แนะนำวิดีโอ Steve ร่วมงานกับ Achronix มาเกือบสิบปีแล้ว และทำงานที่ Altera เป็นเวลา 21 ปีก่อนหน้านั้น แน่นอนเขารู้มากเกี่ยวกับ FPGA ทั้งการออกแบบและการใช้งาน Steve เริ่มต้นด้วยการสรุปองค์ประกอบบางอย่างของสถาปัตยกรรมนวัตกรรมที่กล่าวถึงก่อนหน้านี้ มีความสามารถเฉพาะมากมายบน Speedster7T ซึ่งรวมถึง:

- เซิร์ฟเวอร์ความเร็ว 112 Gbps

- 400G Ethernet

- PCIe Gen5

- GDDR6 ทำงานที่ 4 Tbps

- DDR 4 ทำงานที่ 3,200 Mbps

- โปรเซสเซอร์การเรียนรู้ของเครื่องที่เป็นเอกสิทธิ์

- เครือข่าย 2D บนชิป (NoC)

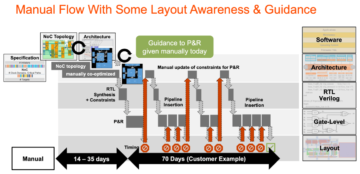

โปรเซสเซอร์แมชชีนเลิร์นนิงที่เป็นกรรมสิทธิ์มอบฟังก์ชันการทำงานมากมาย รวมถึงจุดลอยตัว บล็อกจุดลอยตัว และการดำเนินการจำนวนเต็ม 2D NoC คือความสามารถใหม่ในอุตสาหกรรมสำหรับ FPGA จาก Achronix NoC สามารถกำหนดเส้นทางข้อมูลจากอินเทอร์เฟซความเร็วสูงใดๆ ไปยังคอร์ FPGA Fabric ที่ความถี่ 2 GHz โดยไม่ต้องใช้ทรัพยากรลอจิก FPGA ใดๆ เทคโนโลยีออนบอร์ดทั้งหมดนี้ช่วยให้คุณได้รับประสิทธิภาพระดับ ASIC ใน FPGA

จากนั้น Steve ก็มอบการนำเสนอให้กับ Katie Purcell ผู้จัดการฝ่ายวิศวกรรมแอปพลิเคชันของ Achronix Katie อยู่กับ Achronix มาสี่ปีแล้ว ก่อนหน้านั้นเธอเป็นนักออกแบบ ASIC เธอยังใช้เวลาอยู่ที่ Xilinx อีกด้วย Katie เป็นคนที่นำ Speedster7t FPGA ไปทดลองขับในห้องแล็บ และเธอก็พร้อมรับมือกับความท้าทายอย่างแน่นอน

Katie พาผู้ชมเข้าไปในห้องแล็บ Achronix ซึ่งเป็นที่ที่นำ Speedster7T ขึ้นมาใหม่ - การตรวจสอบความถูกต้องและการกำหนดลักษณะเฉพาะ การสาธิตที่ Katie นำเสนอจะแสดงอุปกรณ์ที่ใช้การรับส่งข้อมูลอีเธอร์เน็ต 400G บน การ์ดเร่งความเร็ว Achronix VectorPath. เคธี่เริ่มต้นด้วยการสรุปองค์ประกอบสำคัญของการสาธิต ซึ่งรวมถึง:

- อินเทอร์เฟซภายนอก 8 X 50G

- อินเทอร์เฟซ 400G เดี่ยวในระบบย่อยอีเธอร์เน็ต

- ข้อมูลแบ่งออกเป็นสี่สตรีมแยกกันใน 2D NoC

- แต่ละสตรีมประมวลผลอย่างอิสระ

Katie ใช้เวลาพอสมควรกับ 2D NoC เธอชี้ให้เห็นว่าความสามารถนี้ทำให้การออกแบบง่ายขึ้นและง่ายต่อการปิดจังหวะ NoC 2D อันเป็นเอกลักษณ์นี้เกิดขึ้นหลายครั้งระหว่างการสาธิต มันคุ้มค่าที่จะขุดลึกลงไปอีกสักหน่อยเพื่อทำความเข้าใจ ก่อนหน้านี้ Achronix ได้นำเสนอการสัมมนาผ่านเว็บเกี่ยวกับความสามารถพิเศษนี้ ครอบคลุมอยู่ใน SemiWiki ที่เรียกว่า 5 เหตุผลว่าทำไม SmartNIC ที่กำหนดค่าใหม่ได้ประสิทธิภาพสูงจึงต้องการ 2D NoC. ข่าวดีก็คือ ขณะนี้สามารถรับชมการสัมมนาผ่านเว็บที่ให้ความรู้นี้ซ้ำได้แล้ว สามารถรับชมได้ที่นี่.

Katie จะพาคุณดูรายละเอียดเกี่ยวกับสิ่งที่เกิดขึ้นภายในอุปกรณ์ Speedster7T ขณะที่ประมวลผลแพ็กเก็ตข้อมูล การทราบรายละเอียดเหล่านั้นช่วยให้เข้าใจความง่ายในการตั้งค่าและส่งมอบความแม่นยำที่แสดงในระหว่างการสาธิต หากคุณคิดว่าอุปกรณ์พิเศษเช่นนี้สามารถช่วยโครงการออกแบบของคุณได้ ฉันขอแนะนำให้คุณชมการสาธิตเป็นอย่างยิ่ง มันสั้นแต่มีประโยชน์มาก คุณสามารถ เข้าถึงวิดีโอสาธิตได้ที่นี่.

ตอนนี้คุณรู้วิธีนำ Achronix Speedster7t FPGA ไปทดลองขับในห้องปฏิบัติการแล้ว คุณสามารถหารายละเอียดเพิ่มเติมเกี่ยวกับเรื่องนี้ได้ ตระกูล FPGA ที่ไม่เหมือนใครที่นี่.

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/efpga/achronix/303686-take-the-achronix-speedster7t-fpga-for-a-test-drive-in-the-lab/

- คันเร่ง

- ทั้งหมด

- การใช้งาน

- สถาปัตยกรรม

- ASIC

- บิต

- คณะกรรมการ

- ท้าทาย

- ชิป

- มา

- ข้อมูล

- ออกแบบ

- นักออกแบบ

- ชั้นเยี่ยม

- ผ้า

- ครอบครัว

- ชื่อจริง

- FPGA

- เต็ม

- ดี

- จุดสูง

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- ทำอย่างไร

- HTTPS

- รวมทั้ง

- นวัตกรรม

- IT

- คีย์

- เรียนรู้

- การเรียนรู้

- LINK

- เรียนรู้เครื่อง

- การตลาด

- เครือข่าย

- ข่าว

- การดำเนินการ

- การปฏิบัติ

- โครงการ

- เหตุผล

- แหล่งข้อมูล

- เส้นทาง

- วิ่ง

- ขาย

- สั้น

- โซลูชัน

- เทคโนโลยี

- ทดสอบ

- เวลา

- การจราจร

- วีดีโอ

- นาฬิกา

- webinar

- WHO

- คุ้มค่า

- X

- ปี