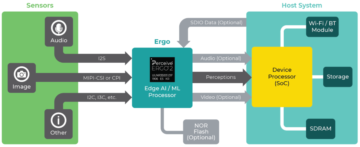

Post-silikon doğrulamayı enstrümanlamak yeni bir fikir değil ama işte bir değişiklik. Silikon içinde enstrümantasyon yapmak için gözlem yapılarında hata ayıklamayı seçmek için (silikon öncesi) emülasyonu kullanma. Paul Cunningham (GM, Cadence'de Doğrulama), Raúl Camposano (Silicon Catalyst, girişimci, eski Synopsys CTO'su) ve ben araştırma fikirleri serimize devam ediyoruz. Her zaman olduğu gibi, geri bildirim hoş geldiniz.

![]()

Yenilik

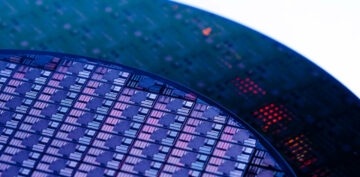

Bu ayın seçimi Silikon Sonrası Doğrulama için Donanım Onaylarının Değerlendirilmesine Yönelik Öykünme Altyapısı. Bildiri, 2017 IEEE Transactions on VLSI'da sunuldu. Yazarlar McMaster Üniversitesi, Hamilton, ON, Kanada'dandır.

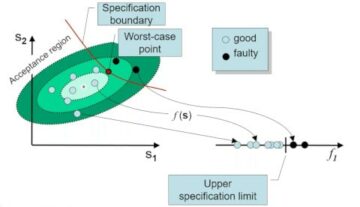

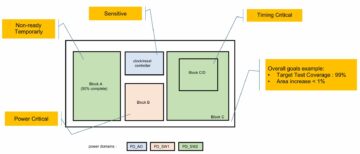

Yazarlar, silikon sonrası mantıksal ve elektriksel hataları birbirinden ayırıyor ve bu yazıda dikkatlerini, floplardaki bit-flips yoluyla saptanabilen elektrik hatalarına adadılar. Yaklaşımları, silikon öncesi analizde optimal bir iddia seti belirlemektir. Bunları daha sonra silikon sonrası hata ayıklamayı desteklemek için silikonda uygularlar. Silikon öncesi analiz, güvenlik analizlerindeki hataya benzer, kağıtta ima ettikleri gibi, hataları elektrik hatalarına karşılık gelen floplara enjekte eder. İddia sentezini kullanarak iddiaların bir aday listesini oluştururlar; Yeniliklerinin özü, bu iddiaları her birinin birden çok hatayı tespit etmede ne kadar etkili olduğuna göre derecelendirmek için bir yöntem sağlamaktır.

Girdi üretimi rasgele olup, enjekte edilen arızaları (geçici olarak ele alınır) sırayla analiz eder. Arıza başına algılama için kullanıcı tarafından belirlenen sayıda döngüye izin verirler. Sonraki bir aşamada, iki farklı kapsama tekniği kullanarak etkinliği ölçerler. Flip-flop kapsamı için, herhangi bir flopta enjekte edilen bir hatayı yakalarsa bir iddia sayarlar. Bit çevirme kapsamında, ayrı floplarda tespit edilen hataların iddia sayısını puanlarlar. Bu ölçümler, alan tahminleriyle birlikte, tercih edilen iddiaları seçmek için (dönüşümlü olarak) kullanırlar.

Paul'ün görüşü

Bu kağıt, bizim Hızlı hata algılamayla ilgili Ağustos 2020 blogu (KED). QED, silikon sonrası işlevsel hata tespitini hızlandırır; burada bu blog, silikon sonrası elektriksel hata tespitine odaklanır. İlk önce [23] referansını okumaya yardımcı olsa da makale kolay okunur.

Elektrik hatalarını yakalamak zordur ve o zaman bile kopyalayıp altta yatan fiziksel nedeni bulmak zordur. Yazarlar, gömülü mantık yoluyla, bu tür hataların bir flopun yanlış bir değere dönmesine neden olduğunu tespit etmek için bir yöntem önermektedir (bu çevirmeleri bulmaktan daha derine inmezler).

Makalenin kalbi ve ona eşlik eden referans [23], bu algılama mantığını oluşturmak ve sentezlemek için çok adımlı bir yöntemdir. kullanarak zamansal iddialar olarak tasarımın özelliklerini araştırmakla başlar. Altın Madeni aracı. İddiaları, bit çevirmelerini tespit etme yeteneklerine ilişkin bir tahmine ve silikonda uygulanacak alan / kablolama maliyetine ilişkin bir tahmine dayalı olarak sıralarlar. Sıralama, aday iddialarla birçok silikon öncesi simülasyonu çalıştırmaya, bit çevirme hatalarını enjekte etmeye ve tespit edilen çevirmeleri iddialara göre saymaya dayanır. Orijinal makalede mantık simülasyonunu kullandılar, burada tasarımı bir Altera FPGA kartına eşleyerek bu simülasyonları hızlandırıyorlar.

Silikon sonrası bit çevirme tespiti için birkaç yeniliği tutarlı bir yöntemde bir araya getirmelerini seviyorum: iddia madenciliği, iddia sentezi ve iddia seçimi için zarif bir sıralama işlevi. Bununla birlikte, makalenin sonuçlar bölümü, parmak arası terliklerin %n'sinde bit çevirmelerinin tespit edilmesinin tasarım alanında kabaca %n'lik bir artış gerektirdiğini göstermektedir. Bu, özellikle yalnızca elektrik arızalarının bulunmasına yardımcı olduğu için ticari uygulama için zorlayıcı görünüyor. Bir flip-flop kullanan mantık konisini klonlayarak potansiyel olarak benzer bir sonuç elde edilebilir, ardından bu klonlanmış mantığın çıktısı orijinal mantıkla karşılaştırılabilir. Bu, tasarımdaki başarısızlıkların %100'ündeki taklaları tespit etmek için tüm tasarımı klonlayan sınırda (yani, ek yükün %100'ü) kendi yöntemlerine benzer bir alan ek yükü oluşturuyor gibi görünmektedir.

Raúl'un görüşü

Kağıt, makul miktarda ayrıntıyla kendi kendine yetiyor. Yazarlar, 3 ISCAS ardışık devresi (yaklaşık 12K geçit, 2000 FF) için deneyler yaptı. Hazırlık deneyleri, flip flop başına 256 hata enjekte eder ve GoldMine tarafından üretilen tüm iddiaları kullanır. FPGA'nın sınırlı kapasitesi nedeniyle, yazarlar bir devre için 45 "oturum" a bölünmüştür. Sonuçlar, 45 seansta bile, analizde simülasyon üzerinde 20-500 kat hızlanma olduğunu gösteriyor (simülasyon çok yavaşladığı için yalnızca 8 hata enjeksiyonuna kadar, 105 saat). Ulaşılabilen maksimum Flip-Flop kapsamı, 55 devre için %89, %99 ve %3'dur. Çıkarılan iddiaların sayısı kapsamı kontrol eder.

Seçilen iddialarla çalıştırma (%5-50 alan ek yüküne karşılık gelir) ve 1-256 enjeksiyon, %2.2 - %34 bit kapsamıyla sonuçlanır. Çoğu zaman, iddia madencisi 228 saat çalıştı. Kafamı karıştıran bir şey, enjekte edilen hatalara karşı çalışma sürelerine ilişkin verileri. Artış, simülasyonda makul (doğrusal) görünüyor. Ancak öykünmede, 0.045'den 5.4'e hata enjeksiyonu artışı için 2 saatten 8 saate büyük ölçüde sıçrar. Bu noktada daha fazla açıklama istiyorum.

Bu bir metodoloji yazısıdır. Hemen hemen her adımın ticari bir araçla değiştirilebilmesini seviyorum. Metodoloji, büyük bir FPGA kartı (emülatör olarak) kullanmakla birlikte ölçeklenir. Metodolojileri ticarileştirmek elbette çok zor ama mevcut teknoloji için güzel bir uygulama!

Benim görüşüm

Silikon sonrası hata ayıklama için bir güvenlik analizi tekniğini keşfetme yöntemi ilgi çekicidir. Ticari uygulama için biraz pratik olmayan bir sonuca yol açsa da yeni bir fikir.

Bu gönderiyi şu yolla paylaş: Kaynak: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Türkiye

- analiz

- Uygulama

- ALAN

- Yazarlar

- Bit

- Blog

- yazı tahtası

- Böcek

- böcek

- Ritim

- Kapasite

- Yakalamak

- Sebeb olmak

- ticari

- devam etmek

- CTO

- veri

- Dizayn

- ayrıntı

- Bulma

- sürme

- Etkili

- Girişimci

- tahminleri

- adil

- Ad

- fpga

- işlev

- Gates,

- GM

- donanım

- okuyun

- Ne kadar

- HTTPS

- Fikir

- IEEE

- Artırmak

- Altyapı

- Yenilikçilik

- IT

- büyük

- önemli

- Sınırlı

- Liste

- ölçmek

- Metrikleri

- Madencilik

- kâğıt

- önermek

- araştırma

- Sonuçlar

- koşu

- Güvenlik

- seçilmiş

- Dizi

- set

- simülasyon

- bölmek

- destek

- zaman

- işlemler

- bükülme

- üniversite

- değer

- Doğrulama

- Karşı