Arka taraftaki güç bağlantılarını içeren ilk CMOS devreleri büyük olasılıkla yığılmış nano tabaka transistörlere dayalı olacak, ancak planlamacılar yolun daha da ilerisinde öngörüyorlar tamamlayıcı transistörler (CFET'ler) yığılmış NFET ve PFET cihazlarını dikey olarak entegre eder.

En az iki katı kalınlıkta nano tabaka transistörCFET'leri birbirine ve devrenin geri kalanına bağlamak, ister arka tarafı, ister ön tarafı veya her ikisini birden kullansın, herhangi bir ara bağlantı şemasına meydan okuma muhtemeldir.

Arka taraf gücü (bkz. ilgili bu madde) çekicidir çünkü arka taraftaki güç hatları hem daha kalın hem de daha kısa olabilir, bu da direnci ve IR düşüşünü azaltır. Güç hatlarının arka tarafa taşınması aynı zamanda ilk birkaç metal katmandaki sinyal yönlendirmeyi de basitleştirerek potansiyel olarak tasarımcıların bu katmanlardaki metal perdesini gevşetmelerine olanak tanır. Intel'in teknoloji geliştirmeden sorumlu başkan yardımcısı Ben Sell, eğer daha rahat bir saha kullanmak EUV'ye maruz kalmayı ortadan kaldırırsa veya EUV çoklu desenleme tekniklerine olan ihtiyacı azaltırsa, bu tasarrufların tek başına arka taraf güç uygulamasının maliyetini haklı çıkaracağını açıkladı.

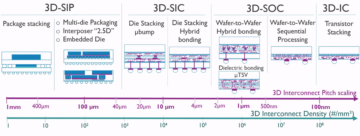

Arka taraftaki güç, transistörün boyutlarını etkilemez ve hücreyi küçültmeyebilir. Arka bağlantı için hala yer olması gerekiyor. Bununla birlikte, 2022 IEEE Elektron Cihaz Toplantısındaki kısa bir kursta Imec'ten Gaspard Hiblot, arka taraftaki güç raylarının kanal uzunluğunu aynı tutarken standart bir hücrede altı ila beş yol arasında ölçeklendirmeyi destekleyebileceğini savundu.[1]

Ancak CFET'ler standart hücreyi yapar daha küçük. PFET ve NFET cihazlarını tek bir dikey yığına taşımak, kanal uzunluğunu aynı tutarken potansiyel olarak transistör ayak izinin neredeyse yarısını kurtarır.

Intel üyesi Mauro Kobrinsky, arka taraftaki gücün CFET'ler için alan açısından en verimli bağlantı çözümü olduğunu söyledi. Yalnızca ön taraftan yönlendirme, alt cihaza ulaşmak için yüksek en boy oranına sahip bir gravür gerektirir ve ciddi yönlendirme tıkanıklığına neden olur. Aralık ayındaki IEDM konferansında sunulan sonuçlarda Intel, "PowerVia" bağlantılarını bir nano tabaka transistörün yanından gömülü bir güç şebekesine kadar çalıştıran bir arka taraf güç uygulamasını gösterdi. Yolları M-0'a kadar çalıştıran ve daha sonra alt tabaka boyunca aşağıya doğru uzanan gömülü güç rayı yaklaşımına kıyasla, PowerVia yaklaşımı hücre yüksekliğini beş yola indirir.

![Şekil 1: CFET'ler için üç ara bağlantı topolojisi seçeneği, tüm ön taraf bağlantılarını (a), üst cihaz için ön taraf bağlantılarını ve alt cihaz için arka taraf bağlantılarını (b) ve ön ve arka ara bağlantı yığınlarının yanı sıra yığılmış cihazlar arasındaki bağlantılara da PowerVia'yı kullanır. Kaynak: Intel/IEDM [2]](https://platoaistream.net/wp-content/uploads/2024/03/powering-cfets-from-the-backside.png)

Şekil 1: CFET'ler için üç ara bağlantı topolojisi seçeneği, tüm ön taraf bağlantılarını (a), üst cihaz için ön taraf bağlantılarını ve alt cihaz için arka taraf bağlantılarını (b) ve ön ve arka ara bağlantı yığınlarının yanı sıra yığılmış cihazlar arasındaki bağlantılara da PowerVia'yı kullanır. Kaynak: Intel/IEDM [2]

Gofret distorsiyonu alt temasları zorluyor

Kobrinsky'ye göre, CFET'lerin ortaya çıkışı, doğrudan alt cihaza bir alt temas ile daha fazla gelişme gerektirecektir. Bu şema, üstteki cihaz ile gömülü güç şebekesi arasında PowerVia'ya benzer bir yapının kullanılmasını öngörüyor. CFET'ler transistörleri istifleyerek çok fazla alan kazandığından, nispeten büyük yollara yer vardır. Bu önemsiz olmasa da, gömülü güç raylarına sahip nano tabaka transistörlerden alt kontaklara sahip CFET'lere doğru ilerleme devrim niteliğinde olmaktan çok artımlıdır.

Arka taraf gücüyle ilgili en büyük süreç zorlukları, cihazın altına ulaşmak için yüksek en-boy oranlı aşındırma ve doldurma, cihazlara alttan erişime izin veren aşırı silikon incelmesi ve arka taraf litografisi için yapıştırmayla ilgili bozulmadır. Özellikle arka taraftaki temaslar, temas edilen cihazlara muhtemelen 10nm veya daha iyi bir aralıkta çok zorlu bir hizalama gerektirecektir, bu nedenle bağlanmayla ilgili bozulma ciddi bir endişe kaynağıdır.

EV Grubu iş geliştirme direktörü Thomas Uhrmann, ön tarafta tam metalizasyon ve pasifleştirme ile cihaz levhasının çıplak bir silikon "taşıyıcı" levhaya füzyonla bağlanması durumunda bağlanmayla ilgili distorsiyonun meydana geldiğini açıkladı. Bağlama işlemi esasen cihaz levhasını gererek onu taşıyıcı levhaya uymaya zorlar. Cihaz katmanına erişim sağlamak için gerekli olan orijinal silikon kalınlığının yaklaşık 500 nm dışında tamamının çıkarılması, ortaya çıkan stresin bir kısmını hafifletir ve cihaz katmanının kendisini yeni desteğe uydurmasına olanak tanır.

Ancak cihaz katmanının nihai topografyası tam devre yapısına bağlıdır ve bu nedenle önceden tahmin edilmesi zordur. Arka taraf temasları için gereken kaplama hassasiyetine ulaşmak, levha şeklinin dikkatli bir şekilde ölçülmesini ve alan bazında litografi düzeltmelerini gerektirir. imec mantık ve CMOS program direktörü Naoto Horiguchi, sürecin araştırma ortamlarında çok zaman aldığını söyledi. Seri üretim için endüstrinin distorsiyon miktarını azaltması ve bunu telafi etmenin daha etkili bir yolunu bulması gerektiğine inanıyor.

Orta dielektrik yönetimi

Bir CFET'te üst cihazdan alt güç şebekesine temas sağlamak, yüksek en-boy oranlı gravür gerektirir. Intel bu süreci radikal bir değişiklik olarak değil, PowerVia planının bir uzantısı olarak görüyor. Nano tabaka transistörlere kıyasla CFET'lerin bir orta dielektrik katman NFET ve PFET'i birbirinden izole etmek için. Entegrasyon şemasına bağlı olarak bu katman, başlangıçta nano tabaka yapısını oluşturacak olan Si/SiGe heteroyapısı içinde bir dielektrik katman olarak oluşturulabilir. Alternatif olarak, kanal nano tabakalarını oluşturan ve izole eden seçici aşındırma ve oksidasyon adımı, orta dielektrik katman için daha kalın bir oksit de oluşturabilir. Ortadaki dielektrik baştan beri hetero yapının bir parçasıysa, üst cihaz temasına yönelik derin aşındırma işleminin dielektrik katmanını hesaba katması gerekecektir. Dielektrik daha sonra takılırsa Si/SiGe aşındırma seçiciliğinin dikkatli bir şekilde kontrol edilmesi gerekecektir.

Sıralı 3D entegrasyonu, CFET'lere daha fazla süreç değişikliği gerektiren daha zorlu ve iddialı bir yaklaşım önermektedir. Sıralı bir 3D yığın içindeki levhalar potansiyel olarak farklı türde aktif öğelere sahip olabileceğinden veya yalnızca kablolama ve pasif bileşenler içerebileceğinden, levha süreci ile paketleme süreci arasındaki çizgiyi bulanıklaştırır. Horiguchi, en azından prensipte, alt cihazlar için güç ve sinyalleri alt levhanın arka tarafına, üst cihazlar için güç ve sinyalleri üst levhanın üst tarafına yönlendirmenin mümkün olacağını söyledi. Ancak pratikte, NFET ve PFET transistörleri arasında yakın bağlantı ve kapıdan kapıya bağlantı, bir CFET hücresi için esastır.

Intel baş mühendisi Marko Radosavljeviç, iki transistörü ayıran orta dielektrik kalınlığının devre tasarımının kapasitans ve güç dağılımı gibi diğer yönleriyle sınırlandığını gözlemledi. Sıralı bir 3 boyutlu süreç, üretimi basitleştiriyor gibi görünebilir, ancak üreteceği nispeten kalın orta dielektrik katman, diğer kısıtlamaları karşılayamayabilir.

Isıdan kurtulmak

CFET'ler monolitik veya sıralı olarak inşa edildikten sonraki büyük endişe ısı dağıtımıdır. Çip seviyesinde, arka taraftaki güç ısı dağıtımına yardımcı olur. Daha kalın güç hatları daha az dirençlidir ve cihazın arkasına termal bir yol sağlar. Ancak herhangi bir spesifik lokasyonda ısıtma miktarı hala iş yüküne ve yerel çevreye bağlıdır. Cihazı arka taraftan ayıran dielektrik katman, ısı transferine engel teşkil etmektedir. Genel ısı ekstraksiyonu yeterli olsa bile, toplu silikon alt tabakanın ısı yayma etkisi olmadan sıcak noktalar görünebilir. Aralık ayındaki IEEE Elektron Cihazı toplantısında sunulan çalışmada Anabela Veloso ve Imec'teki meslektaşları, SiO2'nin değiştirilmesinin gerekli olduğunu belirtti.2 SiN içeren bariyer oksit, ısı yayılımını iyileştirebilir ve sıcak nokta riskini azaltabilir.[3]

CFET'lerden ısı yayılımını yönetmek halen devam eden bir çalışmadır. Daha fazla nano tabaka eklemek, her bir katmandaki akım yoğunluğunu azaltır, böylece ısınma azalır, ancak aynı zamanda kapasitans da artar. Kanalın paralel nano tabakalara parçalanması, aradaki dielektrik katmanların ısı taşınmasına engel oluşturması nedeniyle ısı dağılımını azaltır. Yaprak sayısını artırmak akım yoğunluğunu azaltsa da 2022 VLSI Teknoloji Sempozyumu'nda sunulan çalışma, agresif ölçeklendirmenin önemli bir termal maliyet taşıdığını gösterdi. Simülasyonlarda, N3 düğümündeki 2 sayfalık bir CFET, N5 finFET'in cihaz düzeyindeki kendi kendine ısınmasının neredeyse iki katı kadardı.[4] Olumlu tarafı, transistörlerin istiflenmesiyle geri kazanılan alanın bir kısmı CFET kanallarını genişletmek için kullanılabilir, bu da yine akım yoğunluğunu ve ısınmayı azaltır.

Son husus devre gürültüsüdür. Ön tarafta güç hatları bulunan devrelerde Kobrinsky, güç hatlarının sinyal hatlarını birbirinden izole ederek karışmayı azalttığını söyledi. Intel'in PowerVia mimarisi, bu izolasyon etkisi yerine ön tarafta gürültü kalkanları içerir.

Ancak sonuçta hem sinyal hem de güç hatlarının arka tarafa ve devrenin geri kalanına doğru yol alması gerekecek. Devre yoğunluğu arttıkça kalabalıklaşma sorun haline gelebilir.

Sonuç

Transistör entegrasyon şemasının ötesinde, hem arka güç hem de 3 boyutlu devre yapıları tasarım araç kutusunu genişletir. Arka taraftaki bir elektrik şebekesi, ESD korumasını veya güç düzenleme elemanlarını içerebilir. Onceki gibi tartışılan, sıralı 3D entegrasyonu, transistör katmanının hem üstüne hem de altına bellekte hesaplama öğeleri eklemek için kullanılabilir. Heterojen paketleme şemalarına dahil edilen heterojen bir CMOS platformu, endüstrinin daha kompakt, daha yetenekli sistemler arayışında bir sonraki adım olabilir.

Referanslar

- Geert Hellings, Gaspard Hiblot ve Julien Ryckaert, "Güç Dağıtımını İyileştirmek İçin Süreç Mimarileri Değişiklikleri", IEDM Kısa Kursu 1, San Francisco, Aralık 2022.

- M. Kobrinsky ve diğerleri, "Arka Taraf Güç Dağıtımı ve 3D Cihaz Yığınlama ile Geleceğin Teknolojisi Düğümleri için Süreç Yenilikleri", IEDM, San Francisco, 2023. DOI:10.1109/IEDM45741.2023.10413882

- Anabel Veloso ve diğerleri, "Arka Taraf Güç Dağıtımı: Oyun Değiştirici ve Gelişmiş Mantık Ölçeklendirmenin Temel Etkinleştiricisi ve Yeni STCO Fırsatları", IEDM, San Francisco, Aralık 2023. DOI: 10.1109/IEDM45741.2023.10413867

- B. Vermeersch, ve diğerleri, "iN8–iN2 CMOS Mantık Hücrelerinde Kendiliğinden Isıtma: Mimarinin Termal Etkisi (FinFET, Nanosheet, Forksheet ve CFET) ve Ölçeklendirme Arttırıcılar", 2022 IEEE VLSI Teknolojisi ve Devreleri Sempozyumu. DOI: 10.1109/VLSITechnology ve Cir46769.2022.9830228.

İlgili Okuma

Monolitik ve Sıralı 3D ile CFET'ler Oluşturma

Gelecekteki transistör küçülmeleri açısından alanın faydaları önemlidir, ancak üretim zorlukları devam etmektedir.

CFET'ler Sektörün Dikey Gitmesine Yardımcı Olacak mı?

nMOS'un pMOS cihazlarının üzerine istiflenmesi, monolitik veya sıralı akışlar kullanılarak mümkündür. Her birinin artıları ve eksileri vardır.

Arka Taraf Güç Dağıtımı Yeni Termal Sorunlara Yol Açıyor

Koruma eksikliği, yönlendirme sorunları ve yeni mekanik gerilimler standart hücre tasarımı üzerinde geniş bir etkiye sahip olabilir.

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiengineering.com/powering-cfets-from-the-backside/

- :vardır

- :dır-dir

- :olumsuzluk

- $UP

- 1

- 10

- 2%

- 2022

- 2023

- 3d

- 4

- a

- Hakkımızda

- yukarıdaki

- erişim

- Hesap

- elde

- aktif

- eklemek

- ekleme

- Ekler

- ilerlemek

- ileri

- etkiler

- tekrar

- agresif

- AL

- hiza

- Türkiye

- izin vermek

- Izin

- veriyor

- neredeyse

- tek başına

- Ayrıca

- hırslı

- miktar

- an

- ve

- herhangi

- görünmek

- yaklaşım

- mimari

- mimarileri

- ARE

- ALAN

- savundu

- AS

- boy

- yönleri

- At

- çekici

- mevcut

- b

- Arka

- bariyer

- merkezli

- BE

- Çünkü

- müşterimiz

- Başlangıç

- olmak

- inanıyor

- altında

- ben

- faydaları

- Daha iyi

- arasında

- Büyük

- Biggest

- Bulanıklaştırma

- bağlı

- DESTEKLEYCLER

- her ikisi de

- Alt

- kutu

- geniş

- yığın

- iş

- fakat

- by

- CAN

- yetenekli

- dikkatli

- hücre

- Hücreler

- meydan okuma

- zorluklar

- zor

- değişiklik

- Değiştiren

- değişiklikler

- Telegram Kanal

- kanallar

- yonga

- devre

- devreleri

- Kapanış

- arkadaşları

- kompakt

- karşılaştırılabilir

- tazmin etmek

- tamamlamak

- bileşenler

- İlgilendirmek

- Konferans

- tıkanıklık

- bağlantı

- bağ

- Bağlantılar

- Bağlantı

- Eksiler

- dikkate

- zoraki

- kısıtlamaları

- inşa

- tüketen

- UAF ile

- kontaklar

- içermek

- kontrol

- Düzeltmeler

- Ücret

- olabilir

- kurs

- yaratmak

- çevrimiçi kurslar düzenliyorlar.

- oluşturur

- akım

- derin

- teslim

- gösterdi

- yoğunluk

- bağlı

- bağlıdır

- Dizayn

- tasarımcıları

- gelişme

- cihaz

- Cihaz

- farklı

- zor

- boyutlar

- direkt

- yönetmen

- çarpıtma

- do

- yok

- çift

- aşağı

- Damla

- E&T

- her

- Efekt

- verimli

- ya

- elemanları

- ortadan kaldırır

- çıkma

- enabler

- mühendis

- çevre

- gözünün önüne getirmek

- öngörülüyor

- gerekli

- esasen

- Hatta

- evrim

- kesin

- sadece

- Genişletmek

- açıkladı

- Maruz kalma

- uzatma

- çıkarma

- aşırı

- FAIL

- adam

- az

- Incir

- doldurmak

- son

- bulmak

- Ad

- beş

- Akışları

- ayak izi

- İçin

- zorlama

- Airdrop Formu

- parçalanma

- Francisco

- itibaren

- ön

- daha fazla

- füzyon

- gelecek

- Geleceğin teknolojisi

- Kazanç

- oyun

- oyun değiştirici

- almak

- Go

- Grid

- grup

- vardı

- Yarım

- Var

- he

- yükseklik

- yardım et

- yardımcı olur

- Yüksek

- Ancak

- HTTPS

- IEEE

- if

- darbe

- uygulama

- iyileştirmek

- in

- birleştirmek

- Anonim

- birleştirir

- Artışlar

- artan

- artımlı

- bireysel

- sanayi

- endüstrinin

- yenilikler

- entegre

- bütünleşme

- Intel

- içine

- İzolatlar

- konu

- sorunlar

- IT

- ONUN

- kendisi

- koruma

- anahtar

- çeşitleri

- büyük

- sonra

- tabaka

- katmanları

- en az

- uzunluk

- az

- seviye

- sevmek

- Muhtemelen

- çizgi

- hatları

- yerel

- yer

- mantık

- Çok

- yapmak

- üretim

- Kitle

- maksimum genişlik

- Mayıs..

- ölçümler

- mekanik

- Neden

- toplantı

- metal

- Orta

- olabilir

- yekpare

- Daha

- daha verimli

- çoğu

- hareketli

- neredeyse

- gerekli

- gerek

- ihtiyaçlar

- yeni

- sonraki

- düğüm

- düğümler

- Gürültü

- ünlü

- numara

- gözlenen

- of

- on

- Fırsatlar

- Opsiyonlar

- or

- orijinal

- Diğer

- dışarı

- tüm

- ambalaj

- Paralel

- Bölüm

- belirli

- pasif

- yol

- Zift

- platform

- Platon

- Plato Veri Zekası

- PlatoVeri

- pozitif

- mümkün

- potansiyel

- güç kelimesini seçerim

- Güç ızgarası

- Açılması

- uygulama

- Hassas

- tahmin

- sundu

- başkan

- Önceden

- Anapara

- prensip

- muhtemelen

- süreç

- üretmek

- üretim

- Programı

- Ilerleme

- ilerleme

- önermektedir

- Artıları

- koruma

- sağlamak

- arayışı

- radikal

- demiryolu

- raylar

- daha doğrusu

- oran

- ulaşmak

- kurtarır

- azaltmak

- azaltır

- azaltarak

- bağıl

- Nispeten

- Dinlenmek

- rahat

- kalmak

- giderme

- gerektirir

- gereklidir

- gerektirir

- araştırma

- Direniş

- DİNLENME

- Ortaya çıkan

- Sonuçlar

- devrimci

- Kurtulmak

- Risk

- yol

- oda

- yönlendirme

- koşmak

- ishal

- Adı geçen

- aynı

- San

- San Francisco

- Tasarruf

- ölçekleme

- plan

- şemaları

- görmek

- seçici

- satmak

- ayırma

- ciddi

- ayarlar

- şiddetli

- Shape

- yaprak

- kısa

- gösterdi

- yan

- işaret

- sinyalleri

- önemli

- Silikon

- basitleştirir

- basitleştirmek

- simülasyonları

- tek

- ALTINCI

- daha küçük

- So

- çözüm

- biraz

- Kaynak

- uzay

- özel

- Yayma

- yığın

- yığılmış

- istif

- Yığınları

- standart

- adım

- Yine

- stres

- yapı

- yapılar

- Yüzey

- yeterli

- destek

- Sempozyum

- Sistemler

- teknikleri

- Teknoloji

- Teknoloji gelişimi

- göre

- o

- The

- Alan

- ve bazı Asya

- sonra

- Orada.

- böylece

- bu nedenle

- termal

- Re-Tweet

- thomas

- Bu

- gerçi?

- üç

- İçinden

- zaman

- için

- araç

- üst

- parça

- transfer

- taşıma

- Iki kere

- iki

- eninde sonunda

- kullanım

- Kullanılmış

- kullanım

- kullanma

- dikey

- dikine

- çok

- mengene

- Başkan Yardımcısı

- Gösterim

- Yol..

- İYİ

- ne zaman

- olup olmadığını

- hangi

- süre

- Daha geniş

- irade

- ile

- içinde

- olmadan

- İş

- olur

- zefirnet