Công cụ xác thực sau silicon không phải là một ý tưởng mới nhưng đây là một bước ngoặt. Sử dụng mô phỏng (tiền silicon) để chọn cấu trúc quan sát gỡ lỗi cho công cụ trong silicon. Paul Cunningham (GM, Xác minh tại Cadence), Raúl Camposano (Silicon Catalyst, doanh nhân, cựu CTO của Synopsys) và tôi tiếp tục loạt bài về các ý tưởng nghiên cứu. Như mọi khi, thông tin phản hồi chào mừng.

![]()

Sự đổi mới

Lựa chọn của tháng này là Cơ sở hạ tầng mô phỏng để đánh giá các xác nhận phần cứng để xác thực sau silicon. Bài báo đã được trình bày tại Giao dịch IEEE 2017 trên VLSI. Các tác giả đến từ Đại học McMaster, Hamilton, ON, Canada

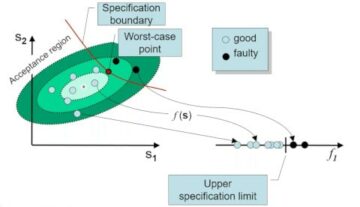

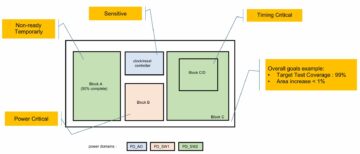

Các tác giả phân biệt giữa các lỗi logic và lỗi điện sau silicon và dành sự chú ý của họ trong bài báo này cho các lỗi điện, có thể phát hiện được thông qua các lần lật bit trong thất bại. Cách tiếp cận của họ là xác định một tập hợp các xác nhận tối ưu trong phân tích tiền silicon. Sau đó, họ triển khai chúng bằng silicon để hỗ trợ gỡ lỗi sau silicon. Phân tích trước silicon tương tự như lỗi trong phân tích an toàn, đưa lỗi vào flops tương ứng với lỗi điện, như chúng gợi ý trong bài báo. Họ tạo ra một danh sách các xác nhận ứng cử viên bằng cách sử dụng tổng hợp xác nhận; cốt lõi của sự đổi mới của họ là cung cấp một phương pháp để phân loại các xác nhận này bằng mức độ hiệu quả của từng xác nhận trong việc phát hiện nhiều lỗi.

Việc tạo đầu vào là ngẫu nhiên, phân tích các lỗi được đưa vào (được coi là tạm thời) theo trình tự. Chúng cho phép số chu kỳ do người dùng chỉ định để phát hiện mỗi lỗi. Trong giai đoạn tiếp theo, họ đo lường hiệu quả bằng hai kỹ thuật bao phủ khác nhau. Đối với vùng phủ sóng của flip-flop, chúng tính một xác nhận nếu nó bắt được lỗi được đưa vào trên bất kỳ flop nào. Trong vùng phủ sóng bit-flip, chúng cho điểm xác nhận số lỗi được phát hiện trên các flop riêng biệt. Các chỉ số này, cùng với ước tính diện tích, chúng sử dụng (luân phiên) để chọn xác nhận ưa thích nào.

Quan điểm của Paul

Bài viết này kết hợp độc đáo với chúng tôi Tháng 2020 năm XNUMX blog về phát hiện lỗi nhanh (QĐD). QED tăng tốc phát hiện lỗi chức năng sau silicon, trong đó blog này tập trung vào phát hiện lỗi điện sau silicon. Bài báo này dễ đọc, mặc dù nó giúp đọc tài liệu tham khảo lần đầu tiên [23].

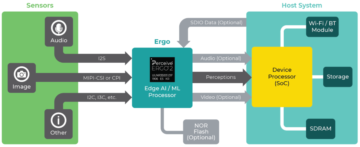

Lỗi điện rất khó phát hiện và thậm chí sau đó cũng khó tái tạo và tìm ra nguyên nhân vật lý cơ bản. Các tác giả đề xuất một phương pháp, thông qua logic nhúng, để phát hiện khi nào những lỗi như vậy khiến một flop chuyển sang một giá trị không chính xác (họ không tìm hiểu sâu hơn việc tìm ra những lần lật này).

Trọng tâm của bài báo và tài liệu tham khảo đồng hành của nó [23] là một phương pháp gồm nhiều bước để tạo và tổng hợp logic phát hiện này. Nó bắt đầu với việc khai thác các thuộc tính của thiết kế dưới dạng các xác nhận tạm thời bằng cách sử dụng Công cụ khai thác vàng. Họ xếp hạng các xác nhận dựa trên ước tính về khả năng phát hiện các lần lật bit và ước tính về diện tích/chi phí nối dây để thực hiện trong silicon. Xếp hạng dựa vào việc chạy nhiều mô phỏng tiền silicon với các xác nhận ứng cử viên, đưa ra các lỗi lật bit và đếm các lần lật được phát hiện theo các xác nhận. Trong bài báo gốc, họ đã sử dụng mô phỏng logic, ở đây họ tăng tốc các mô phỏng này bằng cách ánh xạ thiết kế tới một bo mạch FPGA của Altera.

Tôi thích cách họ tập hợp một số cải tiến thành một phương pháp nhất quán để phát hiện lật bit sau silicon: khai thác xác nhận, tổng hợp xác nhận và chức năng xếp hạng trang nhã để lựa chọn xác nhận. Tuy nhiên, phần kết quả của bài báo chỉ ra rằng việc phát hiện lật bit trong n% số flip-flop yêu cầu tăng khoảng n% diện tích thiết kế. Điều này có vẻ khó khăn đối với ứng dụng thương mại, đặc biệt là vì nó chỉ giúp tìm ra các lỗi về điện. Người ta có khả năng đạt được kết quả tương tự bằng cách nhân bản hình nón logic điều khiển một flip-flop, sau đó so sánh đầu ra của logic nhân bản này với logic ban đầu. Điều này dường như sẽ tạo ra một chi phí khu vực tương tự như phương pháp của họ, trong giới hạn sao chép toàn bộ thiết kế (tức là 100% chi phí khu vực) để phát hiện các lần lật trong 100% số lần thất bại trong thiết kế.

Quan điểm của Raúl

Bài viết được khép kín với một lượng chi tiết hợp lý. Các tác giả đã chạy thử nghiệm cho 3 mạch tuần tự ISCAS (khoảng 12K cổng, 2000 FF). Các thử nghiệm chuẩn bị đưa vào 256 lỗi trên mỗi lần lật và sử dụng tất cả các xác nhận do GoldMine tạo ra. Do khả năng hạn chế của FPGA, các tác giả đã chia nhỏ các lần chạy thành 45 “phiên” cho một mạch. Kết quả cho thấy, ngay cả với 45 phiên, tốc độ phân tích so với mô phỏng là 20-500 lần (chỉ có tối đa 8 lần tiêm lỗi do mô phỏng quá chậm, 105 giờ). Độ phủ Flip-Flop tối đa có thể đạt được là 55%, 89% và 99% cho 3 mạch. Số lượng xác nhận được khai thác kiểm soát phạm vi bảo hiểm.

Chạy với các xác nhận đã chọn (tương ứng với 5-50% chi phí khu vực) và 1-256 lần tiêm dẫn đến độ bao phủ bit 2.2% -34%. Hầu hết thời gian, công cụ khai thác khẳng định chạy trong 228 giờ. Một điều khiến tôi bối rối là dữ liệu của họ về thời gian chạy so với lỗi được đưa vào. Mức tăng có vẻ hợp lý (tuyến tính) trong mô phỏng. Nhưng trong mô phỏng, nó nhảy ồ ạt, từ 0.045h lên 5.4h để tăng từ 2 đến 8 lần tiêm lỗi. Tôi muốn giải thích thêm về điểm này.

Đây là một bài viết về phương pháp. Tôi thích điều đó khá nhiều, mỗi bước có thể được thay thế bằng một công cụ thương mại. Cùng với việc sử dụng một bảng FPGA lớn (làm trình giả lập), phương pháp này sẽ mở rộng quy mô. Tất nhiên, các phương pháp rất khó thương mại hóa, nhưng đó là một ứng dụng tuyệt vời cho công nghệ hiện có!

Quan điểm của tôi

Phương pháp khám phá một kỹ thuật phân tích an toàn để gỡ lỗi sau silicon rất hấp dẫn. Một ý tưởng mới lạ, mặc dù dẫn đến một kết quả hơi phi thực tế đối với ứng dụng thương mại.

Chia sẻ bài đăng này qua: Nguồn: https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/

- 2020

- Tất cả

- phân tích

- Các Ứng Dụng

- KHU VỰC

- tác giả

- Một chút

- Blog

- bảng

- Bug

- lỗi

- Nhịp

- Sức chứa

- Catch

- Nguyên nhân

- thương gia

- tiếp tục

- CTO

- dữ liệu

- Thiết kế

- chi tiết

- Phát hiện

- lái xe

- Hiệu quả

- Doanh nhân

- dự toán

- công bằng

- Tên

- fpga

- chức năng

- Gates

- GM

- phần cứng

- tại đây

- Độ đáng tin của

- HTTPS

- ý tưởng

- IEEE

- Tăng lên

- Cơ sở hạ tầng

- sự đổi mới

- IT

- lớn

- hàng đầu

- Hạn chế

- Danh sách

- đo

- Metrics

- Khai thác mỏ

- Giấy

- đề xuất

- nghiên cứu

- Kết quả

- chạy

- Sự An Toàn

- chọn

- Loạt Sách

- định

- mô phỏng

- chia

- hỗ trợ

- thời gian

- Giao dịch

- xoắn

- trường đại học

- giá trị

- Xác minh

- Versus