Phong trào RISC-V đã phát triển nhanh chóng nhờ có nhiều lựa chọn mà nó mang lại cho các nhà thiết kế. Tuy nhiên, tính linh hoạt lớn tạo ra những thách thức riêng. Một là cách phân tích, tối ưu hóa và xác minh thiết kế lõi RISC-V chưa được chứng minh với những thay đổi vi kiến trúc tiềm năng được cho phép trong giới hạn của thông số kỹ thuật. S2C, nổi tiếng với công nghệ tạo mẫu dựa trên FPGA, đã đưa ra bản cập nhật tại #60DAC cho chiến lược tối ưu hóa và phân tích kiến trúc RISC-V có hệ thống mới nổi, đồng thời bổ sung khả năng lập mô hình và mô phỏng.

Ba giai đoạn để phân tích kiến trúc RISC-V

RISC-V khác với các kiến trúc bộ xử lý khác ở mức độ tùy chỉnh có thể thực hiện được – từ đơn vị thực thi và cấu hình đường dẫn cho đến việc thêm các hướng dẫn tùy chỉnh. Các nhà phát triển đang khám phá những cấu hình RISC-V khác nhau phù hợp nhất trong nhiều ứng dụng, trong đó một số định nghĩa vẫn còn mơ hồ. Hỗ trợ EDA vẫn chưa bắt kịp; các công cụ cơ bản tồn tại nhưng có rất ít nền tảng mô hình hóa tiên tiến.

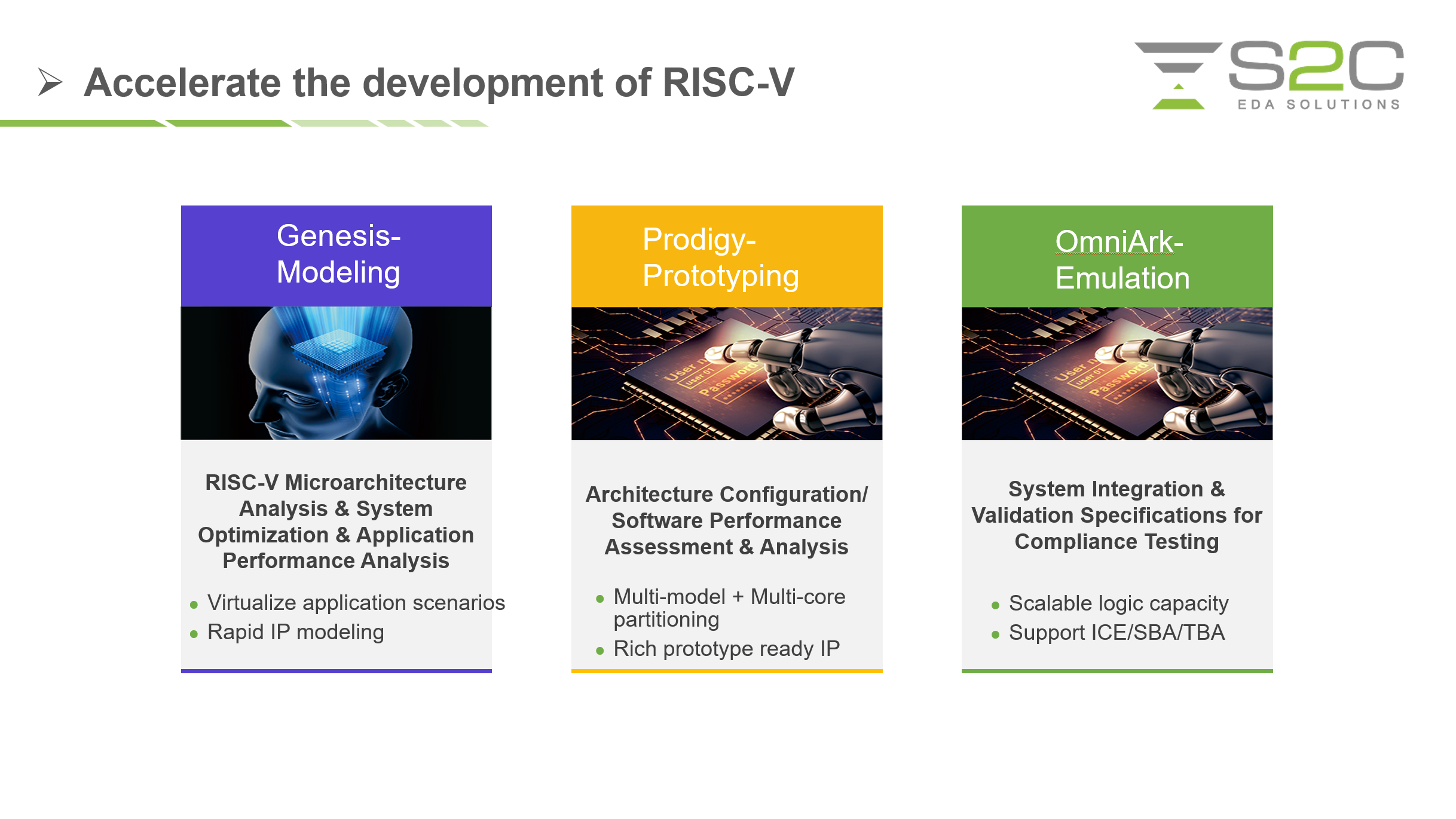

Những điều kiện này khiến các nhóm gặp khó khăn: nếu họ mở rộng bộ hướng dẫn RISC-V để triển khai, họ phải tạo các mô hình mới chính xác theo chu kỳ cho các hướng dẫn đó trước khi đánh giá hiệu suất, được mô phỏng hoặc mô phỏng. S2C đang nỗ lực lấp đầy khoảng trống này bằng một chuỗi hoàn chỉnh để phân tích và tối ưu hóa kiến trúc RISC-V có hệ thống, bao gồm một công nghệ quen thuộc cùng với hai công nghệ khác.

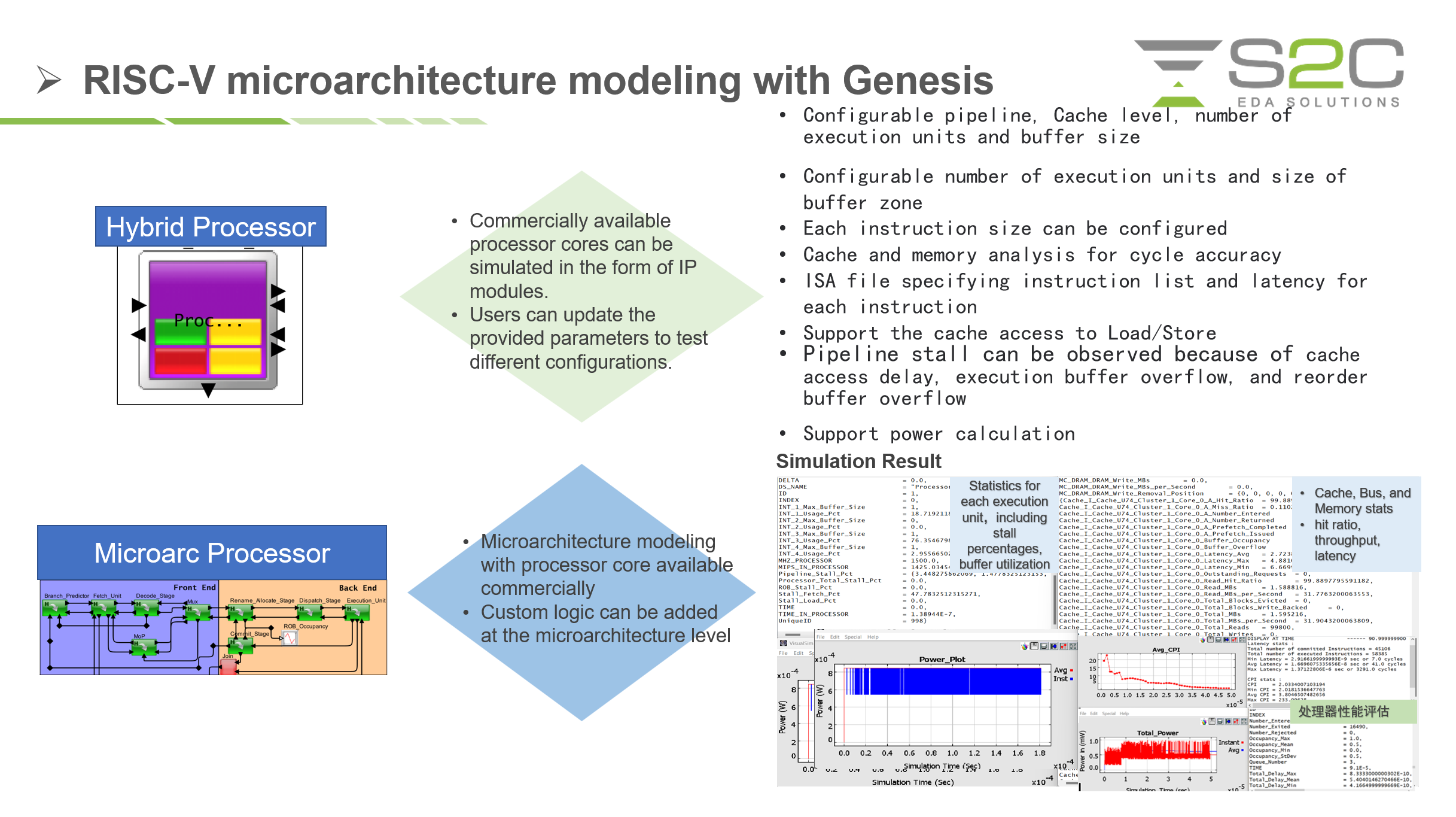

Đầu tiên trong chuỗi là nền tảng trừu tượng hóa mô hình “core master” RISC-V mới của S2C, Genesis. Nó cung cấp mô hình ngẫu nhiên, mô hình kiến trúc hệ thống và mô hình chính xác theo chu kỳ, với mức độ chính xác ngày càng tăng khi các mô hình tăng thêm độ trung thực. Genesis cho phép mô phỏng các lõi RISC-V có bán trên thị trường dưới dạng mô-đun IP, sau đó cập nhật các tham số hoặc thêm logic tùy chỉnh vào vi kiến trúc. Những mô phỏng này cho phép tối ưu hóa lõi sớm hơn.

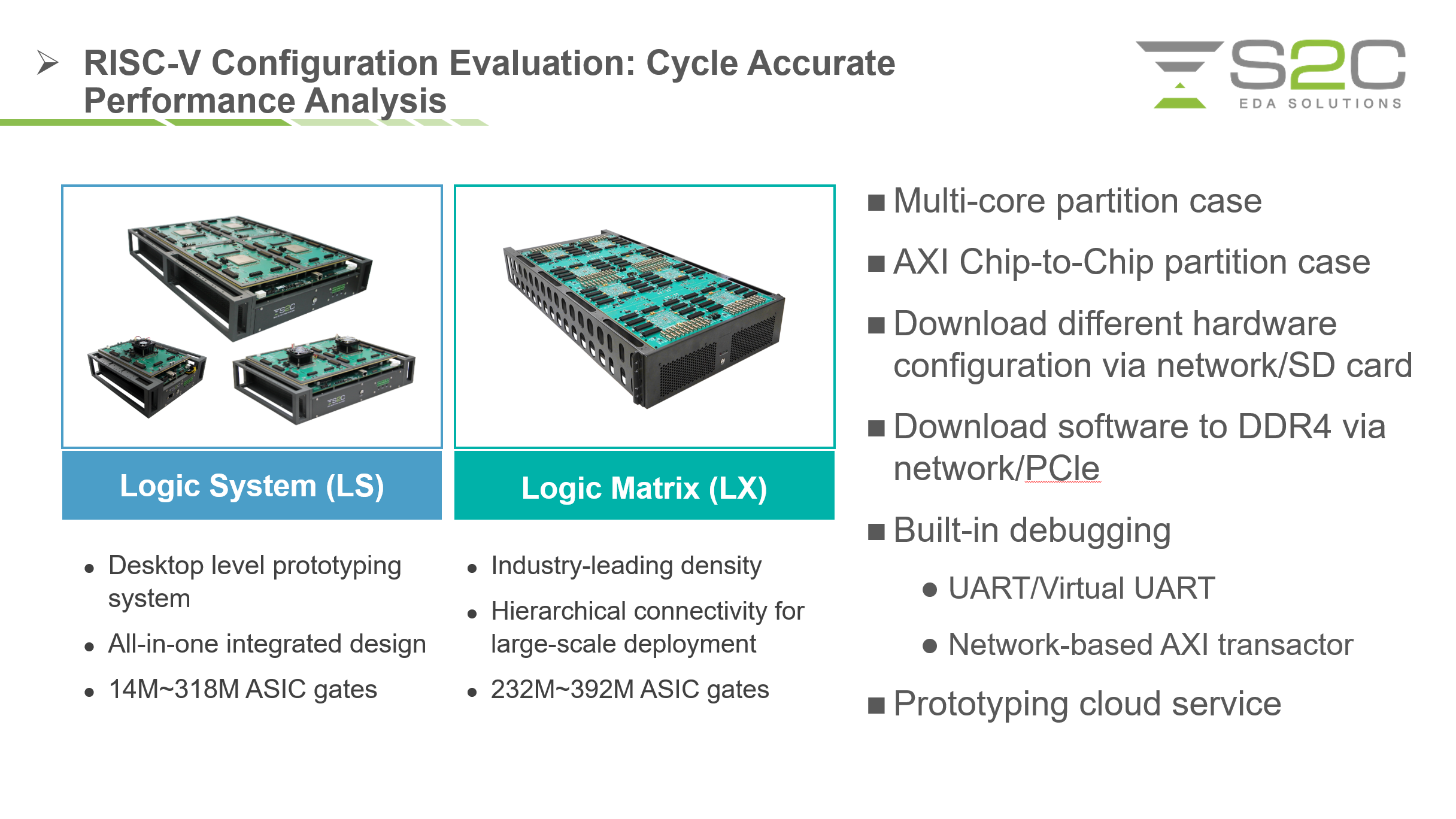

Giữ vị trí trung tâm trong chuỗi phân tích là dòng nguyên mẫu S2C Prodigy, hỗ trợ các nguyên mẫu dựa trên FPGA để gỡ lỗi logic phần cứng, đánh giá hiệu suất cơ bản và phát triển phần mềm sớm. Phần cứng tạo mẫu Prodigy cũng chấp nhận các mô-đun I/O sẵn có do S2C phát triển để kích thích và tiêu thụ tín hiệu trong thế giới thực xung quanh vùng ngoại vi của SoC, cũng như xác minh hiệu suất IP RISC-V.

Khả năng mô phỏng mới đi kèm với hệ thống mô phỏng lai OmniArk của S2C, có khả năng xác minh siêu quy mô các SoC RISC-V. OmniArk chuyên biên soạn SoC ô tô và tự hào có khả năng sửa lỗi mạnh mẽ cho môi trường xác minh hiệu quả. Nó có quy mô lên tới 1 tỷ cổng cho các thiết kế lớn và hỗ trợ các chế độ xác minh như QEMU, TBA và ICE.

Một ví dụ: hợp tác trong dự án cốt lõi XiangShan RISC-V

Các mô hình hành vi chính xác của lõi RISC-V được thực hiện thông qua các quy trình lập mô hình ban đầu, tạo nguyên mẫu dựa trên FPGA và mô phỏng phần cứng. Việc cung cấp cho các nhà thiết kế khả năng kiểm soát tốt hơn cả IP và mô hình sẽ cho phép các tác vụ chỉ có thể thực hiện được trong các nguyên mẫu phần cứng chuyển sang hoạt động phân tích ảo sớm hơn trong chu trình thiết kế, tạo ra nhiều cơ hội tối ưu hóa hơn.

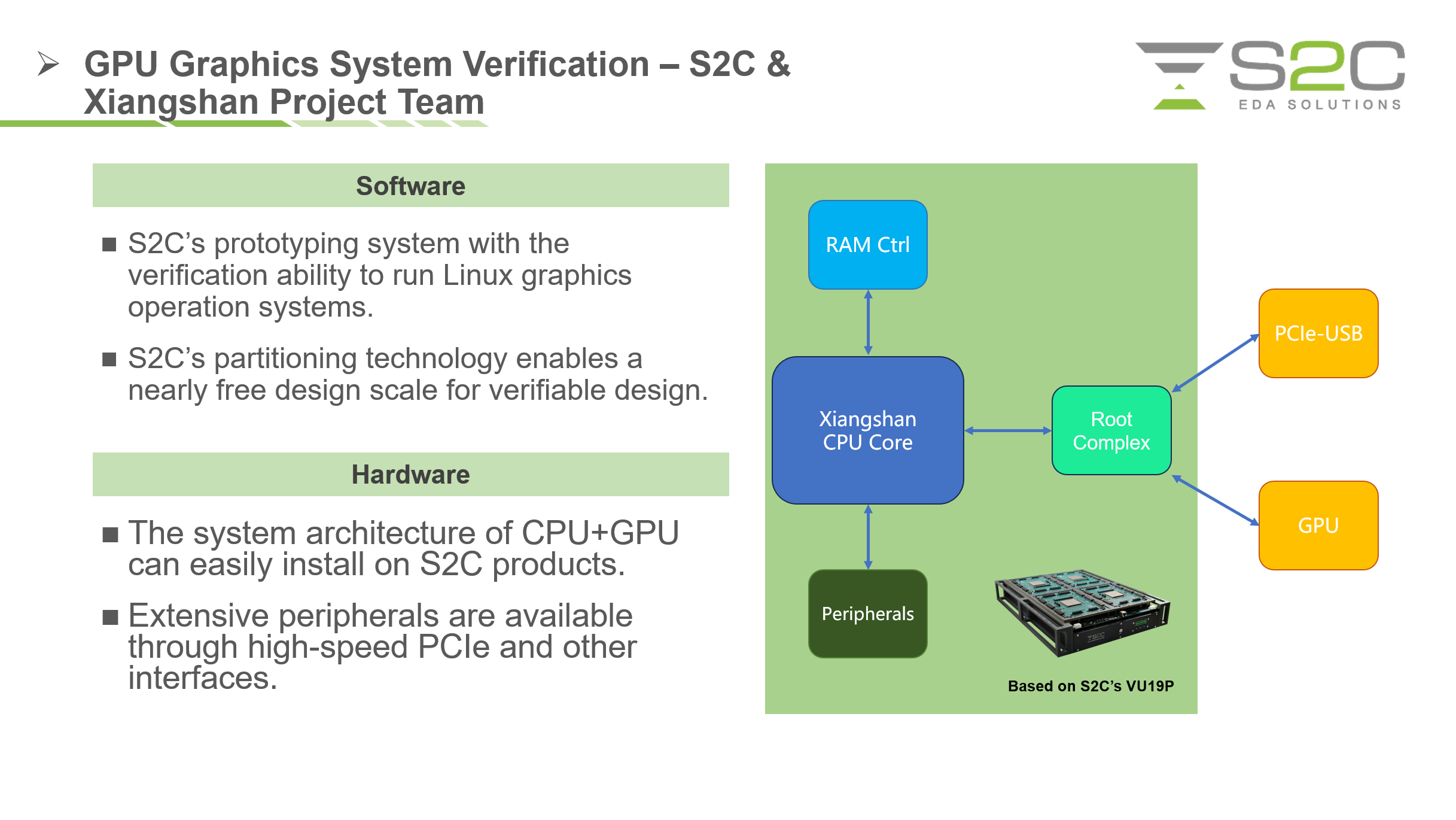

Một ví dụ về phân tích và tối ưu hóa kiến trúc RISC-V có hệ thống là sự hợp tác của S2C với nhóm dự án XiangShan có trụ sở tại Viện Hàn lâm Khoa học Trung Quốc. XiangShan là một triển khai RISC-V siêu vô hướng, sáu chiều, không theo thứ tự nhắm vào một biến thể Linux cho hệ điều hành của nó.

Nhóm XiangShan đã sử dụng các sản phẩm S2C để tạo nền tảng xác minh cốt lõi được tích hợp với GPU bên ngoài và các thiết bị ngoại vi khác. Các phân vùng lõi siêu quy mô thành nền tảng tạo mẫu dựa trên S2C FPGA, với các thiết bị ngoại vi được bổ sung thông qua PCIe và các giao diện khác.

Ying J. Chen, Phó Chủ tịch của S2C cho biết: “Khi công nghệ RISC-V đã thâm nhập vào nhiều lĩnh vực khác nhau, nguồn mở, tính đồng nhất và khả năng mở rộng cao của nó đang xác định lại tương lai của điện toán”. “Ba dòng sản phẩm chính của S2C có thể cung cấp nhiều giải pháp khác nhau như đánh giá hiệu suất phần mềm để phân tích vi kiến trúc, tích hợp hệ thống và kiểm tra tuân thủ thông số kỹ thuật dựa trên RISC-V.”

Chúng tôi mong đợi S2C sẽ sớm có thêm thông tin chi tiết về cách chuỗi phân tích và tối ưu hóa kiến trúc RISC-V có hệ thống kết hợp với các thông báo sản phẩm sắp tới của Hoa Kỳ – hiện tại, trang web tiếng Trung của S2C đã có một số thông tin về Genesis. Thông tin chi tiết hơn về dự án XiangShan RISC-V có tại hướng dẫn được đưa ra tại ASPLOS'23.

Cũng đọc:

Sirius Wireless hợp tác với S2C trên Hệ thống xác minh IP Wi-Fi6/BT RF để thiết kế chip tốt hơn

S2C đẩy nhanh tiến độ phát triển của Bluetooth LE Audio SoC

S2C giúp khách hàng đạt được quá trình xác minh chip GPU bảo mật hiệu suất cao

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Ô tô / Xe điện, Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- ChartPrime. Nâng cao trò chơi giao dịch của bạn với ChartPrime. Truy cập Tại đây.

- BlockOffsets. Hiện đại hóa quyền sở hữu bù đắp môi trường. Truy cập Tại đây.

- nguồn: https://semiwiki.com/prototyping/s2c-eda/333925-systematic-risc-v-architecture-analysis-and-optimization/

- : có

- :là

- :Ở đâu

- $ LÊN

- 1

- a

- sự trừu tượng

- Học viện

- tăng tốc

- Chấp nhận

- chính xác

- Đạt được

- hoạt động

- thêm vào

- thêm

- thêm

- tiên tiến

- Tất cả

- cho phép

- cho phép

- Ngoài ra

- an

- phân tích

- phân tích

- và

- Thông báo

- các ứng dụng

- kiến trúc

- LÀ

- xung quanh

- AS

- Đánh giá

- thẩm định, lượng định, đánh giá

- At

- âm thanh

- ô tô

- có sẵn

- dựa

- cơ bản

- bởi vì

- trước

- BEST

- Hơn

- Tỷ

- Bluetooth

- tự hào

- cả hai

- giới hạn

- nhưng

- by

- CAN

- khả năng

- khả năng

- có khả năng

- mang

- Catch

- chuỗi

- thách thức

- Những thay đổi

- chen

- Trung Quốc

- Chip

- lựa chọn

- khách hàng

- hợp tác

- Đến

- đến

- thương mại

- hoàn thành

- tuân thủ

- máy tính

- điều kiện

- cấu hình

- tiêu thụ

- điều khiển

- Trung tâm

- tạo

- tạo ra

- Tạo

- khách hàng

- tùy biến

- tùy chỉnh

- chu kỳ

- các định nghĩa

- Thiết kế

- thiết kế

- thiết kế

- chi tiết

- phát triển

- phát triển

- Phát triển

- Sớm hơn

- Đầu

- hiệu quả

- mới nổi

- cho phép

- cho phép

- Môi trường

- đánh giá

- ví dụ

- thực hiện

- tồn tại

- mong đợi

- Khám phá

- thêm

- ngoài

- tạo điều kiện

- quen

- gia đình

- Với

- vài

- lòng trung thành

- Lĩnh vực

- điền

- Linh hoạt

- Trong

- từ

- tương lai

- tương lai của máy tính

- Gates

- cho

- Genesis

- được

- Cho

- GPU

- phần cứng

- giúp

- Cao

- hiệu suất cao

- Độ đáng tin của

- Hướng dẫn

- Tuy nhiên

- HTTPS

- Hỗn hợp

- ICE

- if

- thực hiện

- in

- tăng

- thông tin

- hướng dẫn

- tích hợp

- hội nhập

- giao diện

- trong

- IP

- IT

- ITS

- nổi tiếng

- Ngôn ngữ

- lớn

- Rời bỏ

- niveaux

- Lượt thích

- dòng

- linux

- logic

- chính

- nhiều

- lớn

- max-width

- Tên đệm

- kiểu mẫu

- người mẫu

- mô hình

- chế độ

- Modules

- chi tiết

- phong trào

- nhiều

- phải

- Mới

- tại

- of

- off

- Cung cấp

- on

- hàng loạt

- ONE

- có thể

- mã nguồn mở

- hoạt động

- hệ điều hành

- Cơ hội

- tối ưu hóa

- Tối ưu hóa

- or

- Nền tảng khác

- Khác

- riêng

- thông số

- Đối tác

- hiệu suất

- thiết bị ngoại vi

- đường ống dẫn

- nền tảng

- Nền tảng

- plato

- Thông tin dữ liệu Plato

- PlatoDữ liệu

- có thể

- Bài đăng

- tiềm năng

- mạnh mẽ

- Chủ tịch

- Vấn đề

- Quy trình

- Bộ xử lý

- Sản phẩm

- Sản phẩm

- dự án

- nguyên mẫu

- tạo mẫu

- cho

- cung cấp

- Mau

- phạm vi

- Đọc

- thế giới thực

- Xác định lại

- nói

- khả năng mở rộng

- quy mô

- KHOA HỌC

- an toàn

- định

- thay đổi

- tín hiệu

- mô phỏng

- website

- So

- Phần mềm

- phát triển phần mềm

- Giải pháp

- một số

- Chẳng bao lâu

- chuyên

- đặc điểm kỹ thuật

- Vẫn còn

- kích thích kinh tế

- Chiến lược

- hỗ trợ

- Hỗ trợ

- hệ thống

- Lấy

- nhắm mục tiêu

- nhiệm vụ

- nhóm

- đội

- Công nghệ

- Kiểm tra

- Sản phẩm

- Tương lai

- cung cấp their dịch

- sau đó

- Kia là

- họ

- điều này

- những

- số ba

- Thông qua

- timeline

- đến

- bên nhau

- công cụ

- hai

- đơn vị

- sắp tới

- Cập nhật

- cập nhật

- us

- đã sử dụng

- biến thể

- khác nhau

- Xác minh

- xác minh

- thông qua

- phó

- Phó Chủ Tịch

- ảo

- Đường..

- TỐT

- rộng

- Phạm vi rộng

- không dây

- với

- ở trong

- đang làm việc

- nhưng

- YING

- zephyrnet