IC 布局在被代工厂或 IDM 接受制造之前,要经过广泛的设计规则检查以确保正确性。在芯片制造过程中会发生一种称为天线效应的现象,其中等离子体引起的损伤 (PID) 会降低 MOSFET 器件的可靠性。布局设计人员运行设计规则检查 (DRC) 以查找违反 PID 的区域,然后进行编辑以通过所有检查。

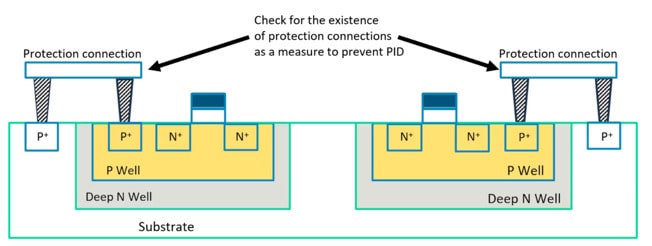

传统的天线设计规则将测量金属(或通孔)层与MOSFET栅极层的关系,如果面积比太大,则必须通过添加保护二极管来固定布局。

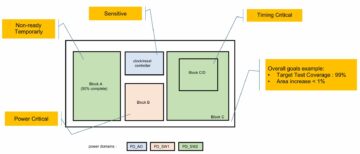

针对天线效应的传统 DRC 无法处理的一种 IC 布局方案是具有多个电源域的 AMS 设计,使用多个隔离的 P 型阱,如下所示。以下四种场景需要一种称为基于路径的验证的新方法。

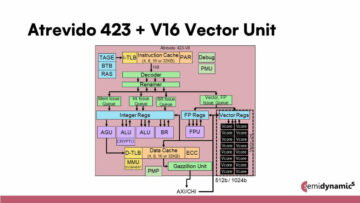

这四种布局方案只能通过 EDA 工具来检测,该工具在金属和 MOSFET 栅极层的面积计算过程中了解器件、连接性和电气路径。这就是 口径 PERC 西门子 EDA 工具应运而生,因为它可以执行复杂的基于路径的检查来识别 PID 区域、查找静电放电 (ESD) 问题并找到设计团队正在寻找的其他路径。以下是使用 Calibre PERC 的 PID 流程:

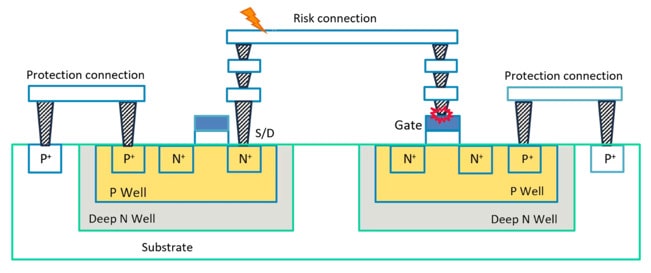

在 IC 布局上使用此流程并在 Calibre RVE 结果查看器中查看结果表明发现了 PID 违规,因为在金属 1 级别建立了风险连接,但直到金属 2 级别才发生保护连接。

下一个 PID 违规是根据金属层和 N 埋层 (nbl) 的不平衡面积比确定的。以紫色 (rve) 突出显示的区域是受害设备。

为了获得完整的 PID 覆盖,您的设计团队必须同时使用传统的基于 DRC 的天线检查和基于路径的检查。作为预防步骤,在设计阶段早期运行 DRC 类型检查。随着布局中更多金属连接的完成,然后形成跨隔离 P 型阱的路径,是时候添加基于路径的验证,以提供完整的覆盖范围。

在此早期 IC 布局中,需要运行传统的基于 DRC 的天线检查,以确认布局通过 PID 验证。

随着越来越多的金属路径添加到 IC 布局中,就需要使用基于路径的工具了,因为它可以正确理解风险连接和保护连接。

总结

IC 布局必须满足严格的设计规则,以通过所使用的代工厂或晶圆厂工艺设定的可靠性和良率要求。传统的基于 DRC 的天线设计规则仍可用于早期布局,但随着添加更多金属层以完成互连,则需要使用 Calibre PERC 进行基于路径的检查。

随着跨隔离 P 阱的路径建立,Calibre PERC 基于路径的流程可用于检查 IP、块/模块甚至全芯片级别的 IC 布局以进行签核。因此,建议同时使用这两种流程来满足可靠性和良率目标。

阅读 技术论文 在西门子在线。

相关博客

通过以下方式分享此帖子:

- :具有

- :是

- :在哪里

- ][p

- a

- 关于

- 公认

- 横过

- 加

- 添加

- 添加

- 所有类型

- an

- 和

- 天线

- 的途径

- 保健

- 国家 / 地区

- 地区

- AS

- At

- BE

- 因为

- 成为

- before

- 作为

- 如下。

- 之间

- 都

- 但是

- by

- 计算

- 被称为

- CAN

- 不能

- 查

- 检查

- 支票

- 芯片

- 购买的订单均

- 完成

- 完成

- 复杂

- 确认

- 地都

- 连接

- 连接方式

- 正确性

- 覆盖

- 损伤

- 设计

- 设计师

- 设计

- 检测

- 设备

- 设备

- 二极管

- 域名

- 刚果(金)

- ,我们将参加

- 早

- 早期

- 效果

- 影响

- 确保

- 成熟

- 甚至

- 广泛

- 最后

- 找到最适合您的地方

- 固定

- 流

- 流动

- 以下

- 针对

- 申请

- 发现

- 铸造厂

- 四

- 止

- 门

- 得到

- Go

- 理想中

- 团队

- 处理

- 发生

- 发生

- 有

- 突出

- HTTPS

- 确定

- 鉴定

- if

- in

- 互连

- IP

- 孤立

- 问题

- 问题

- IT

- JPG

- 知道

- 大

- 层

- 层

- 布局

- Level

- 各级

- 寻找

- 降低

- 制成

- 使

- 制造业

- 最大宽度

- 衡量

- 满足

- 某些金属

- 分钟

- 更多

- 多

- 必须

- 必要

- 全新

- 下页

- of

- on

- 在线

- 仅由

- or

- 其他名称

- 通过

- 通行证

- 路径

- 演出

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 加

- 帖子

- 功率

- 防止

- 过程

- 正确

- 保护

- 优

- 比

- 比

- 建议

- 可靠性

- 必须

- 岗位要求

- 成果

- 严格

- 风险

- 第

- 定位、竞价/采购和分析/优化数字媒体采购,但算法只不过是解决问题的操作和规则。

- 运行

- 脚本

- 情景

- 集

- 显示

- 如图

- Siemens

- So

- 东西

- 实习

- 步

- 仍

- 团队

- 这

- 区域

- 然后

- Free Introduction

- 通过

- 次

- 至

- 一起

- 也有

- 工具

- 传统

- 二

- 理解

- 直到

- 使用

- 用过的

- 运用

- 验证

- 企业验证

- 通过

- 受害者

- 观众

- 违反

- 违反

- 是

- 井

- 井

- 将

- 产量

- 您一站式解决方案

- 和风网