仪器化硅后验证并不是一个新想法,但这里有一个变化。使用(硅前)仿真来选择调试观察结构以进行硅内仪器。 Paul Cunningham(Cadence 验证总经理)、Raúl Camposano(Silicon Catalyst、企业家、前 Synopsys 首席技术官)和我继续我们的研究想法系列。一如既往,欢迎反馈。

![]()

创新

本月的选择是 用于评估硬件断言以进行流片后验证的仿真基础设施。该论文在 2017 年 IEEE Transactions on VLSI 上发表。作者来自加拿大安大略省汉密尔顿麦克马斯特大学

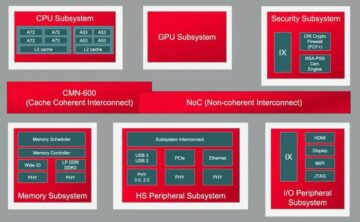

作者区分了硅后逻辑错误和电气错误,并在本文中重点关注可通过触发器中的位翻转来检测的电气错误。他们的方法是在硅前分析中确定一组最佳断言。然后,他们在硅中实现这些,以支持硅后调试。硅前分析类似于安全分析中的故障,在与电气错误相对应的触发器上注入故障,正如论文中所暗示的那样。他们使用断言合成生成候选断言列表;他们创新的核心是提供一种方法,根据每个断言在检测多个故障方面的有效性来对这些断言进行评级。

输入生成是随机的,按顺序分析注入的故障(视为瞬态)。它们允许用户指定的周期数来检测每个故障。在后续阶段,他们使用两种不同的覆盖技术来衡量有效性。对于触发器覆盖率,如果在任何触发器上捕获注入错误,它们就会算作一个断言。在位翻转覆盖范围中,他们对单独触发器上检测到的错误断言数量进行评分。他们(交替地)使用这些指标以及面积估计来选择首选断言。

保罗的观点

这篇论文与我们的 2020 年 XNUMX 月有关快速错误检测的博客 (QED)。 QED 加速硅后功能缺陷检测,本博客重点关注硅后电气缺陷检测。尽管首先阅读参考文献[23]会有所帮助,但这篇论文很容易阅读。

电气错误很难被发现,即使如此,也很难复制并找到潜在的物理原因。作者提出了一种通过嵌入式逻辑来检测此类错误何时导致触发器翻转到错误值的方法(他们不会比找到这些翻转更深入地挖掘)。

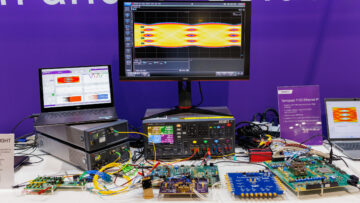

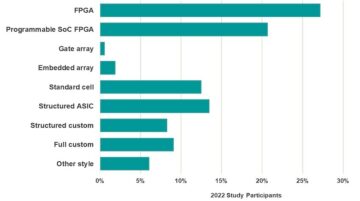

本文及其配套参考文献 [23] 的核心是创建和综合此检测逻辑的多步骤方法。它首先使用挖掘设计的属性作为时间断言 金矿工具。他们根据对检测位翻转的能力的估计以及对在硅中实现的面积/布线成本的估计来对断言进行排名。排名依赖于使用候选断言运行许多硅前模拟、注入位翻转错误并通过断言对检测到的翻转进行计数。在最初的论文中,他们使用了逻辑仿真,在这里,他们通过将设计映射到 Altera FPGA 板来加速这些仿真。

我喜欢他们如何将多项创新整合到一个用于硅后位翻转检测的连贯方法中:断言挖掘、断言合成以及用于断言选择的优雅排名函数。然而,论文的结果部分表明,检测 n% 的触发器中的位翻转需要大约增加 n% 的设计面积。这对于商业应用来说似乎具有挑战性,特别是因为它只能帮助发现电气错误。通过克隆驱动触发器的逻辑锥,然后将该克隆逻辑的输出与原始逻辑进行比较,可能会获得类似的结果。这似乎会产生与他们的方法类似的面积开销,在极限克隆整个设计(即 100100% 面积开销)中检测设计中 XNUMX% 的触发器中的翻转。

劳尔的观点

这篇论文是独立的,包含相当多的细节。作者对 3 个 ISCAS 时序电路(大约 12K 门,2000 FF)进行了实验。准备实验为每个触发器注入 256 个错误,并使用 GoldMine 生成的所有断言。由于 FPGA 的容量有限,作者将一个电路的运行拆分为 45 个“会话”。结果显示,即使有 45 个会话,分析速度也比模拟快 20-500 倍(由于模拟速度太慢,仅注入最多 8 次错误,即 105 小时)。 55 个电路可实现的最大触发器覆盖率为 89%、99% 和 3%。挖掘的断言数量控制覆盖范围。

使用选定的断言(对应于 5-50% 的区域开销)和 1-256 次注入运行会导致 2.2%-34% 的位覆盖率。大多数情况下,断言矿工运行了 228 小时。让我困惑的一件事是他们的运行时数据与注入错误的数据。在模拟中,这种增加看起来是合理的(线性)。但在仿真中,它大幅跃升,从 0.045 小时跃升至 5.4 小时,错误注入增加了 2 到 8 次。我想在这一点上得到更多解释。

这是一篇方法论论文。我喜欢几乎每一步都可以用商业工具代替。结合使用大型 FPGA 板(作为仿真器),该方法可扩展。当然,方法论很难商业化,但它是现有技术的一个很好的应用!

我的观点

探索硅后调试安全分析技术的方法很有趣。这是一个新颖的想法,尽管会导致商业应用有些不切实际的结果。

通过以下方式分享此帖子: 来源:https://semiwiki.com/artificial-intelligence/301350-instrumenting-post-silicon-validation/