在每个芯片中,功耗都是一个需要解决的渐进问题。长期以来,设计人员不得不依靠经验和知识的结合来解决这一困境,通常必须等到芯片可用后才能使用实际的软件工作负载执行功耗分析。然而,这在游戏中为时已晚,因为解决硅后电源问题变得昂贵且耗时。在这篇博文中,我将解释如何尽早在数小时内对十亿门设计实现可操作的功率验证结果。借助此功能,您可以找到峰值功率的关键区域和时间窗口,从而优化您的 RTL 和软件。

在硅后进行功率分析会带来错过关键高功率情况的风险,这可能会造成严重的成本和产品采用问题。对权力的错误认识有什么坏处?如果设计未达到承诺的功耗目标,客户可以选择与其他芯片供应商合作。或者,系统设计人员可能被迫降低芯片性能以维持目标功率范围,这对于依赖快速计算性能的应用来说是不利的权衡。在这篇文章中,最初发表在 “从硅到软件”博客,我们将仔细研究一些 SoC 应用领域,其中准确的功耗分析至关重要。

图形处理器

相比之下,传统 GPU 应用程序是已知的实体,但这并不会让功耗分析任务变得更容易。考虑为笔记本电脑设计的 GPU。您可以在一段时间内在某些测量点运行功率分析。然而,由于时钟周期可能高达 10 万个,这种方法显然并不详尽,这就是为什么设计人员传统上不得不依赖他们对功耗的最佳估计。

人工智能

在人工智能(AI)芯片中,应用程序以及人工智能应用程序和架构的软件堆栈都是新领域,从功耗分析的角度来看,这提出了更多挑战。然而,优化人工智能应用的电力潜在回报是巨大的。毕竟,电源效率和快速计算性能是人工智能芯片设计者希望能够宣传的优势。

5G

另一个对功耗至关重要的应用是 5G,它的核心是高性能和低延迟。 5G 应用涉及大量并行处理和高频,但由于可用功率有限,因此必须对其进行优化才能高效运行。对于无线电头芯片来说尤其如此。

数据中心

数据中心,尤其是超大规模数据中心,建立在闪电般快速、节能的芯片上,有助于最大限度地提高系统总吞吐量。数据中心 SoC 拥有数十亿个门以及复杂的软件工作负载,因此具有特别苛刻的验证和软件启动要求。

联络号码

鉴于其紧凑的外形尺寸和期望的长电池寿命,智能手机等移动设备无法使用功耗过多的芯片。虽然工作负载的复杂性不断增加,但这些设备(甚至是耗电的 GPU)仍然必须能够高效地适应这些工作负载。

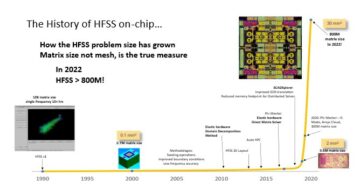

快速功率仿真器如何解决功率分析挑战

随着满足动态功耗要求变得越来越困难,芯片设计人员通常认为功耗是他们面临的首要验证挑战。动态功率验证需要找到峰值功率。然而,关键峰值功率事件是由实际软件工作负载驱动的。仿真可以识别高于或低于功率预算的峰值功率,但在十亿门设计中,它只能靠纯粹的运气捕获真正的关键事件,因为基于仿真的方法可以考虑的窗口太多了。小的。签核工具将提供准确的功率测量,但如果在错误的时间窗口上使用它,设计人员将无法确定哪个窗口具有最高功率。

识别低功耗错误需要运行软件工作负载。小型测试不会暴露实际的工作负载驱动的电源错误。需要的是:

- 硅前测试时的真实固件和操作系统

- 通过仿真验证数百万或数十亿周期的功率

- 用于调试的硅前功率验证,这在实际硅中是不可能实现的

高速仿真使设计团队能够在设计周期的早期执行功耗验证,从而最大限度地降低功耗错误和错过 SoC 功耗目标的风险。事实上,快速功率仿真器可以解决硬件/软件功率验证困境,在更广泛的窗口中提供更好的准确性。理想的模拟器将能够每天在具有实际工作负载的大型设计上运行多次迭代。通过这样做,芯片设计人员可以获得对其设计的功耗概况的可行见解。

数小时内即可获得可行的见解

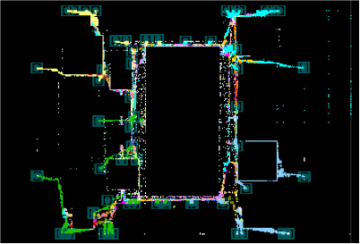

考虑到数十亿门 SoC 工作负载, Synopsys 推出了新的 Synopsys ZeBu® Empower 仿真系统,用于硬件/软件功率验证。提供最大的计算性能, 瘤牛赋能 每天可以执行多次迭代,在数小时内提供可操作的结果。根据生成的功耗曲线,硬件和软件设计人员可以尽早确定可以改善动态和泄漏功耗的领域。 ZeBu Empower 利用 ZeBu服务器 快速仿真硬件技术可提供较短的周转时间。

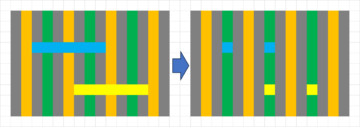

ZeBu Empower 还将功率关键型块和时间窗口反馈到 Synopsys PrimePower 引擎 加速 RTL 功耗分析和门级功耗签核。 ZeBu Empower 和 PrimePower 都是 Synopsys 软件驱动的低功耗解决方案。如下图所示,低功耗解决方案提供了从架构分析到块 RTL 功耗分析再到 SoC 功耗分析和优化的端到端流程和方法。

Synopsys 软件驱动的低功耗解决方案旨在帮助降低 IC 的整体动态和静态功耗。

总结

功耗可能是功耗、性能和面积 (PPA) 方程中最具挑战性的部分。当涉及数十亿门设计时,实现精确功率分布的复杂性只会增加。然而,借助 Synopsys 的快速功率仿真解决方案,设计团队现在可以找到峰值功率的关键区域和时间窗口,从而优化其 RTL 和软件。通过利用全面的 Synopsys 低功耗流程,设计人员可以获得可以帮助他们实现 PPA 目标的工具。考虑到 GPU、AI、5G、数据中心和移动等应用的繁重工作负载和性能需求,任何能够提供更准确功率图的解决方案都应该成为任何设计人员 PPA 工具包中受欢迎的补充。