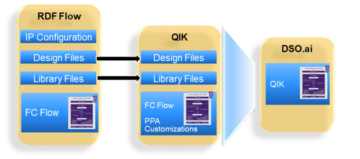

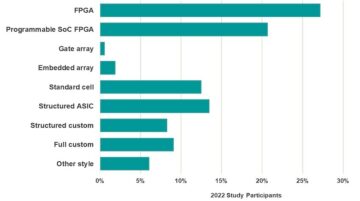

Jeg skrev i sidste måned om fysisk bevidst NoC-design, så du skulle ikke blive overrasket over, at Arteris nu tilbyder netop den mulighed 😊. Først en hurtig opsummering af, hvorfor fysisk bevidsthed er vigtig, især under 16nm. I dag, mellem det øverste niveau og undersystemerne, kan en state-of-art SoC indeholde alt fra fem til tyve NoC'er, hvilket bidrager med 10-12% af siliciumarealet. Interconnect skal tråde gennem hele plantegningen, hvilket øger kompleksiteten i at opfylde PPA-mål i fysisk design. Dette kræver en balancegang mellem NoC-arkitektur, logisk design og fysisk design, en opgave som indtil nu har tvunget manuel iteration, hvilket væsentligt forlænger implementeringsplanen. Denne iteration er et tidsfald, som fysisk bevidst NoC-design sigter mod at skære dramatisk.

(Kilde: Arteris, Inc.)

Det traditionelle sammenkoblingsdesignflow

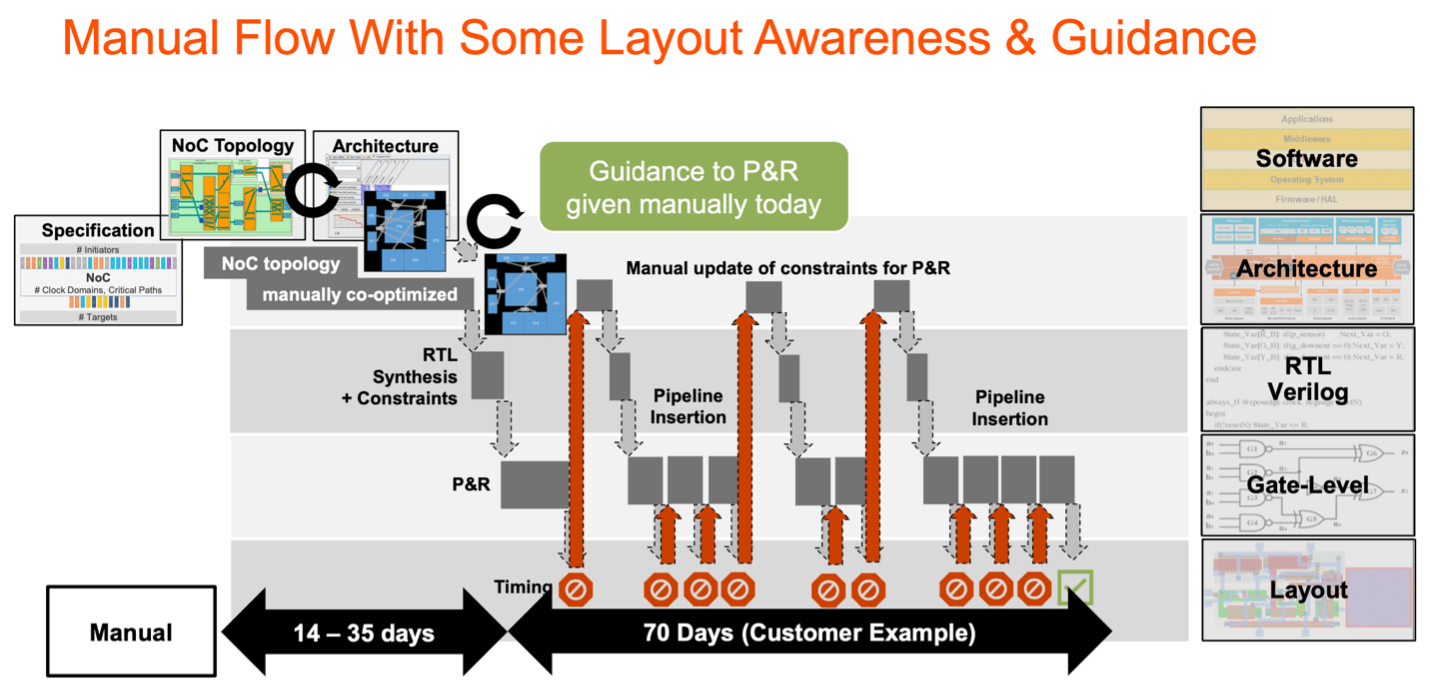

De tidlige stadier af NoC-design er arkitektur-centrerede og finder ud af, hvordan typiske softwarebrugssager bedst kan understøttes. Netværkstopologien bør optimeres omkring servicekvaliteten for stier med høj trafik, samtidig med at den tillader mere fleksibilitet for forbindelser med lavere frekvens og relativt latens-ufølsomme forbindelser. Topologivalg er også påvirket af tidlige plantegningsestimater, emballagebegrænsninger, strømstyringsarkitektur og sikkerheds- og sikkerhedsovervejelser. Arkitekter og NoC-designteams itererer mellem en estimeret plantegning og sammenkoblingstopologi for at konvergere til en omtrentlig arkitektur. Denne planlægningsfase bruger tid (14-35 dage i et produktionsdesigneksempel illustreret her), hvilket er afgørende for tilnærmelsesvis at justere mellem arkitektur, logik og fysiske begrænsninger.

Så begynder det hårde arbejde med at forfine tilnærmelser. Systemverifikation og logisk verifikation køres for at validere båndbredde- og latenstidsmål. Syntese, sted og rute og tidsanalysesonde, hvor designet skal optimeres yderligere for at opfylde effekt-, areal- og timingmål. På dette stadie arbejder designere med en reel fysisk plantegning for alle funktions IP-komponenter, som NoC IP'er og forbindelser skal passe ind i. Uundgåeligt viser tidlige tilnærmelser sig ikke at være helt rigtige, det fysiske designteam kan ikke opfylde timingmålene, og processen skal gentages. Fysiske begrænsninger skal muligvis tunes og pipelines tilføjes, drevet af informeret gætværk. Flere iterationer følger yderligere raffinering af estimater og fører i sidste ende til lukning. Nogle gange kan løsning af et problem kræve en genstart for at refaktorere NoC-topologien, hvilket bringer hele projektet i fare.

Disse iterationer tager tid. I et produktionsdesign tog lukning af NoC-timing 10 uger! Erfarne designteams begrænser iterationer ved over-provision pipelining og ved at bruge LVT-biblioteker langs tidskritiske stier. Accepter afvejninger i areal, latens og kraft i bytte for hurtigere konvergens. Per iteration, at overveje og implementere disse beslutninger, derefter genkøre implementeringsflowet og gentjekke timingen, kan i det hele taget tage uger.

Fysisk bevidst NoC-design med FlexNoC 5

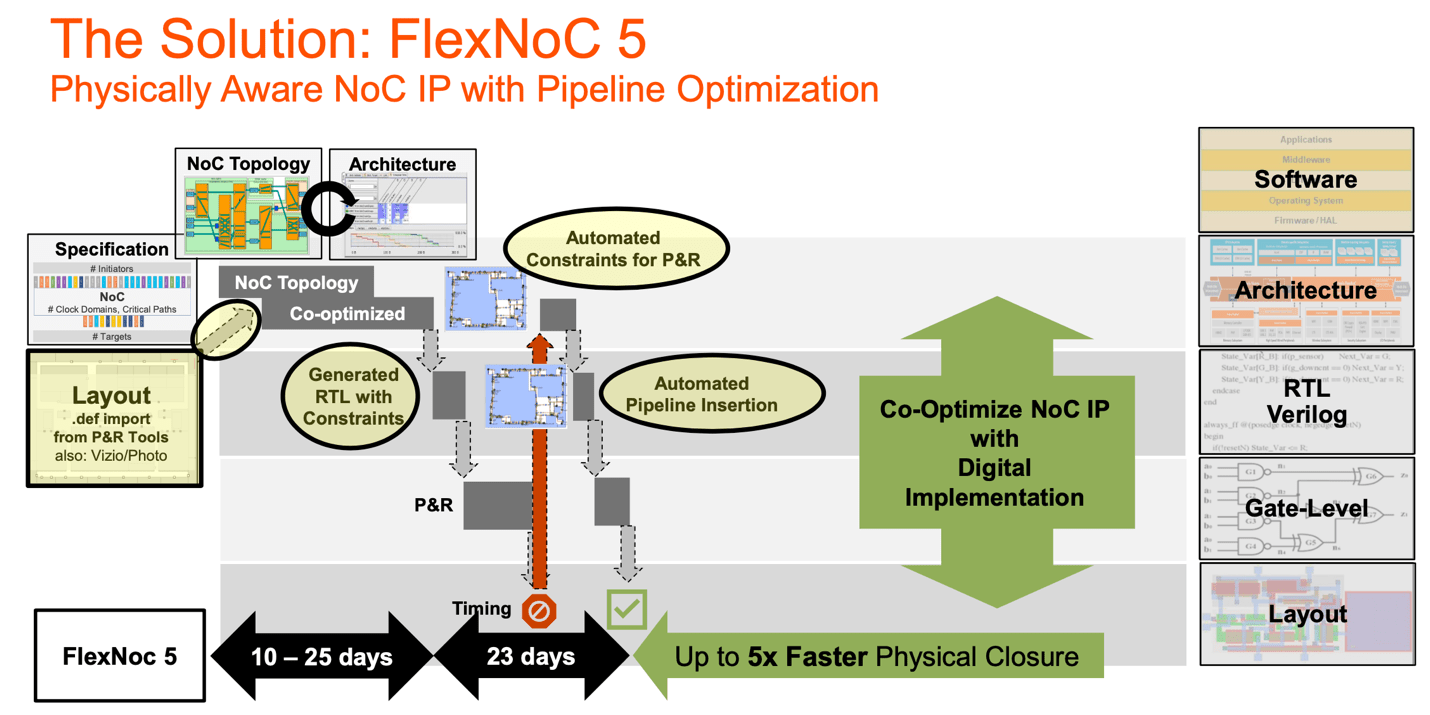

At trial-and-error iteration er en konsekvens af tilnærmelser og antagelser i arkitektonisk design. Forståeligt, men nu er en meget bedre tilgang mulig. Efter den allerførste implementering er en mere præcis plantegning tilgængelig. Måske skal NoC-topologien justeres i forhold til plantegningen, men nu arbejder den med reelle fysiske og tidsmæssige begrænsninger. NoC-generatoren har nok information til at generere mere nøjagtig timing og fysiske begrænsninger for P&R. Det kan også indsætte det rigtige niveau af pipelining, præcis hvor det er nødvendigt. Leverer automatisk en NoC-topologi, som lukkes med tillid med blot endnu et implementeringspas.

(Kilde: Arteris, Inc.)

Dette er, hvad Arteris hævder for deres nye generation FlexNoC 5-løsning – at en første iteration baseret på en gulvplan i implementeringsgrad vil give tilstrækkelig information til, at FlexNoC 5 automatisk kan generere timing og fysiske begrænsninger sammen med pipelining for at imødekomme lukning på den næste passere. Baseret på kundedesigneksemplet beskrevet tidligere, hævder de, at denne automatisering leverer op til en 5X hastighed i iteration til NoC fysisk lukning.

Det er et stort spring i produktiviteten, og det forekommer mig intuitivt fornuftigt. Jeg talte i min tidligere blog om, at hele processen er et optimeringsproblem med alle udfordringerne ved sådanne problemer. En prøve-og-fejl-søgning efter et godt udgangspunkt lider under lange cyklustider gennem implementering, for at afgøre, om et forsøg missede målet, og hvordan man bedst justerer til næste forsøg. Mere automatisering i NoC-generering baseret på mere præcise estimater burde finde et effektivt udgangspunkt hurtigere.

Bevis påstanden

Arteris citerer målte forbedringer i NoC fysisk implementering ved hjælp af et FlexNoC 5 flow, i hvert tilfælde med det samme antal ingeniører med og uden den nye teknologi. Til pipeline-indsættelse var de i stand til at reducere iterationer fra 10 til 1 inden for samme tid pr. iteration. I begrænsning (re-) definition var de i stand til at reducere den forløbne tid fra 3 dage til 1 dag og aktiverer begrænsninger fra 3 til 1. På plads og rute var de i stand til at reducere 5 eller flere iterationer til 1 iteration inden for samme eller bedre iterationstid. Samlet set 10X hurtigere i pipeline-indsættelse, 9X hurtigere i constraint (re-)definition og 5X hurtigere i P&R.

Jeg skal tilføje, at en kunde i dette tilfælde (Sondrel) har betydelig erfaring med ASIC-design og har arbejdet med NoC-teknologi i mange år. Disse er erfarne SoC-designere, der ved, hvordan de optimerer deres manuelle flow, men er enige om, at det nye automatiserede flow leverer bedre resultater hurtigere.

Du kan lære mere om FlexNoC 5 HER og om Arteris HER.

Del dette opslag via:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Kilde: https://semiwiki.com/ip/325116-physically-aware-noc-design-arrives-with-a-big-claim/

- 1

- 10

- a

- I stand

- Om

- acceptere

- præcis

- Lov

- tilføjet

- Efter

- mod

- målsætninger

- Alle

- tillade

- analyse

- ,

- overalt

- tilgang

- cirka

- arkitektonisk

- arkitektur

- OMRÅDE

- omkring

- Ankommer

- ASIC

- Automatiseret

- automatisk

- Automation

- til rådighed

- bevidsthed

- båndbredde

- baseret

- være

- jf. nedenstående

- BEDSTE

- Bedre

- mellem

- Big

- Blog

- tilfælde

- tilfælde

- udfordringer

- valg

- krav

- Luk

- lukning

- lukning

- kompleksitet

- komponenter

- tillid

- Tilslutninger

- overvejelser

- Overvejer

- begrænsninger

- bidrager

- Converge

- Konvergens

- kritisk

- kunde

- Klip

- cyklus

- dag

- Dage

- afgørelser

- leverer

- leverer

- beskrevet

- Design

- designere

- Bestem

- dramatisk

- drevet

- hver

- tidligere

- Tidligt

- Effektiv

- Ingeniører

- nok

- især

- væsentlig

- anslået

- skøn

- præcist nok

- eksempel

- udveksling

- erfaring

- erfarne

- strækker

- hurtigere

- Finde

- Fornavn

- passer

- Fleksibilitet

- Gulvlampe

- flow

- følger

- Frekvens

- fra

- funktion

- yderligere

- generere

- generation

- generator

- Mål

- godt

- klasse

- Hård Ost

- hårdt arbejde

- link.

- Hvordan

- How To

- HTTPS

- implementering

- gennemføre

- vigtigt

- forbedringer

- in

- Inc.

- uundgåeligt

- påvirket

- oplysninger

- informeret

- IP

- IT

- iteration

- iterationer

- hoppe

- bare en

- Kend

- Efternavn

- Latency

- førende

- LÆR

- Niveau

- biblioteker

- GRÆNSE

- logisk

- Lang

- ledelse

- manuel

- mange

- markere

- materielt

- max-bredde

- Mød

- møde

- Måned

- mere

- Behov

- behov

- behov

- netværk

- Ny

- næste

- nummer

- tilbyde

- ONE

- optimering

- Optimer

- optimeret

- samlet

- emballage

- gå igennem

- fase

- fysisk

- Fysisk

- pipeline

- Place

- fly

- planlægning

- plato

- Platon Data Intelligence

- PlatoData

- Punkt

- mulig

- Indlæg

- magt

- sonde

- Problem

- problemer

- behandle

- produktion

- produktivitet

- projekt

- Bevise

- give

- Sætte

- kvalitet

- Hurtig

- ægte

- rimelige

- resumé

- reducere

- Refaktor

- relativt

- kræver

- Kræver

- Resultater

- Risiko

- R

- Kør

- Sikkerhed

- Sikkerhed og sikkerhed

- samme

- planlægge

- Søg

- sikkerhed

- synes

- tjeneste

- bør

- signifikant

- Silicon

- So

- Software

- løsninger

- Kilde

- Stage

- etaper

- Starter

- starter

- sådan

- lider

- Understøttet

- overrasket

- systemet

- Tag

- mål

- Opgaver

- hold

- hold

- Teknologier

- deres

- Gennem

- hele

- tid

- gange

- timing

- til

- i dag

- sammen

- top

- traditionelle

- retssag

- typisk

- Ultimativt

- forståelig

- brug

- VALIDATE

- Verifikation

- via

- uger

- Hvad

- som

- mens

- WHO

- vilje

- inden for

- uden

- Arbejde

- arbejder

- år

- zephyrnet