In elke chip is macht een progressief probleem dat moet worden opgelost. Ontwerpers hebben lang moeten vertrouwen op een combinatie van ervaring en kennis om dit dilemma aan te pakken, waarbij ze doorgaans moesten wachten tot na de beschikbaarheid van silicium om vermogensanalyses uit te voeren met realistische softwareworkloads. Dit is echter te laat in het spel, omdat het een kostbaar en tijdrovend voorstel wordt om energieproblemen na silicium op te lossen. In deze blogpost leg ik uit hoe je in een vroeg stadium bruikbare resultaten voor stroomverificatie kunt bereiken bij ontwerpen met miljard poorten. Met deze mogelijkheid kunt u de kritieke regio's en tijdvensters voor piekvermogen vinden en zo uw RTL en software optimaliseren.

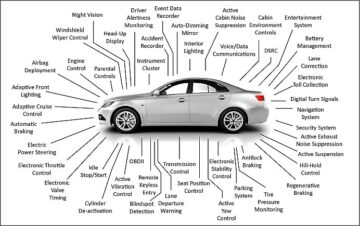

Het uitvoeren van vermogensanalyses na silicium brengt het risico met zich mee dat kritieke situaties met hoog vermogen over het hoofd worden gezien, wat aanzienlijke kosten- en productacceptatieproblemen kan veroorzaken. De nadelen van het verkeerd hebben over macht? Een klant zou ervoor kunnen kiezen om met een andere chipleverancier in zee te gaan als een ontwerp het beloofde vermogensdoel mist. Of een systeemontwerper zou gedwongen kunnen worden de chipprestaties terug te draaien om het beoogde vermogensbereik te behouden – een ongunstige afweging bij toepassingen die afhankelijk zijn van snelle rekenprestaties. In dit bericht, dat oorspronkelijk werd gepubliceerd op de Blog ‘Van silicium tot software’gaan we dieper in op enkele SoC-toepassingsgebieden waar nauwkeurige vermogensanalyse essentieel is.

GPU's

Traditionele GPU-applicaties zijn in vergelijking bekende entiteiten, maar dit maakt de vermogensanalyse-taak er niet eenvoudiger op. Overweeg een GPU die is ontworpen voor een laptopcomputer. U kunt gedurende een bepaalde periode op bepaalde meetpunten een vermogensanalyse uitvoeren. Met potentieel tot 10 miljoen klokcycli is deze benadering echter duidelijk niet uitputtend – en dat is de reden waarom ontwerpers traditioneel moesten vertrouwen op hun beste schattingen voor het vermogen.

Artificial Intelligence

Op het gebied van kunstmatige intelligentie (AI)-chips zijn zowel de applicaties als de softwarestack voor AI-applicaties en -architecturen allemaal nieuw terrein, wat vanuit het perspectief van machtsprofilering meer uitdagingen met zich meebrengt. Toch zijn de potentiële voordelen van het optimaliseren van AI-toepassingen voor macht groot. Energie-efficiëntie is tenslotte een voordeel dat ontwerpers van AI-chips graag zouden willen promoten, samen met snelle rekenprestaties.

5G

Een andere energiekritische toepassing is 5G, waarbij het draait om hoge prestaties en lage latentie. 5G-toepassingen brengen veel parallelle verwerking en hoge frequenties met zich mee, maar omdat er slechts een beperkte hoeveelheid stroom beschikbaar is, moeten ze worden geoptimaliseerd om efficiënt te kunnen werken. Dit geldt met name voor radiokopchips.

data Centers

Datacenters, vooral hyperscale datacenters, zijn gebouwd op bliksemsnelle, energiezuinige chips die de totale systeemdoorvoer kunnen helpen maximaliseren. Met miljarden poorten en complexe softwareworkloads komen SoC's in datacenters met bijzonder veeleisende verificatie- en softwarevereisten.

Mobile

Gezien hun compacte vormfactor en de gewenste lange levensduur van de batterij kunnen mobiele apparaten zoals smartphones het zich niet veroorloven chips te gebruiken die te veel stroom verbruiken. Hoewel hun werklasten steeds complexer zijn geworden, moeten deze apparaten (zelfs de stroomvretende GPU's) nog steeds in staat zijn deze werklasten op een efficiënte manier aan te kunnen.

Hoe een Fast Power-emulator de uitdaging van powerprofilering oplost

Omdat het steeds moeilijker wordt om aan de dynamische stroomvereisten te voldoen, beschouwen chipontwerpers stroom vaak als hun grootste verificatie-uitdaging. Dynamische vermogensverificatie vereist het vinden van piekvermogen. Toch worden kritieke piekvermogensgebeurtenissen veroorzaakt door daadwerkelijke softwareworkloads. Simulatie kan piekvermogen identificeren dat zowel boven als onder het energiebudget valt, maar bij ontwerpen met miljard poorten zal het alleen door puur geluk in staat zijn om de echte kritieke gebeurtenissen op te vangen, omdat de vensters die een op simulatie gebaseerde aanpak kan overwegen veel te groot zijn. klein. Een aftekentool zou nauwkeurige vermogensmetingen opleveren, maar als deze in het verkeerde tijdvenster wordt gebruikt, zou de ontwerper niet kunnen bepalen welk venster het hoogste vermogen heeft.

Voor het identificeren van bugs met een laag energieverbruik is het uitvoeren van softwareworkloads vereist. Kleine tests zullen geen realistische, door de werklast veroorzaakte powerbugs blootleggen. Wat nodig is, is:

- Echte firmware en besturingssysteem tijdens pre-siliciumtests

- Emulatie om de macht over miljoenen of miljarden cycli te verifiëren

- Pre-silicium vermogensverificatie voor debuggen, wat niet mogelijk is met echt silicium

Door de snelle emulatie kunnen ontwerpteams de stroomverificatie eerder in de ontwerpcyclus uitvoeren, zodat ze de risico's op stroombugs en gemiste SoC-stroomdoelen kunnen minimaliseren. Een snelle energie-emulator kan inderdaad het antwoord zijn op het hardware-/software-dilemma voor stroomverificatie, en zorgt voor een betere nauwkeurigheid over een breder venster. De ideale emulator zou meerdere iteraties per dag kunnen uitvoeren op grote ontwerpen met realistische werklasten. Door dit te doen kunnen chipontwerpers bruikbare inzichten verkrijgen in het krachtprofiel van hun ontwerpen.

Bruikbare inzichten in uren

Met SoC-workloads met meerdere miljardenpoorten in gedachten, Synopsys heeft zijn nieuwe Synopsys ZeBu® Empower-emulatiesysteem voor hardware-/softwarestroomverificatie onthuld. Maximale computerprestaties leveren, ZeBu-empower kan meerdere iteraties per dag uitvoeren en binnen enkele uren bruikbare resultaten opleveren. Op basis van de resulterende energieprofielen kunnen hardware- en softwareontwerpers in een vroeg stadium gebieden identificeren waar ze de dynamische energie en het lekvermogen kunnen verbeteren. ZeBu Empower maakt gebruik van ZeBu-server snelle emulatiehardwaretechnologie om korte doorlooptijden te bieden.

ZeBu Empower stuurt ook energiekritische blokken en tijdvensters door naar de Synopsys PrimePower-motor om de RTL-vermogensanalyse en de vermogensafgifte op poortniveau te versnellen. Zowel ZeBu Empower als PrimePower maken deel uit van de Synopsys softwaregestuurde energiezuinige oplossing. In het onderstaande diagram ziet u dat de energiezuinige oplossing een end-to-end stroom en methodologie biedt, variërend van architectuuranalyse tot het blokkeren van RTL-vermogensanalyse tot SoC-vermogensanalyse en -optimalisatie.

De softwaregestuurde energiezuinige oplossing van Synopsys is ontworpen om het algehele dynamische en statische stroomverbruik van IC's te helpen verminderen.

Samengevat

Macht is misschien wel het meest uitdagende onderdeel van de vergelijking tussen macht, prestatie en oppervlakte (PPA). En als het gaat om ontwerpen met meerdere miljarden poorten, wordt de complexiteit bij het realiseren van nauwkeurige vermogensprofielen alleen maar groter. Met de snelle stroomemulatieoplossing van Synopsys kunnen ontwerpteams nu echter de kritieke regio's en tijdvensters voor piekvermogen vinden, zodat ze hun RTL en hun software kunnen optimaliseren. Door te profiteren van de uitgebreide Synopsys low-power flow krijgen ontwerpers tools waarmee ze hun PPA-doelen kunnen bereiken. Gezien de zware werklast en prestatie-eisen van applicaties zoals GPU's, AI, 5G, datacenters en mobiele apparaten, zou elke oplossing die een nauwkeuriger vermogensbeeld kan bieden een welkome aanvulling moeten zijn op de PPA-toolkit van elke ontwerper.

Deel dit bericht via: Bron: https://semiwiki.com/eda/synopsys/301320-optimize-rtl-and-software-with-fast-power-verification-results-for-billion-gate-designs/

- 5G

- Adoptie

- Voordeel

- AI

- Alles

- analyse

- Aanvraag

- toepassingen

- architectuur

- GEBIED

- kunstmatige intelligentie

- Kunstmatige intelligentie (AI)

- beschikbaarheid

- Accu

- BEST

- Blog

- bugs

- het worstelen

- uitdagen

- spaander

- chips

- dichterbij

- Berekenen

- consumeren

- consumptie

- gegevens

- Data Center

- datacenters

- dag

- het leveren van

- Design

- leesmaatjes

- systemen

- gedreven

- Vroeg

- doeltreffendheid

- machtigen

- schattingen

- EVENTS

- SNELLE

- stroom

- formulier

- Naar voren

- spel

- Gates

- GPU

- GPU's

- groot

- Hardware

- hoofd

- Hoge

- Hoe

- HTTPS

- ICS

- identificeren

- inzichten

- Intelligentie

- problemen

- IT

- kennis

- laptop

- Groot

- lang

- liefde

- miljoen

- Mobile

- mobiele toestellen

- werkzaam

- besturingssysteem

- prestatie

- perspectief

- beeld

- energie

- Product

- Profiel

- Profielen

- Radio

- verminderen

- Voorwaarden

- Resultaten

- Beloningen

- Risico

- lopen

- lopend

- Bermuda's

- simulatie

- Klein

- smartphones

- So

- Software

- system

- doelwit

- Technologie

- testen

- niet de tijd of

- top

- Verificatie

- wachten

- ruiten