U.S. strategy on microelectronics; standard cell layout automation; penning micro-trap for quantum; TCAM-SSD; predicting warpage early in package design; open HW in quantum; van der Waals heterojunctions; cleaner semi manufacturing.

New technical papers recently added to Semiconductor Engineering’s library.

| Technical Paper | Research Organizations |

|---|---|

| National Strategy on Microelectronics Research | White House Office of Science and Technology Policy (OSTP) |

| Novel Transformer Model Based Clustering Method for Standard Cell Design Automation | Nvidia |

| Penning micro-trap for quantum computing | ETH Zürich, Leibniz Universität Hannover, and Physikalisch-Technische Bundesanstalt |

| Cleaner Chips: Decarbonization in Semiconductor Manufacturing | Oak Ridge National Laboratory (ORNL) / UT-Battelle |

| TCAM-SSD: A Framework for Search-Based Computing in Solid-State Drives | University of Illinois Urbana-Champaign, Carnegie Mellon University, Samsung Electronics and Sandia National Laboratories |

| Warpage Study by Employing an Advanced Simulation Methodology for Assessing Chip Package Interaction Effects | Siemens EDA, D2S, and Univ. Grenoble Alpes, CEA, Leti |

| Electrical characterization of multi-gated WSe2 /MoS2 van der Waals heterojunctions | Helmholtz-Zentrum Dresden Rossendorf (HZDR), TU Dresden, National Institute for Materials Science (Japan) and NaMLab gGmbH |

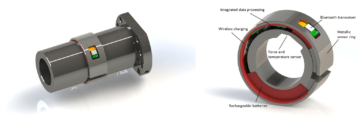

| Open Hardware Solutions in Quantum Technology | Unitary Fund, Qruise GmbH, Technical University of Valencia, Lawrence Berkeley National Laboratory, Fermi National Accelerator Laboratory, Sandia National Labs, and others |

Find last week’s technical paper additions here.

Linda Christensen

Linda Christensen is vice president of operations and a contributing writer at Semiconductor Engineering.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiengineering.com/chip-industry-technical-paper-roundup-mar-26/

- :is

- 1

- 10

- 22

- 26

- 28

- 29

- 30

- 5

- 6

- 7

- 8

- 80

- 9

- a

- accelerator

- added

- additions

- advanced

- All

- All Posts

- alternative

- an

- and

- Assessing

- At

- Automation

- based

- Berkeley

- by

- Carnegie Mellon

- Carnegie mellon university

- cell

- chip

- Chips

- Christensen

- cleaner

- clustering

- computing

- contributing

- decarbonization

- Design

- Early

- Electronics

- employing

- Engineering

- Even

- For

- Framework

- fund

- GmBH

- Hardware

- House

- HTTPS

- illinois

- in

- industry

- Institute

- interaction

- Japan

- laboratory

- Labs

- Last

- lawrence

- Layout

- manufacturing

- March

- materials

- Mellon

- method

- Methodology

- model

- National

- of

- Office

- on

- open

- Operations

- ORNL

- OSTP

- package

- Paper

- papers

- plato

- Plato Data Intelligence

- PlatoData

- policy

- popularity

- Posts

- pr

- predicting

- president

- Quantum

- recently

- roundup

- ROW

- s

- Samsung

- Science

- Science and Technology

- Semi

- semiconductor

- simulation

- Solutions

- standard

- Strategy

- Study

- Technical

- Technology

- text

- thumbnail

- to

- transformer

- university

- van

- vice

- Vice President

- writer

- zephyrnet

More from Semi Engineering

Everyone’s A System Designer With Heterogeneous Integration

Source Node: 2304484

Time Stamp: Oct 2, 2023

Why The SOAFEE Project Is Integral For The Design Of Connected Vehicles

Source Node: 2260688

Time Stamp: Sep 7, 2023

Big Changes Ahead In Power Delivery, Materials, And Interconnects

Source Node: 2025173

Time Stamp: Mar 22, 2023

Overcoming Signal Integrity Challenges Of 112G Connections

Source Node: 2513891

Time Stamp: Mar 13, 2024

How Quickly Will Multi-Die Systems Change Semiconductor Design?

Source Node: 2307814

Time Stamp: Oct 4, 2023

A Chiplet-Based Fully Homomorphic Encryption Accelerator

Source Node: 2222028

Time Stamp: Aug 18, 2023

Hardware Trojans: CPU-Oriented Trojan Trigger Circuits (Georgia Tech)

Source Node: 2522856

Time Stamp: Mar 22, 2024