When you think “FPGA,” what comes to mind? Massive, expensive parts capable of holding a lot of logic but also consuming a lot of power. Reconfigurable platforms that can swallow RTL for an SoC design in pre-silicon testing. Big splashy corporate acquisitions where investors made tons of money. Exotic 3D packaging and advanced interconnects. But probably not inexpensive, small package, low pin count, low standby power parts, right? Flex Logix’s eFPGA goes back to basics for low-power programmable logic that can take on lower cost, higher volume, and size-constrained devices.

Two programmable roads presented a choice

At the risk of dating myself, my first exposure to what was then called FPGA technology was back when Altera brought out their EPROM-based EP1200 family in a 40-pin DIP package with its 16 MHz clock, 400 mW active power and 15 mW standby power. It came with a schematic editor and a library of gate macros. Designers would draw their logic, “burn” their part, test it out, throw it under a UV lamp and erase it if it didn’t work, and try again.

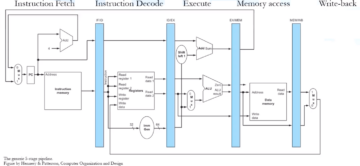

Soon after, a board showed up in another of our labs with some of the first Xilinx FPGAs. These were RAM-based instead of EPROM-based – bigger, faster, and reprogramming without the UV lamp wait or removing the part from the board. The logic inside was also more complex, with the introduction of fast multipliers. These parts could not only sweep up logic but could also be used to explore custom digital signal processing capability with rapid redesign cycles.

That set off the programmable silicon arms race, and a bifurcation developed between the PLD – programmable logic device – and the FPGA. Manufacturers made choices, with Altera and Xilinx taking the high road of FPGA scalability and Actel, Lattice, and others taking the lower road of PLD flexibility for “glue logic” to reduce bill-of-materials costs.

eFPGA shifts the low-power programmable logic equation

All that sounds like a mature market, with a high barrier to entry on one end and a more commoditized offering on the other. But what if programmable logic was an IP block that could be designed into any chip in this fabless era – including a small, low-power FPGA? That would circumvent the barrier (at least in the low and mid-range offerings) and commoditization.

Flex Logix took on that challenge with the EFLX 1K eFPGA Tile. Each logic tile has 560 six-input look-up tables (LUTs) with RAM, clocking, and interconnect. Arraying EFLX tiles gives the ability to handle various logic and DSP roles. But its most prominent features may be its size and power management.

Fabbed in TSMC 40ULP, the EFLX 1K tile fits in 1.5mm2 and offers power-gating for deep sleep modes with state retention – much more aggressive than traditional PLDs. EFLX 1K also has production-ready features borrowed from FPGAs. It presents AXI or JTAG interfaces for bitstream configuration, readback circuitry enabling soft error checking, and a test mode with streamlined vectors improving coverage and lowering test times.

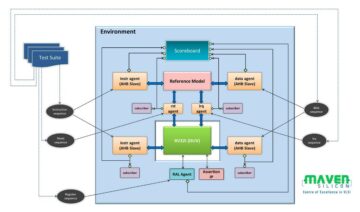

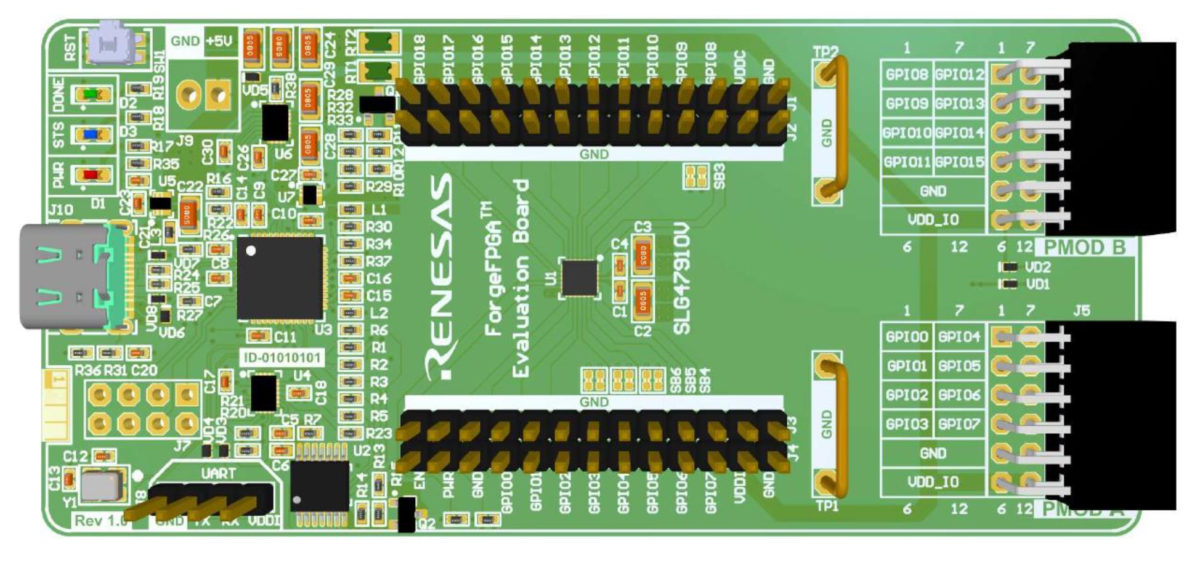

See the chip in the center of this next image? That’s a ForgeFPGA from Renesas in a QFN-24 package, based on EFLX 1K IP, which Renesas offers at sub-$1 price points in volume. Its standby target current checks in at less than 20uA. Smaller size, lower cost, and less power open doors previously closed to FPGAs. The lineage of ForgeFPGA traces back to Silego Technology, then to Dialog Semiconductor, acquired by Renesas in 2021.

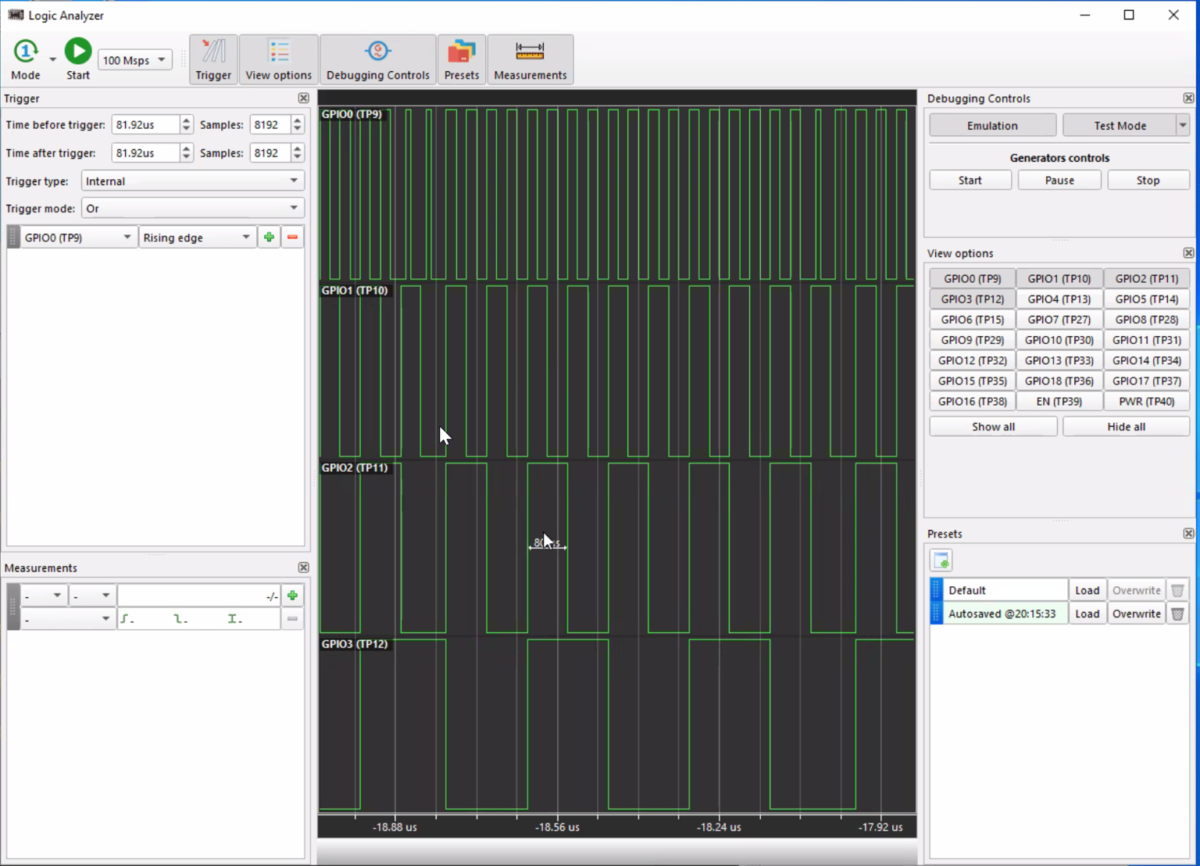

Renesas brings the Go Configure IDE environment, putting a graphical user interface on top of the Flex Logix EFLX compiler. It supports mapping ForgeFPGA pins, compiling Verilog, generating a bitstream, and has a lightweight logic analyzer.

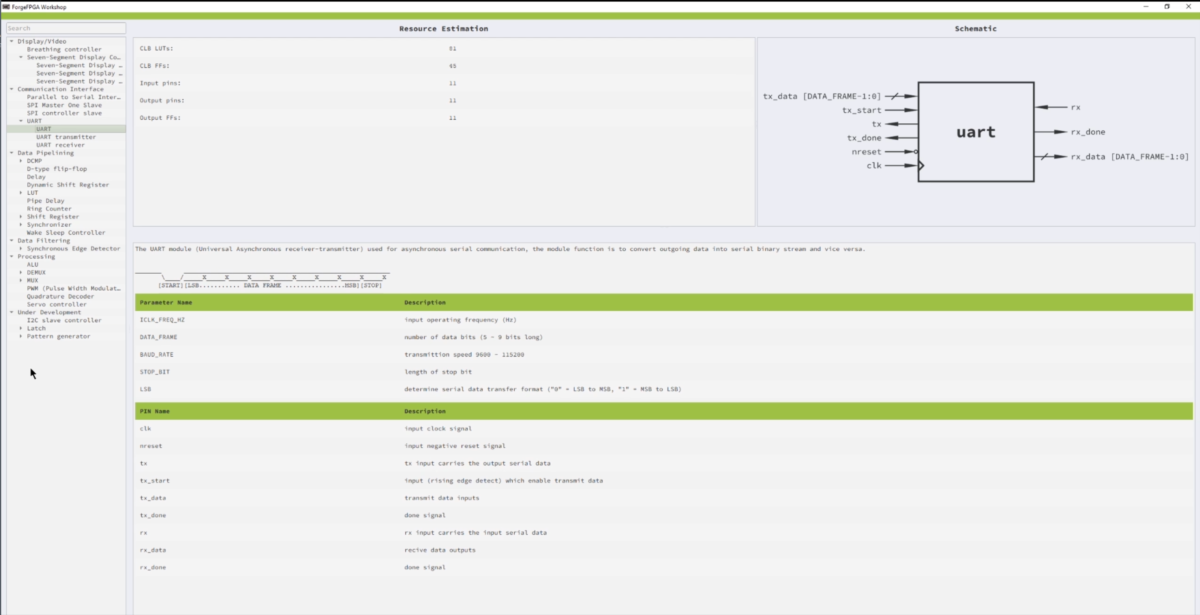

The pre-built application blocks for the ForgeFPGA have an interesting one that Flex Logix’s Geoff Tate points out: a UART. Creating a UART in logic isn’t all that difficult, but it turns out that everyone has gone about it differently, and it’s just enough logic to be more than a couple of discrete chips. A ForgeFPGA is a chunk of reconfigurable logic that can solve that problem, allowing one hardware implementation to adapt quickly for various configurations.

ForgeFPGA is just one example of what can be done with the Flex Logix EFLX 1K eFPGA Tile. Flex Logix can adapt the IP for various process nodes, and the mix-and-match tiling capability offers scalability. It achieves new lows for low-power programmable logic and allows chip makers to differentiate solutions in remarkable ways. For more info, please visit:

Also Read:

eFPGAs handling crypto-agility for SoCs with PQC

Flex Logix: Industry’s First AI Integrated Mini-ITX based System

Flex Logix Partners With Intrinsic ID To Secure eFPGA Platform

Share this post via:

- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Source: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :is

- $UP

- 1

- 2021

- 3d

- a

- ability

- About

- about IT

- Achieves

- acquired

- acquisitions

- active

- adapt

- advanced

- After

- aggressive

- AI

- All

- Allowing

- allows

- and

- Another

- Application

- At

- back

- barrier

- based

- Basics

- BE

- between

- Big

- bigger

- Block

- Blocks

- board

- borrowed

- Brings

- brought

- by

- called

- CAN

- capable

- Center

- challenge

- checking

- Checks

- chip

- Chips

- choices

- Clock

- closed

- complex

- Configuration

- configurations

- Corporate

- Cost

- Costs

- could

- Couple

- coverage

- Creating

- Current

- custom

- cycles

- Dating

- deep

- Design

- designed

- designers

- developed

- device

- Devices

- dialog

- differentiate

- difficult

- digital

- Dip

- doors

- each

- editor

- enabling

- enough

- entry

- Environment

- Era

- error

- evaluation

- everyone

- example

- Exotic

- expensive

- explore

- Exposure

- family

- FAST

- faster

- Features

- First

- Flexibility

- For

- fpga

- from

- generating

- gives

- Go

- Goes

- handle

- Handling

- Hardware

- Have

- High

- higher

- holding

- HTTPS

- ID

- image

- implementation

- improving

- in

- Including

- industry’s

- inexpensive

- info

- instead

- integrated

- interesting

- Interface

- interfaces

- intrinsic

- Introduction

- Investors

- IP

- IT

- ITS

- jpg

- just one

- Labs

- Library

- lightweight

- like

- Lot

- Low

- lowering

- Lows

- Macro

- macros

- made

- Makers

- management

- Manufacturers

- mapping

- Market

- massive

- mature

- max-width

- mind

- Mode

- modes

- money

- more

- most

- New

- next

- nodes

- of

- offering

- Offerings

- Offers

- on

- ONE

- open

- Other

- Others

- package

- packaging

- part

- partners

- parts

- PIN

- pins

- Platforms

- plato

- Plato Data Intelligence

- PlatoData

- please

- points

- Post

- power

- presented

- presents

- previously

- price

- probably

- Problem

- process

- processing

- prominent

- Putting

- quickly

- Race

- RAM

- rapid

- Read

- redesign

- reduce

- remarkable

- removing

- retention

- Risk

- road

- roads

- roles

- Scalability

- secure

- semiconductor

- set

- Shifts

- Signal

- Silicon

- Size

- sleep

- small

- smaller

- Soft

- Solutions

- SOLVE

- some

- State

- streamlined

- Supports

- Sweep

- Take

- taking

- Target

- Technology

- test

- Testing

- that

- The

- their

- These

- Think

- times

- to

- tons

- top

- traditional

- Tsmc

- under

- User

- User Interface

- various

- via

- Visit

- volume

- wait

- ways

- What

- which

- with

- without

- Work

- would

- zephyrnet