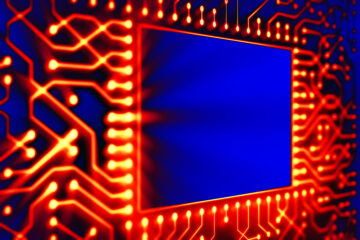

Delivering unrivaled memory bandwidth in a compact, high-capacity footprint, has made HBM the memory of choice for AI training. HBM3 is the third major generation of the HBM standard, with HBM3E offering an extended data rate and the same feature set. The Rambus HBM3E/3 Controller provides industry-leading performance to 9.6 Gb/s, enabling a memory throughput of over 1.23 TB/s for training recommender systems, generative AI and other compute-intensive AI workloads.

Download this white paper to:

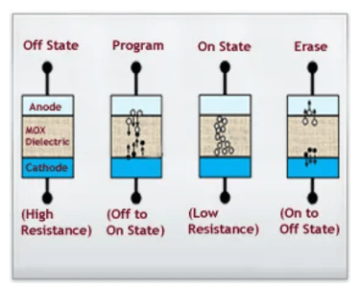

- Read about the HBM architecture

- Discover the performance enhancements offered by HBM3E

- Discover the features of the Rambus HBM3E/3 Memory Controller cores

Click here to read more.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiengineering.com/hbm3e-memory-break-through-to-greater-bandwidth/

- :has

- :is

- 1

- 23

- 6

- 9

- a

- About

- AI

- AI training

- an

- and

- Bandwidth

- Break

- by

- choice

- compact

- controller

- data

- enabling

- enhancements

- extended

- Feature

- Features

- Footprint

- For

- generation

- generative

- Generative AI

- greater

- HTTPS

- in

- industry-leading

- jpg

- made

- major

- Memory

- more

- of

- offered

- offering

- Other

- over

- Paper

- performance

- plato

- Plato Data Intelligence

- PlatoData

- provides

- Rate

- Read

- same

- set

- standard

- Systems

- The

- Third

- this

- Through

- throughput

- to

- Training

- unrivaled

- white

- white paper

- with

- zephyrnet

More from Semi Engineering

Large-Scale Integration Of 2D Materials As The Semiconducting Channel In An In-Memory Processor (EPFL)

Source Node: 2426286

Time Stamp: Jan 3, 2024

Complex Safety Mechanisms Require Interoperability And Automation For Validation And Metric Closure

Source Node: 2506344

Time Stamp: Mar 6, 2024

FPGA-Based HW/SW Platform For Pre-Silicon Emulation Of RISC-V Designs (Barcelona Supercomputing Center)

Source Node: 2484760

Time Stamp: Feb 15, 2024

Fixed-Point And Floating-Point FMCW Radar Signal Processing With Tensilica DSPs

Source Node: 1917931

Time Stamp: Jan 25, 2023

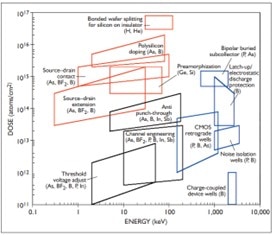

Ion Implantation Applications For In-Line SIMS Metrology

Source Node: 1955591

Time Stamp: Feb 13, 2023

3D-IC: Operator Learning Framework For Ultra-Fast 3D Chip Thermal Prediction Under Multiple Chip Design Configurations

Source Node: 2030005

Time Stamp: Mar 24, 2023

An Open-Source Solution To Accelerate Autonomous Vehicle Validation And Verification Research

Source Node: 2240854

Time Stamp: Aug 28, 2023