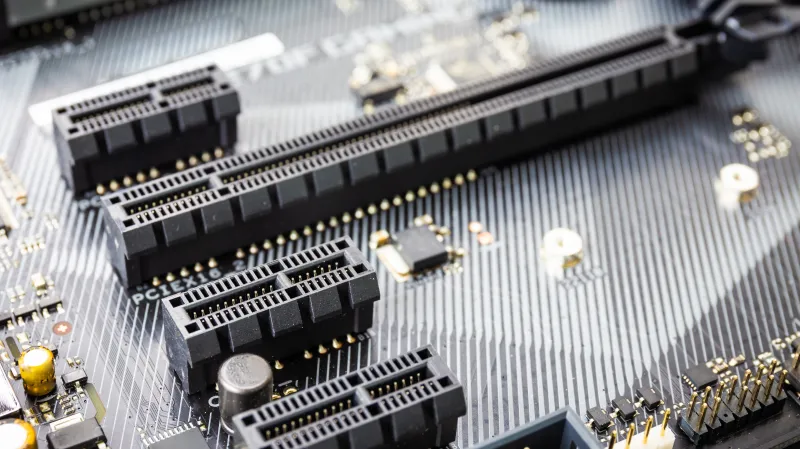

With most expansion busses for computers, you are limited to one device in one slot. But PCIe, used in modern computers and slated for the Raspberry Pi 5, have some interesting characteristics in comparison. First, some terminology, via Wikipedia:

Conceptually, the PCI Express bus is a high-speed serial replacement of the older PCI/PCI-X bus. One of the key differences between the PCI Express bus and the older PCI is the bus topology; PCI uses a shared parallel bus architecture, in which the PCI host and all devices share a common set of address, data, and control lines. In contrast, PCI Express is based on point-to-point topology, with separate serial links connecting every device to the root complex (host).

A PCI Express bus link supports full-duplex communication between any two endpoints, with no inherent limitation on concurrent access across multiple endpoints.

In terms of bus protocol, PCI Express communication is encapsulated in packets. The work of packetizing and de-packetizing data and status-message traffic is handled by the transaction layer of the PCI Express port.

The PCI Express link between two devices can vary in size from one to 16 lanes. In a multi-lane link, the packet data is striped across lanes, and peak data throughput scales with the overall link width. The lane count is automatically negotiated during device initialization and can be restricted by either endpoint. For example, a single-lane PCI Express (x1) card can be inserted into a multi-lane slot (x4, x8, etc.), and the initialization cycle auto-negotiates the highest mutually supported lane count.

The link can dynamically down-configure itself to use fewer lanes, providing a failure tolerance in case bad or unreliable lanes are present. The PCI Express standard defines link widths of x1, x2, x4, x8, and x16.

Interconnect

PCI Express devices communicate via a logical connection called an interconnect or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts. At the physical level, a link is composed of one or more lanes. Low-speed peripherals (such as an 802.11 Wi-Fi card) use a single-lane (x1) link, while a graphics adapter typically uses a much wider and therefore faster 16-lane (x16) link.

Lane

A lane is composed of two differential signaling pairs, with one pair for receiving data and the other for transmitting. Thus, each lane is composed of four wires or signal traces. Conceptually, each lane is used as a full-duplex byte stream, transporting data packets in eight-bit “byte” format simultaneously in both directions between endpoints of a link.

Serial bus

The bonded serial bus architecture was chosen over the traditional parallel bus because of the inherent limitations of the latter.

For more, see Wikipedia.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://blog.adafruit.com/2023/10/04/pcie-pci-express-what-it-is-and-terminology/

- :is

- 1

- 220

- 247

- 361

- a

- access

- across

- address

- All

- Allowing

- Anchor

- and

- any

- architecture

- ARE

- AS

- At

- automatically

- Bad

- based

- BE

- because

- between

- both

- bus

- but

- by

- called

- CAN

- card

- case

- Channel

- channels

- characteristics

- chosen

- Common

- communicate

- Communication

- comparison

- complex

- composed

- computers

- Conceptually

- concurrent

- Configuration

- Connecting

- connection

- consists

- contrast

- control

- cycle

- data

- Defines

- device

- Devices

- differences

- during

- dynamically

- each

- either

- encapsulated

- Endpoint

- endpoints

- etc

- Every

- example

- expansion

- express

- Failure

- faster

- fewer

- First

- For

- format

- four

- from

- graphics

- handled

- Have

- High

- highest

- host

- HTTPS

- in

- inherent

- interesting

- into

- IT

- itself

- Key

- Lane

- layer

- Level

- limitation

- limitations

- Limited

- lines

- LINK

- links

- logical

- max-width

- Memory

- Modern

- more

- most

- much

- multiple

- mutually

- negotiated

- no

- of

- older

- on

- ONE

- or

- ordinary

- Other

- over

- overall

- packets

- pair

- pairs

- Parallel

- Peak

- peripherals

- physical

- plato

- Plato Data Intelligence

- PlatoData

- ports

- present

- protocol

- providing

- Raspberry

- Raspberry Pi

- receive

- receiving

- reference

- replacement

- requests

- restricted

- root

- scales

- see

- send

- set

- Share

- Signal

- Simplex

- simultaneously

- Size

- slot

- some

- standard

- stream

- such

- Supported

- Supports

- SVG

- terminology

- terms

- The

- Them

- therefore

- throughput

- Thus

- to

- tolerance

- traditional

- traffic

- transaction

- transporting

- two

- typically

- use

- used

- uses

- using

- vary

- via

- was

- What

- which

- while

- wider

- Wikipedia

- with

- Work

- x8

- you

- zephyrnet