While writing last month’s blog that used some of the trend charts we have seen, I noticed that a lot of the data ends in 2020 or earlier, but I was too close to the deadline to sit down and make orderly updates to some of the charts. Working day-to-day in the area of SoC integration and networks-on-chips (NoCs), the classic chart based on Karl Rupp’s now 50 years of processor data that overlays the Moore’s law transistors with single-thread performance, processor frequency, typical power, and the number of processor cores is relevant, but not quite perfect. Yes, processor cores are essential, but there are many other types of silicon IP blocks (SIP) to be connected using NoCs and integrated using what we at Arteris call “SoC Integration Automation.”

So, I looked for the relevant source data and developed some new visualizations.

NoC protocol complexity

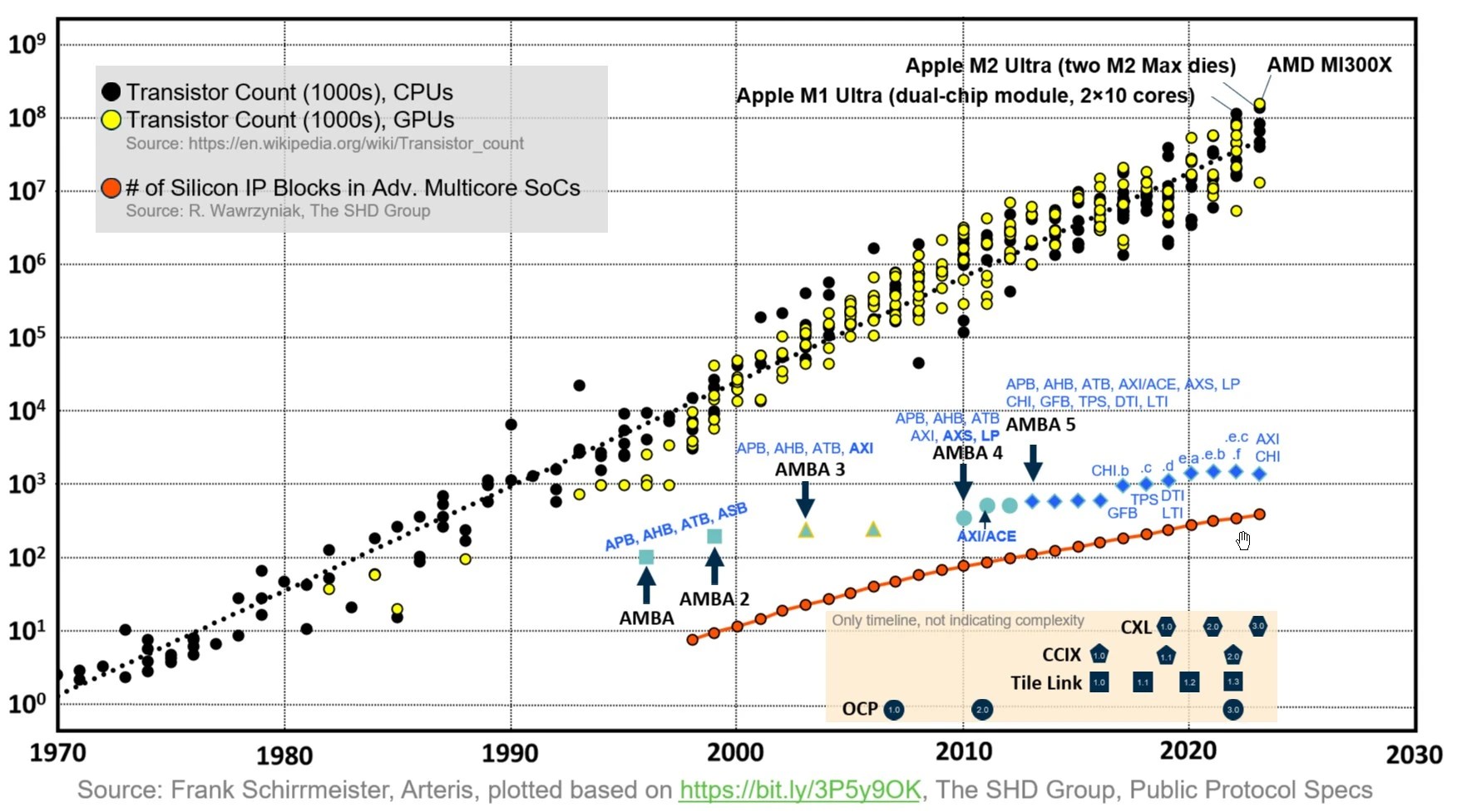

First, let’s look at NoCs in the context of complexity. The chart below shows the evolution of transistor complexity as outlined on the Transistor Wikipedia page. I separated CPUs and GPUs; the latter is kicking in in the mid-1990s in earnest. Unsurprisingly, this part of the chart shows Moore’s law without considering transistor cost, which I plan to overlay in a future version.

The red data points are the number of SIP blocks, with permission from Richard Wawrzyniak at The SHD Group. We are arriving at about 400 SIP blocks for Advanced Multicore SoCs in 2023. Note that this is on a logarithmic scale, so in the early 2000s, the industry was in the lower two digits for the number of SIP blocks, and the number was growing fast.

![]()

Fig. 1: Transistor and network-on-chip (NoC) complexity over time.

All these SIP blocks need to talk to each other, which spawned the development of protocols for NoCs. The most prominent protocol is the Advanced Microcontroller Bus Architecture (AMBA). It is a freely available, open standard to connect and manage functional blocks and charted with its complexity as measured in the number of pages. The first version of AMBA, released in 1996, included two buses, the Advanced System Bus (ASB) and Advanced Peripheral Bus (APB), and had 106 pages. The second version, released in 1999, added the AMBA High-performance Bus (AHB), a single clock-edge protocol. The spec had 204 pages.

The third version of AMBA was released in 2003 and introduced the AMBA Advanced eXtensible Interface (AXI), a high-performance, multi-channel protocol. The total number of pages grew to 260 pages in 2006. AMBA 4 was released in 2010 and added the AMBA AXI Coherency Extensions (ACE) and AMBA Low-power Interface (LPI) protocols, which enable cache coherency and power management. The specs grew to a total of 534 pages in 2012.

AMBA 5, the latest version, released in 2013, introduced the AMBA Coherent Hub Interface (CHI) architecture, which defines the interfaces to connect fully coherent processors and high-performance interconnects. It also extended the prior protocols to support new features such as quality of service and atomic operations. By 2023, the total page count of AMBA 5 related specs has grown to 1398, with various versions of CHI and specification of Adaptive Traffic Profiles (marked at ATP), a Generic Flash Bus Protocol (GFP), a Distributed Translation Interface (DTI) and a Local Translation Interface (LTI), defining the point-to-point protocol between an I/O device and the Translation Lookaside Buffer Unit (TLBU) of an Arm System Memory Management Unit (SMMU).

By the way, thanks to Arm’s Francisco Socal for his input on this project. He warned me that the AMBA complexity would drop slightly in 2003 due to the recent introduction of AXI-J. It significantly simplifies the document by removing legacy content and AXI5 now has a generic interface that can be configured as ACE5-Lite, ACE5-LiteDVM, and AXI5-Lite.

If you have, at this point, like me, the “TLA and FLA Blues” (three and four-letter acronyms), then it becomes clear that NoCs for AMBA require particular expertise. That’s where we at Arteris are coming in with our FlexNoC and NCore IP for non-coherent and coherent protocols.

But wait, there is more.

The bottom right of the chart above shows the timeline of the introduction of four other related protocols:

- The Open Core Protocol (OCP) is a standard for on-chip interconnects. It was first introduced in 2007 by the SPIRIT Consortium. The latest version, OCP 3.0, was released in 2022.

- The TileLink NoC protocol is a standard for on-chip interconnects focused on RISC-V. It was first introduced in 2016 by the RISC-V Foundation. The latest version, TileLink 1.3, was released in 2022.

- The Cache Coherent Interconnect for Accelerators (CCIX) is a high-speed interconnect standard for connecting processors, memory, and accelerators, first introduced in 2016.

- The Compute Express Link (CXL) is a high-speed interconnect standard for connecting processors, memory, and accelerators, first introduced in 2019.

The chart only shows the complexity of these protocols as the number of pages, only the timelines, hence they are called out in a different block.

Bottom line: It’s a complex world of NoCs, and they are critical to enabling complex SoCs and, more and more, chiplet-based designs.

SoC integration complexity

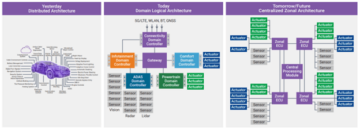

Well, now you have many commercial SIP blocks and all your differentiating blocks. Where to go from here? SoC integration automation is the answer. The chart below shows how the industry has and still is reacting to the growing complexity and number of SIP blocks over time:

![]()

Fig. 2: Transistor and SoC integration complexity over time.

This chart repeats the transistor complexity and number of SIP blocks described above. But now it overlays the attempts and standards that deal with the SoC assembly, i.e., the management of the sea of RTL blocks, both commercially acquired and developed internally. IP-XACT is the critical term to remember here.

As charted, the VSI Alliance was an organization founded in 1996 to enhance the productivity of the SoC design community by providing standards and solutions for IP reuse. The SPIRIT Consortium was another organization founded in 2003 to develop and specify the IP-XACT standard, an XML format for describing IP components and designs. In 2008, the VSI Alliance and the SPIRIT Consortium merged into Accellera, an industry association dedicated to creating design and verification standards. Accellera maintains and updates the IP-XACT standard.

2004 marked the release of IP-XACT 1.0 as the first version of IP-XACT. It focused on describing SIP blocks’ register-transfer level (RTL) behavior. Then, in 2005, version 1.1 added support for defining SIP block transaction-level modeling (TLM) behavior; in 2006, version 1.2 added support for describing the physical implementation of IP blocks. Version 1.4 added support for defining the verification of IP blocks in 2008. After the merger, IEEE Std. 1685-2009 was the first version of IP-XACT approved by the IEEE in 2009. IEEE Std. 1685-2014 added support for describing the security of IP blocks. Today, the latest version of IP-XACT, IEEE Std. 1685-2022, supports the definition of vendor extensions of SIP blocks.

Outlook

While the charts illustrate the trends leading up to today, 2023, both SoC designs and chiplet-based designs are only getting more complex from here. NoC protocols will become more complex, and the sea of RTL blocks to be connected is only getting more profound and extensive. Do you want to refactor the RTL manually when redefining power regions? No, you don’t! That’s where IP-XACT-based SoC integration automation comes in.

NoC SIP reuse and IP-XACT-based SoC integration automation are critical to keeping design costs in check and increasing productivity for the Golden Age of Semiconductors!

Frank Schirrmeister

(all posts)

Frank Schirrmeister is vice president of solutions and business development at Arteris. He leads activities in the automotive, data center, 5G/6G communications, mobile, aerospace and data center industry verticals and the technology horizontals artificial intelligence, machine learning, and safety. Before Arteris, Schirrmeister held various senior leadership positions at Cadence Design Systems, Synopsys, and Imperas, focusing on product marketing and management, solutions, strategic ecosystem partner initiatives and customer engagement.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Automotive / EVs, Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- ChartPrime. Elevate your Trading Game with ChartPrime. Access Here.

- BlockOffsets. Modernizing Environmental Offset Ownership. Access Here.

- Source: https://semiengineering.com/design-complexity-in-the-golden-age-of-semiconductors/

- :has

- :is

- :not

- :where

- $UP

- 1

- 1.3

- 1996

- 1999

- 2005

- 2006

- 2008

- 2009

- 2010

- 2012

- 2013

- 2016

- 2019

- 2020

- 2022

- 2023

- 50

- 50 Years

- 80

- a

- About

- above

- accelerators

- ace

- acquired

- Acronyms

- activities

- added

- advanced

- Aerospace

- After

- age

- All

- All Posts

- Alliance

- also

- an

- and

- Another

- answer

- approved

- architecture

- ARE

- AREA

- ARM

- arriving

- artificial

- artificial intelligence

- AS

- Assembly

- Association

- At

- Attempts

- Automation

- automotive

- available

- based

- BE

- become

- becomes

- before

- behavior

- below

- between

- Block

- Blocks

- both

- Bottom

- buffer

- bus

- Buses

- business

- business development

- but

- by

- cache

- Cadence

- call

- called

- CAN

- Center

- Chart

- Charts

- check

- classic

- clear

- Close

- COHERENT

- comes

- coming

- commercial

- commercially

- Communications

- community

- complex

- complexity

- components

- configured

- Connect

- connected

- Connecting

- considering

- consortium

- content

- context

- Core

- Cost

- Costs

- Creating

- critical

- customer

- Customer Engagement

- data

- Data Center

- data points

- day-to-day

- deal

- dedicated

- Defines

- defining

- definition

- described

- Design

- design systems

- designs

- develop

- developed

- Development

- device

- different

- digits

- distributed

- do

- document

- down

- Drop

- DTI

- due

- e

- each

- Earlier

- Early

- ecosystem

- enable

- enabling

- ends

- engagement

- enhance

- essential

- evolution

- expertise

- express

- extensions

- extensive

- FAST

- Features

- First

- Flash

- focused

- focusing

- For

- format

- Foundation

- Founded

- four

- frank

- Frequency

- from

- fully

- functional

- future

- getting

- Go

- Golden

- GPUs

- grew

- Group

- Growing

- grown

- had

- Have

- he

- Held

- hence

- here

- High

- high-performance

- his

- How

- HTTPS

- Hub

- i

- IEEE

- implementation

- in

- included

- increasing

- industry

- initiatives

- input

- integrated

- integration

- Intelligence

- interconnects

- Interface

- interfaces

- internally

- into

- introduced

- Introduction

- IP

- IT

- ITS

- jpg

- keeping

- latest

- Law

- Leadership

- leading

- Leads

- learning

- Legacy

- Level

- like

- Line

- LINK

- local

- Look

- looked

- Lot

- lower

- machine

- machine learning

- maintains

- make

- manage

- management

- manually

- many

- marked

- Marketing

- max-width

- me

- measured

- Memory

- Merger

- Mobile

- modeling

- more

- most

- Need

- New

- New Features

- no

- note

- now

- number

- of

- on

- only

- open

- Operations

- or

- organization

- Other

- our

- out

- outlined

- over

- page

- pages

- part

- particular

- partner

- perfect

- performance

- peripheral

- permission

- photo

- physical

- plan

- plato

- Plato Data Intelligence

- PlatoData

- Point

- points

- positions

- Posts

- power

- president

- Prior

- Processor

- processors

- Product

- productivity

- Profiles

- profound

- project

- prominent

- protocol

- protocols

- providing

- quality

- recent

- Red

- Redefining

- Refactor

- regions

- related

- release

- released

- relevant

- remember

- removing

- require

- reuse

- Richard

- right

- Safety

- Scale

- SEA

- Second

- security

- seen

- Semiconductors

- senior

- senior leadership

- service

- Shows

- significantly

- Silicon

- single

- sit

- So

- Solutions

- some

- Source

- specification

- specs

- spirit

- standard

- standards

- Still

- Strategic

- such

- support

- Supports

- system

- Systems

- Talk

- Technology

- term

- thanks

- that

- The

- The Area

- the security

- then

- There.

- These

- they

- Third

- this

- three

- thumbnail

- time

- timeline

- timelines

- TLM

- to

- today

- too

- Total

- traffic

- Translation

- Trend

- Trends

- two

- types

- typical

- unit

- Updates

- used

- using

- various

- vendor

- Verification

- version

- versions

- verticals

- vice

- Vice President

- wait

- want

- was

- Way..

- we

- webp

- What

- when

- which

- Wikipedia

- will

- with

- without

- working

- world

- would

- writing

- XML

- years

- yes

- you

- Your

- zephyrnet