Many SoC and ASIC manufacturers rely heavily on cryptographic solutions to safeguard sensitive IP and data transmission within their devices. In a dynamic landscape where threats from attackers continue to evolve, encryption algorithms play a crucial role in fortifying defenses. Hackers today are leveraging advanced physical tactics that extend beyond traditional data interception, posing significant risks beyond mere ransomware payments. The stakes are high, encompassing the potential loss of intellectual property and integrity of the device.

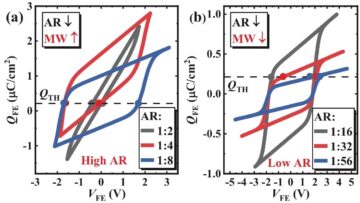

Security solutions rely on cryptographic algorithms that combine data with a randomly generated key. These procedures emit a physical byproduct known as leakage, which can manifest in various forms such as slight power variations and electromagnetic radiations. Hackers have developed sophisticated methods using sniffing equipment to extract these secrets.

Moreover, understanding the system clock enables hackers to conduct power monitoring attacks like differential power analysis. By monitoring subtle power supply fluctuations, attackers can detect logic states.

The realm of physical hacking techniques extends beyond timing and power monitoring attacks. It includes a spectrum of methods like electromagnetic, optical, and thermal cryptanalysis. The sophistication and variety of these techniques highlight the critical need for robust cybersecurity measures.

Manufacturers are constantly enhancing their security measures to combat vulnerabilities. Techniques like shielded packages and isochronous circuitry have been deployed, but adversaries can still find ways to breach defenses. Masking and shuffling emerge as two promising countermeasures to strengthen security against such threats.

Masking schemes play a vital role in protecting against Side-Channel Attacks (SCAs) by concealing statistical dependencies within data. One common approach involves using Boolean masking (exclusive-or) to hide these patterns, known as first-order masking. But did you know there are multiple orders of masking? Each order enhances security levels. Second-order masking is highly regarded for secure implementations of various cryptographic primitives like Keccak, SKINNY, Midori, PRESENT, and PRINCE.

Shuffling schemes play a crucial role in safeguarding the Gaussian sampling component. By rearranging the order of operations, they effectively reduce the correlation between operations and power consumption. One prevalent algorithm used for shuffling is the Fisher-Yates shuffle, known for generating unbiased permutations of the output.

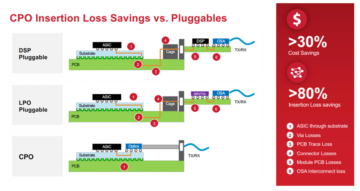

Implementing masking and shuffling schemes in FPGA IP holds significant value for multiple reasons. Firstly, these techniques, like most cryptography algorithms, continue to evolve, ensuring enhanced security measures. Secondly, FPGA IP empowers designers to adjust the order of masking or shuffling based on specific security needs. Additionally, FPGA IP introduces variability to each of these security measures, leveraging randomness inherent in FPGA logic implementations, such as LUT-combining and retiming. Moreover, embedded FPGA (eFPGA) IP, exemplified by Flex Logix’s EFLX IP, operates glitch-free and asynchronously, presenting challenges for cryptanalysis.

To learn more about implementations of using these techniques on FPGAs, read this paper on Security Aspects of Masking on FPGAs. It also introduces tools to formally verify any-order masked hardware implementations directly on FPGA netlists.

To make implementation of cryptography algorithms easier, companies are innovating and building SCA-resistant IP. Take for instance, PQsecure’s library of IP cores. Reza Azarderakhsh, PhD, CEO of PQsecure, illustrates the value of this IP in eFPGA IP. “The severity of side-channel attacks necessitates using countermeasures such as masking and hiding. For example, many masking schemes continue to be developed and masking can be implemented at several orders of security. Since side-channel countermeasures research is a fast-moving field, the ability to update these countermeasures after deploying cryptographic devices in the field is extremely desirable. FPGAs are suitable to satisfy this goal of flexibility while providing superior performance and energy consumption compared to software implementation.”

Customizable for the perfect solution

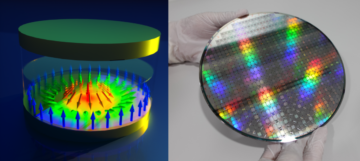

Exciting news for semiconductor designers! Flex Logix’s eFPGA IP, EFLX, seamlessly integrates into any SoC or ASIC. Offering top-notch power, performance, and area (PPA) metrics, EFLX is compatible with cutting-edge nodes like Intel 18A, TSMC 7nm, and 5nm. The scalability of Flex Logix eFPGA IP empowers users to optimize their resources effectively for enhanced flexibility.

Scalable Flex Logix eFPGA IP.

Yes, there is a cost to implement robust SoC security. But it is far cheaper to protect your data and IP than have it stolen by malicious hackers. eFPGA IP enables flexibility to adapt to new cryptography algorithms and SCA countermeasure schemes. This hardware not only accelerates these functions but also enables rolling cryptography, obfuscation and asynchronous controls. Adding only a couple hundred of logic cells can dramatically enhance security and this consumes only 0.04mm2 of die area at TSMC’s 5nm node.

What’s next? Hybrid solutions will emerge where software and hardware work together to provide optimized, flexible and cost-sensitive solutions. See section 1.5 USA’s National Strategy on Microelectronics Research. Here are a couple of quotes from the article:

“In recent years, cybersecurity threats have evolved from attacks focused high in the software stack to progressively lower levels of the computational hierarchy, down to the chip level.”

“Co-design of hardware with software is needed to meet these challenges in ways that provide maximum protection while minimizing the impact on system performance.”

Want to learn more about Flex Logix IP? Contact us at [email protected] or visit our website https://flex-logix.com.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiengineering.com/secure-your-soc-from-side-channel-attacks-with-adaptable-security/

- :is

- :not

- :where

- 1

- 200

- 5

- a

- ability

- About

- accelerates

- adapt

- adaptable

- adding

- Additionally

- adjust

- advanced

- After

- against

- algorithm

- algorithms

- also

- alt

- analysis

- and

- any

- approach

- ARE

- AREA

- article

- AS

- asic

- aspects

- At

- attackers

- Attacks

- based

- BE

- been

- between

- Beyond

- breach

- Building

- but

- by

- CAN

- Cells

- ceo

- challenges

- Channel

- cheaper

- chip

- Clock

- COM

- combat

- combine

- Common

- Companies

- compared

- compatible

- component

- computational

- Conduct

- constantly

- consumption

- contact

- continue

- controls

- Correlation

- Cost

- Couple

- critical

- crucial

- cryptographic

- cryptography

- cutting-edge

- Cybersecurity

- data

- defenses

- dependencies

- deployed

- deploying

- designers

- detect

- developed

- device

- Devices

- DID

- Die

- directly

- down

- dramatically

- dynamic

- each

- easier

- effectively

- embedded

- emerge

- empowers

- enables

- encompassing

- encryption

- energy

- Energy Consumption

- enhance

- enhanced

- Enhances

- enhancing

- ensuring

- equipment

- evolve

- evolved

- example

- exemplified

- extend

- extends

- extract

- extremely

- far

- fast-moving

- field

- Find

- firstly

- Flexibility

- flexible

- fluctuations

- focused

- For

- Formally

- forms

- fpga

- from

- functions

- generated

- generating

- goal

- hackers

- hacking

- Hardware

- Have

- heavily

- here

- Hide

- hiding

- hierarchy

- High

- Highlight

- highly

- holds

- HTTPS

- hundred

- Hybrid

- illustrates

- Impact

- implement

- implementation

- implementations

- implemented

- in

- includes

- inherent

- innovating

- instance

- Integrates

- integrity

- Intel

- intellectual

- intellectual property

- into

- Introduces

- involves

- IP

- IT

- Key

- Know

- known

- landscape

- leakage

- LEARN

- Level

- levels

- leveraging

- Library

- like

- logic

- loss

- lower

- make

- malicious

- Manufacturers

- many

- max-width

- maximum

- measures

- Meet

- mere

- methods

- Metrics

- minimizing

- monitoring

- more

- Moreover

- most

- multiple

- National

- necessitates

- Need

- needed

- needs

- New

- news

- next

- node

- nodes

- of

- offering

- on

- ONE

- only

- operates

- Operations

- optical

- Optimize

- optimized

- or

- order

- orders

- our

- output

- packages

- Paper

- patterns

- payments

- perfect

- performance

- phd

- physical

- plato

- Plato Data Intelligence

- PlatoData

- Play

- posing

- potential

- power

- Power Supply

- present

- presenting

- prevalent

- primitives

- Prince

- procedures

- progressively

- promising

- property

- protect

- protected

- protecting

- protection

- provide

- providing

- quotes

- randomly generated

- randomness

- ransomware

- Read

- realm

- reasons

- recent

- reduce

- regarded

- rely

- research

- Resources

- risks

- robust

- Role

- Rolling

- safeguard

- safeguarding

- satisfy

- Scalability

- schemes

- seamlessly

- secrets

- Section

- secure

- security

- security measures

- see

- semiconductor

- sensitive

- several

- severity

- side

- significant

- since

- slight

- Software

- Solutions

- sophisticated

- sophistication

- specific

- Spectrum

- stack

- stakes

- States

- statistical

- Still

- stolen

- Strategy

- Strengthen

- subtle

- such

- suitable

- superior

- supply

- system

- tactics

- Take

- techniques

- than

- that

- The

- their

- There.

- thermal

- These

- they

- this

- threats

- timing

- to

- today

- together

- tools

- top-notch

- traditional

- transmission

- Tsmc

- two

- unbiased

- understanding

- Update

- us

- used

- users

- using

- value

- variations

- variety

- various

- verify

- Visit

- vital

- Vulnerabilities

- ways

- webp

- Website

- which

- while

- Wikipedia

- will

- with

- within

- Work

- work together

- years

- you

- Your

- zephyrnet